## **LXT6155**

#### 155 Mbps SDH/SONET/ATM Transceiver

#### **Datasheet**

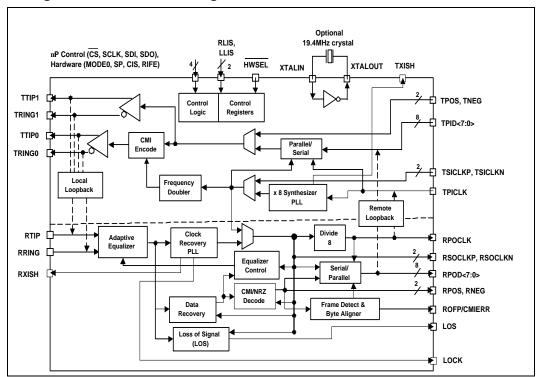

The LXT6155 is a high speed fully integrated transceiver designed for 155 Mbps SDH/SONET/ ATM transmission system applications. The LXT6155 provides a LVPECL interface for fiber optics modules, and a CMI interface for coax cable drive. These circuits are implemented using Level One's proven low power 3.3V CMOS analog and digital circuits.

The transmitter incorporates a parallel-to-serial converter, a frequency multiplier PLL, CMI line encoders, and line interfaces for both coax cable and optical fiber. The receiver incorporates an adaptive equalizer, a clock recovery PLL, Loss of Signal (LOS) detector, CMI and NRZ decoders, a serial-to-parallel converter, and an SDH/SONET frame byte detector/aligner. At the system interface, the LXT6155 offers both parallel 8-bit and serial differential interfaces. The LXT6155 also operates in either Hardware stand-alone mode or Software mode. Software mode is controlled by a serial microprocessor ( $\mu$ P) to program formats and operating/test modes.

#### **Product Features**

#### **Applications**

- OC3/STM1 SDH/SONET Cross Connects

- OC3/STM1 SDH/SONET Add/Drop Mux

- OC3/STM1 Transmission Systems

- OC3/STM1 Short Haul Serial Links

- OC3/STM1 ATM/WAN Transmission Systems

- OC3/STM1 ATM/WAN Access Systems

#### **Features**

- Complies with:

- —Bellcore SONET GR-253

- -- ITU-T G.703/813/958 STM1

- Two line interface formats:

- —Fiber LVPECL NRZ

- —Coax CMI

- Transmit synthesizer PLL

- Receive clock recovery PLL

- Adaptive CMI equalizer

- Analog circuitry for transformer drive

- Programmable LOS function

- CMI encoder and decoder

- Serial/Parallel and Parallel/Serial conversion

- Byte alignment for SDH/SONET frames

- Two modes of operation:

- Microprocessor controlled; software mode

- -Stand-alone; hardware mode

- No external crystal required. A 19.44 MHz crystal is optional

- Low power consumption (less than 760 mW typical)

- Operates from a single 3.3 V supply

- 64 pin LQFP package

Order Number: 249612-001 January 2001

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The NAME OF PRODUCT may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Pin / | Assignr   | ments and Signal Descriptions                         | 8  |

|-----|-------|-----------|-------------------------------------------------------|----|

| 2.0 | Fund  | ctional l | Description                                           | 13 |

|     | 2.1   |           | nitter                                                |    |

|     | 2.1   | 2.1.1     | Transmitted Signal                                    |    |

|     |       | 2.1.1     | 2.1.1.1 Fiber Based G.957/GR-253 Transmission Systems |    |

|     |       | 2.1.2     | Coax Based G.703/GR-253 Transmission Systems          |    |

|     |       | 2.1.2     | 2.1.2.1 CMI Encoding                                  |    |

|     |       | 2.1.3     | Tx Clock Monitoring                                   |    |

|     | 2.2   |           | /er                                                   |    |

|     | 2.2   | 2.2.1     | Analog Front End and Timing Recovery                  |    |

|     |       | ۷.۷.۱     | 2.2.1.1 CMI Mode                                      |    |

|     |       |           | 2.2.1.2 NRZ Mode                                      |    |

|     |       | 2.2.2     | Receive Frame Detect and Byte Alignment               |    |

|     |       | 2.2.2     | 2.2.2.1 Loss of Signal (LOS)                          |    |

|     |       |           | 2.2.2.2 Coax Interface                                |    |

|     |       |           | 2.2.2.3 Fiber Interface                               |    |

|     | 2.3   | Clocks    |                                                       |    |

|     |       | 2.3.1     | Parallel Mode                                         |    |

|     |       |           | 2.3.1.1 Transmit Parallel Input Clock (TPICLK)        |    |

|     |       |           | 2.3.1.2 Receive Parallel Output Clock (RPOCLK)        | 18 |

|     |       | 2.3.2     | Serial Mode                                           |    |

|     |       |           | 2.3.2.1 Transmit Serial Input Clock (TSICLKP/TSICLKN) |    |

|     |       |           | 2.3.2.2 Receive Serial Output Clock (RSOCLKP/RSOCLKN) |    |

|     |       | 2.3.3     | Crystal Reference Clock (XTALIN/XTALOUT)              |    |

|     | 2.4   | Jitter    |                                                       |    |

|     |       | 2.4.1     | Jitter Tolerance                                      | 19 |

|     |       | 2.4.2     | Jitter Generation (Intrinsic Jitter)                  | 19 |

|     |       | 2.4.3     | Jitter Transfer                                       |    |

|     | 2.5   | Operat    | tional Modes                                          | 19 |

|     |       | 2.5.1     | Hardware Mode                                         |    |

|     |       |           | 2.5.1.1 PLL Clock Reference (CIS pin)                 | 20 |

|     |       |           | 2.5.1.2 Loopback Test (RLIS and LLIS pins)            | 21 |

|     |       |           | 2.5.1.3 Line Interface Selection (MODE Pin)           | 21 |

|     |       |           | 2.5.1.4 Parallel/Serial Mode Selection (SP pin)       | 21 |

|     |       |           | 2.5.1.5 Tx Amplitude Trim                             |    |

|     |       | 2.5.2     | Software Mode                                         |    |

|     |       |           | 2.5.2.1 Serial Input Clock (SCLK)                     |    |

|     |       |           | 2.5.2.2 Chip Select Input (CS)                        |    |

|     |       |           | 2.5.2.3 Serial Input Word (SDI)                       |    |

|     | 0.0   | 0         | 2.5.2.4 Serial Output Word (SDO)                      |    |

|     | 2.6   |           | System Interface                                      |    |

|     | 2.7   |           | el System Interface                                   |    |

|     | 2.8   | •         | ack Modes                                             |    |

|     |       | 2.8.1     | Local Loopback                                        |    |

|     |       | 2.8.2     | Remote Loopback                                       | 25 |

## LXT6155 — 155 Mbps SDH/SONET/ATM Transceiver

| 3.0     | Reg      | ister Definitions                                                         | 26 |

|---------|----------|---------------------------------------------------------------------------|----|

| 4.0     | App      | lication Information                                                      | 33 |

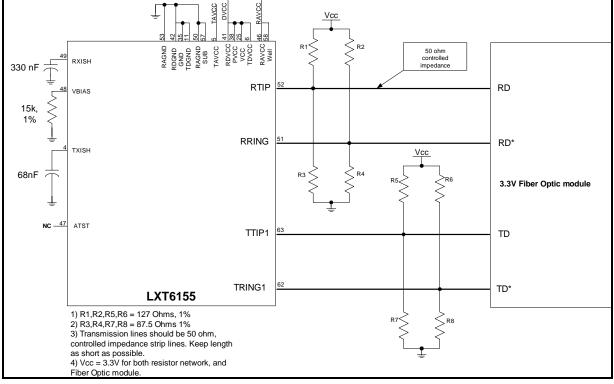

|         | 4.1      | Fiber Optic Module Interface                                              | 33 |

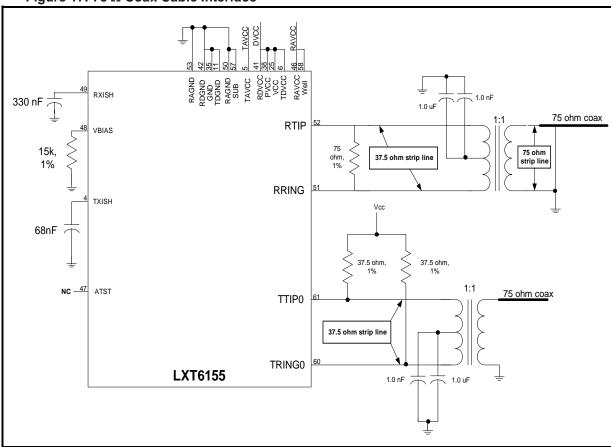

|         | 4.2      | Coax Interface                                                            |    |

| 5.0     | Test     | t Specifications                                                          |    |

| 6.0     |          | chanical Specifications                                                   |    |

|         |          | -                                                                         |    |

| 7.0     | Note     | es                                                                        | 49 |

| Figures |          |                                                                           |    |

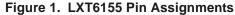

| •       | 1        | LXT6155 Pin Assignments                                                   | 8  |

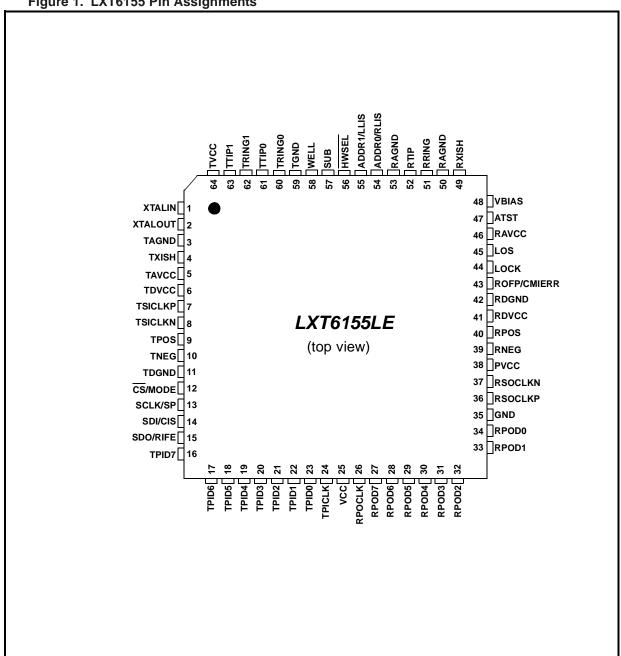

|         | 2        | LXT6155 System Interface                                                  |    |

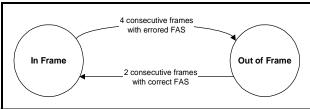

|         | 3        | Framing State                                                             | 16 |

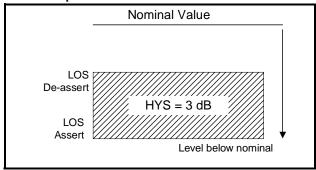

|         | 4        | Criteria for LOS Output                                                   |    |

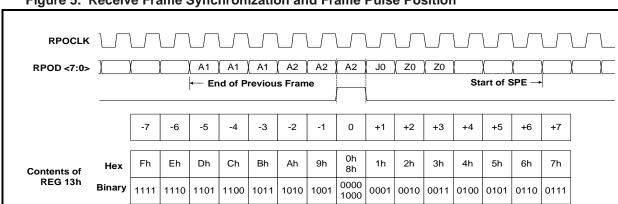

|         | 5        | Receive Frame Synchronization and Frame Pulse Position                    | 17 |

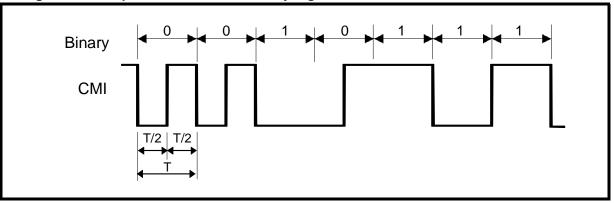

|         | 6        | Example of CMI Encoded Binary Signal                                      |    |

|         | 7        | Hardware Mode                                                             |    |

|         | 8        | Software Mode                                                             |    |

|         | 9        | Serial Data Output Word Structure (Read Cycle: R/W=High)                  |    |

|         | 10       | Serial Data Input Word Structure (Write Cycle: R/W = Low)                 |    |

|         | 11       | Serial Interface                                                          |    |

|         | 12       | Parallel Interface                                                        |    |

|         | 13       | Local Loopback                                                            |    |

|         | 14       | Remote Loopback                                                           |    |

|         | 15       | Rx Digital 2, Register #13 (Address A<3:0>=11001)                         |    |

|         | 16       | 3.3 V LVPECL to 3.3 V LVPECL Interface                                    |    |

|         | 17       | 75 W Coax Cable Interface                                                 |    |

|         | 18       | Transmit Parallel Input Data Timing (See Table 28)                        |    |

|         | 19       | Transmit Serial Input Data Timing (See Table 28)                          |    |

|         | 20       | Receive Serial Output Data Timing (See Table 30)                          |    |

|         | 21<br>22 | Microprocessor Input Timing Diagram                                       |    |

|         | 23       | · · · · · · · · · · · · · · · · · · ·                                     |    |

|         | 23<br>24 | Microprocessor Output Timing Diagram CMI Encoded Zero per G.703 and STS-3 |    |

|         | 24<br>25 | CMI Encoded One per G.703 and STS-3                                       |    |

|         | 25<br>26 | Jitter Tolerance                                                          |    |

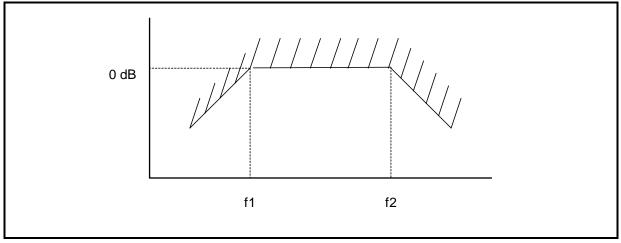

|         | 20<br>27 | Generation Measurement Filter Characteristics                             |    |

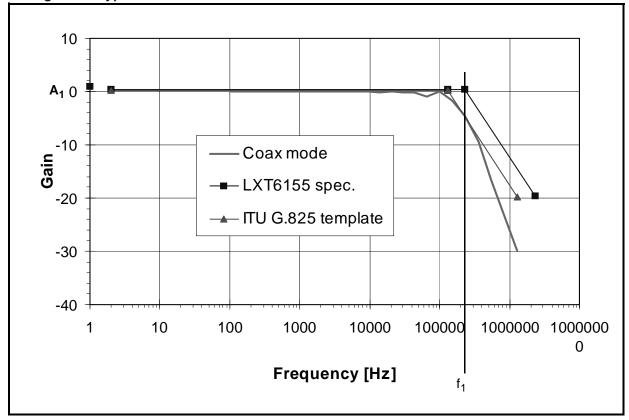

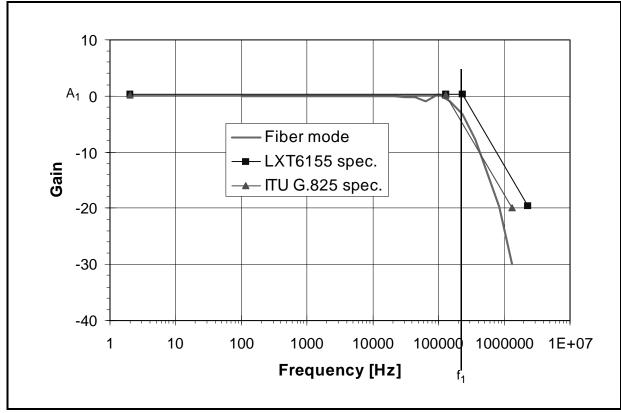

|         | 28       | Typical Coax Jitter Transfer                                              |    |

|         | 29       | Typical Fiber Jitter Transfer                                             |    |

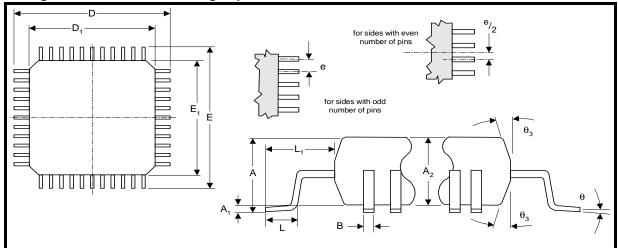

|         | 30       | I XT6155I F Package Specification                                         | 48 |

# Revision History

Figure 1. LXT6155 Block Diagram

#### **Pin Assignments and Signal Descriptions** 1.0

Table 1. LXT6155 Pin Descriptions

| Pin # | Symbol   | I/O <sup>1</sup> | Type <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|----------|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | XTALIN   | AI/O             |                   | Crystal Input/Output. These pins are connected to an external 19.44                                                                                                                                                                                                                                                                                                                                           |

| 2     | XTALOUT  |                  |                   | MHz crystal. Alternately, a stable external clock signal may be connected to XTALIN with XTALOUT left open. XTALIN should be connected to TAGND and XTALOUT should be left open if the transmit input clock is used as a clock reference                                                                                                                                                                      |

| 3     | TAGND    | S                |                   | Transmit Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                       |

| 4     | TXISH    | AI/O             |                   | <b>Transmit PLL Loop Filter Pin.</b> Connecting a capacitor to TAGND from this pin controls the Tx PLL transfer function. This pin requires a 68nF cap to TAGND.                                                                                                                                                                                                                                              |

| 5     | TAVCC    | S                |                   | Transmit Analog Power Supply.                                                                                                                                                                                                                                                                                                                                                                                 |

| 6     | TDVCC    | S                |                   | Transmit Digital Power Supply.                                                                                                                                                                                                                                                                                                                                                                                |

| 7     | TSICLKP  | DI               | LVPECL            | Transmit Serial Input Clock, positive and negative. Differential                                                                                                                                                                                                                                                                                                                                              |

| 8     | TSICLKN  |                  |                   | Transmit clocks at 155.52 MHz. These pins are disabled when parallel mode is selected.                                                                                                                                                                                                                                                                                                                        |

| 9     | TPOS     | DI               | LVPECL            | Transmit Serial Input Data, positive and negative. Differential input                                                                                                                                                                                                                                                                                                                                         |

| 10    | TNEG     |                  |                   | data from an overhead terminator at 155.52 Mbps, clocked in by TSICLK. These pins are disabled when parallel mode is selected.                                                                                                                                                                                                                                                                                |

| 11    | TDGND    | S                |                   | Transmit Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                      |

| 12    | CS/MODE  | DI               | TTL               | Chip Select Input, software mode ( $\overline{HWSEL}$ = High). Register transactions through the $\mu P$ interface are initiated by the falling edge of this signal.                                                                                                                                                                                                                                          |

|       |          |                  |                   | Line Interface Mode, hardware mode (HWSEL = Low). Sets line interface mode to LVPECL (MODE = Low) or CMI (MODE = High).                                                                                                                                                                                                                                                                                       |

| 13    | SCLK/SP  | DI               | TTL               | Serial Clock Input, software mode (HWSEL = High). Serial Microprocessor uses this pin to clock in/out data. SCLK can be from 0 to 4.096 MHz.                                                                                                                                                                                                                                                                  |

|       |          |                  |                   | Serial/Parallel Select, hardware mode (HWSEL = Low). When SP = Low, serial systems interface is used. When SP = High, 8 bit parallel system interface is used.                                                                                                                                                                                                                                                |

| 14    | SDI/CIS  | DI               | TTL               | Serial Input Data, software mode (HWSEL = High). The serial data is applied to this pin when the LXT6155 operates in software mode. SDI is sampled on the rising edge of SCLK.                                                                                                                                                                                                                                |

|       |          |                  |                   | Clock Input Select, hardware mode (HWSEL = Low). CIS sets the reference clock for centering the Rx PLL. If CIS = Low, then the LXT6155 uses the transmit input clock as the reference. If CIS = High, then the LXT6155 uses the crystal clock input (XTALIN) as the reference.                                                                                                                                |

| 15    | SDO/RIFE | DI/O             | TTL               | Serial Output Data, software mode (HWSEL = High). The serial data from the on-chip register is output on this in software mode. Data output is valid on the rising edge of SCLK. This pin goes to a high impedance state when the serial port is being written to or when CS is High.                                                                                                                         |

|       |          |                  |                   | Receive Input Frame Enabler, hardware mode (HWSEL = Low). The frame detection option is available only in parallel mode. If RIFE = Low, then the LXT6155 disables the frame detection, and byte alignment. If RIFE = High, then the LXT6155 enables the frame detection, and outputs RPOD bytes aligned to the SONET/SDH framer. This feature, if used, must be enabled prior to applying data to Rtip/Rring. |

DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; AI/O = Analog Input/Output; S=Supply.

TTL = Transistor-to-Transistor Logic (5V tolerant); LVPECL = Low-Voltage positive ECL.

Table 1. LXT6155 Pin Descriptions (Continued)

| Pin #                                        | Symbol                                                               | I/O <sup>1</sup>               | Type <sup>2</sup>              | Description                                                                                                                                                                                                                                                                            |        |     |                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|----------------------------------------------------------------------|--------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16<br>17<br>18<br>19                         | TPID7/TXTRIM3 DI TPID6/TXTRIM2 TPID5/TXTRIM1 TPID4/TXTRIM0           | TPID6/TXTRIM2<br>TPID5/TXTRIM1 | TPID6/TXTRIM2<br>TPID5/TXTRIM1 | ID6/TXTRIM2<br>ID5/TXTRIM1                                                                                                                                                                                                                                                             | DI TTL | TTL | Transmit Parallel Input Data. Transmit data from an Overhead Terminator at parallel speed 19.44 MHz, clocked in by TPICLK. TPID7 is the most significant bit, and is the first bit to be sent. These pins should be grounded or not connected when the LXT6155 is used in serial mode. |

|                                              |                                                                      |                                |                                | Transmit Trim Controls, in serial, hardware, coax mode only. These pins trim the amplitude of the line driver output from (nom -21%) to (nom +24%) in 3% steps. This feature is only enabled when pin #20 (TXTRIMENA) is High.                                                         |        |     |                                                                                                                                                                                                                                                                                        |

| 20                                           | TPID3/TXTRIMENA                                                      | DI                             | TTL                            | Transmit Parallel Input Data. Transmit data from an Overhead Terminator at parallel speed 19.44 MHz, clocked in by TPICLK. TPID7 is the most significant bit, and is the first bit to be sent. These pins should be grounded or not connected when the LXT6155 is used in serial mode. |        |     |                                                                                                                                                                                                                                                                                        |

|                                              |                                                                      |                                |                                | <b>Transmit Trim Enable</b> , in serial, hardware, coax mode only. This pin enables the trimming of the line driver output by pins 16-19 when high.                                                                                                                                    |        |     |                                                                                                                                                                                                                                                                                        |

| 21<br>22<br>23                               | TPID2<br>TPID1<br>TPID0                                              | DI                             | TTL                            | Transmit Parallel Input Data. Transmit data from an Overhead Terminator at parallel speed 19.44 MHz, clocked in by TPICLK. TPID7 is the most significant bit, and is the first bit to be sent. These pins should be grounded or not connected when the LXT6155 is used in serial mode. |        |     |                                                                                                                                                                                                                                                                                        |

| 24                                           | TPICLK                                                               | DI                             | TTL                            | Transmit Parallel Input Clock. Parallel transmit clock at 19.44 MHz. This pin is disabled when serial mode is selected and should be grounded or not connected.                                                                                                                        |        |     |                                                                                                                                                                                                                                                                                        |

| 25                                           | VCC                                                                  | S                              |                                | Power Supply.                                                                                                                                                                                                                                                                          |        |     |                                                                                                                                                                                                                                                                                        |

| 26                                           | RPOCLK                                                               | DO                             | TTL                            | Receive Parallel Output Clock. Parallel receive clock as recovered from received data. The clock is nominally 19.44 MHz, synchronized with RPOD<7:0>.                                                                                                                                  |        |     |                                                                                                                                                                                                                                                                                        |

| 27<br>28<br>29<br>30<br>31<br>32<br>33<br>34 | RPOD7<br>RPOD6<br>RPOD5<br>RPOD4<br>RPOD3<br>RPOD2<br>RPOD1<br>RPOD0 | DO                             | TTL                            | Receive Parallel Output Data. RPOD<7:0> output aligned 8-bit bytes at RPOCLK clock rate. These pins are to be left open when serial mode is selected. RPOD7 is the most significant bit, and is the first to arrive.                                                                   |        |     |                                                                                                                                                                                                                                                                                        |

| 35                                           | GND                                                                  | S                              |                                | Ground.                                                                                                                                                                                                                                                                                |        |     |                                                                                                                                                                                                                                                                                        |

| 36                                           | RSOCLKP                                                              | DO                             | LVPECL                         | Receive Serial Output Clock. Serial receive clock as recovered from                                                                                                                                                                                                                    |        |     |                                                                                                                                                                                                                                                                                        |

| 37                                           | RSOCLKN                                                              |                                |                                | received data. The clock is nominally 155.52 MHz, synchronized with output serial data RPOS and RNEG.                                                                                                                                                                                  |        |     |                                                                                                                                                                                                                                                                                        |

| 38                                           | PVCC                                                                 | S                              |                                | PECL Buffers Power Supply.                                                                                                                                                                                                                                                             |        |     |                                                                                                                                                                                                                                                                                        |

| 39                                           | RNEG                                                                 | DO                             | LVPECL                         | Receive Serial Output Data, positive and negative. These two pins                                                                                                                                                                                                                      |        |     |                                                                                                                                                                                                                                                                                        |

| 40                                           | RPOS                                                                 |                                |                                | provide recovered data synchronized to receive serial output clocks RSOCLKP and RSOCLKN. These pins are tristated and should be left open when parallel mode is selected.                                                                                                              |        |     |                                                                                                                                                                                                                                                                                        |

| 41                                           | RDVCC                                                                | S                              |                                | Receive Digital Power Supply.                                                                                                                                                                                                                                                          |        |     |                                                                                                                                                                                                                                                                                        |

| 42                                           | RDGND                                                                | S                              |                                | Receive Digital Ground.                                                                                                                                                                                                                                                                |        |     |                                                                                                                                                                                                                                                                                        |

DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; AI/O = Analog Input/Output; S=Supply.

TTL = Transistor-to-Transistor Logic (5V tolerant); LVPECL = Low-Voltage positive ECL.

Table 1. LXT6155 Pin Descriptions (Continued)

| Pin #    | Symbol          | I/O <sup>1</sup> | Type <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

|----------|-----------------|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 43       | ROFP/<br>CMIERR | DO               | ΠL                | Receive Output Frame Pulse. In hardware mode (HWSEL = Low), this pin is asserted (High) on the last A2 byte in the (A1A1, A2A2) sequence in the RPOD<7:0> traffic. A1=1111,0110 and A2=0010,1000 in binary. In software mode (HWSEL = High), this position is programmable. During coax operation, when frame detection is disabled (RIFE = 0 in HW/Reg #12, bit3 = 0), or in serial mode, this pin indicates CMI line code errors. These pulses are 50 ns wide (active high). One or more errors in 16 consecutive bits will causes a single pulse. |                                                                                                 |

| 44       | LOCK            | DO               | TTL               | Receive Output PLL Lock. A High indicates receive PLL has locked to incoming data. A Low indicates receive PLL is not locked.                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                 |

| 45       | LOS             | DO               | TTL               | Loss of Signal. An alarm output signal (high) indicating incoming signal voltage is weak or incoming data does not contain enough transitions. In software mode (HWSEL = 1) this pin can be configured to combine LOS and LOCK alarms.                                                                                                                                                                                                                                                                                                               |                                                                                                 |

| 46       | RAVCC           | S                |                   | Receive Analog Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |

| 47       | ATST            | -                |                   | Analog Test. For factory test purposes only; do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |

| 48       | VBIAS           | AI               | Analog            | <b>Bias Input Voltage.</b> This pin requires a 15K (1%) pull-down resistor to RAGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

| 49       | RXISH           | A0               | Analog            | <b>Rx PLL External Cap.</b> Connecting a capacitor to RAGND from this pin controls the Rx PLL transfer function. This pin requires a 330nF cap to RAGND.                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                 |

| 50       | RAGND           | S                |                   | Receive Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                 |

| 51<br>52 | RRING<br>RTIP   | AI               | Analog            | Receive Input Data, positive (RTIP) and negative (RRING). Accepts incoming signals (LVPECL or CMI) from the line interface.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

| 53       | RAGND           | S                |                   | Receive Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                 |

| 54       | ADDR0/RLIS      | DI               | TTL               | Address 0, software mode (HWSEL = High). This pin together with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

| 54       |                 |                  |                   | DI TIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADDR1 sets the chip select address. Up to 4 LXT6155 chips can be addressed by the μP interface. |

|          |                 |                  |                   | Remote Loopback Input Select, hardware mode (HWSEL = Low). Together with LLIS sets LXT6155 in a loopback test mode. See Table 4                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

| 55       | ADDR1/LLIS      | DI               | TTL               | Address 1, software mode ( $\overline{\text{HWSEL}}$ = High). This pin together with ADDR0 sets the chip select address. Up to 4 LXT6155 chips can be addressed by the $\mu P$ interface.                                                                                                                                                                                                                                                                                                                                                            |                                                                                                 |

|          |                 |                  |                   | Local Loopback Input Select, hardware mode (HWSEL = Low). Together with RLIS sets the LXT6155 in remote loopback mode. See Table 4                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                 |

| 56       | HWSEL           | DI               | TTL               | Hardware/Software Mode Select. When HWSEL = High, LXT6155 enters software (host) mode, and is ready to communicate with a serial microprocessor. When HWSEL = Low, LXT6155 operates in hardware standalone mode (without a serial μP).                                                                                                                                                                                                                                                                                                               |                                                                                                 |

| 57       | SUB             | S                |                   | Reserved. Must be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                 |

| 58       | WELL            | S                |                   | Reserved. Must be connected to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                 |

| 59       | TGND            | S                |                   | Transmit Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

| 60       | TRING0          | AO               |                   | Transmit Output Data, positive (TTIP0) and negative (TRING0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                 |

| 61       | TTIP0           |                  |                   | Differential CMI driver outputs for coax interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                 |

<sup>1.</sup> DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; AI/O = Analog Input/Output; S=Supply.

2. TTL = Transistor-to-Transistor Logic (5V tolerant); LVPECL = Low-Voltage positive ECL.

Table 1. LXT6155 Pin Descriptions (Continued)

| Pin# | Symbol | I/O <sup>1</sup> | Type <sup>2</sup> | Description                                                           |

|------|--------|------------------|-------------------|-----------------------------------------------------------------------|

| 62   | TRING1 | DO               |                   | Transmit Output Data, positive (TTIP1) and negative (TRING1).         |

| 63   | TTIP1  |                  |                   | Differential LVPECL NRZ driver outputs for a fiber optic transceiver. |

| 64   | TVCC   | S                |                   | Transmit Analog Power Supply.                                         |

<sup>1.</sup> DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; AI/O = Analog Input/Output; S=Supply.

2. TTL = Transistor-to-Transistor Logic (5V tolerant); LVPECL = Low-Voltage positive ECL.

## 2.0 Functional Description

The LXT6155 is a front-end transceiver designed for 155 Mbps OC3/STM1/ATM transmission applications. Table 2 lists the standards with which the LXT6155 is compliant.

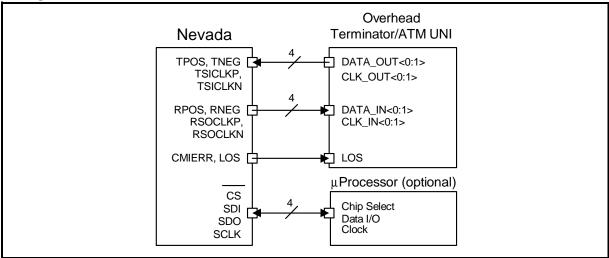

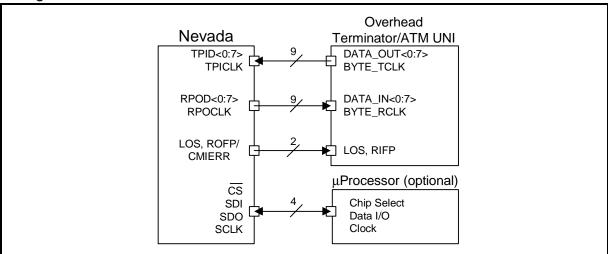

The LXT6155 interfaces to either a fiber transceiver or a coax cable on the line side, and on the system side, to an SDH/SONET Overhead Terminator or an ATM UNI. The LXT6155 can function in Hardware stand-alone mode, or in Software mode controlled through an industry standard Motorola compatible 4-wire serial microprocessor interface.

The LXT6155 can be set to operate in either CMI mode for the  $75\Omega$  coax interface or NRZ mode for the optical transceiver interface. The operating mode can be set in either hardware mode by using the MODE pin, or software mode by using Primary Control Register, bit 0.

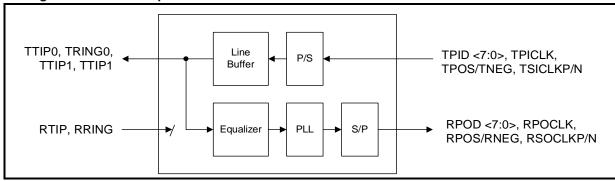

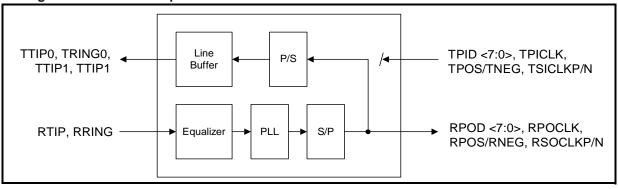

#### 2.1 Transmitter

In serial mode, the LXT6155 accepts both data (TPOS, TNEG) and clock signals (TSICLKP, TSICLKN). Serial clock signals are required for the LXT6155 to run internal logic, reshape the line transmit pulses and generate the low-jitter clocks for Tx data generation.

In parallel mode, the LXT6155 accepts data TPID<7:0> and clock TPICLK. TPICLK is internally multiplied by 8 to yield the 155.52 MHz clock for Tx data generation.

Both serial and parallel clocks (TSICLKP/TSICLKN and TPICLK) must conform to the SONET/SDH standard frequency accuracy requirements.

Depending on whether the selected media interface is coax or fiber, the data is CMI or NRZ encoded respectively, and passed to the appropriate line drivers. The LXT6155 line drivers are high-speed buffers that meet the CMI templates and industry standard LVPECL signal requirements. The CMI output pins are TTIP0 and TRING0, and the NRZ LVPECL pins, TTIP1 and TRING1.

#### 2.1.1 Transmitted Signal

Transmitted signals conform to the standard templates listed in Table 2.

#### 2.1.1.1 Fiber Based G.957/GR-253 Transmission Systems

The LXT6155 provides 3.3V LVPECL compatible signals for interfacing to a fiber optic transceiver. Please refer to Application Information for interface schematics.

#### 2.1.2 Coax Based G.703/GR-253 Transmission Systems

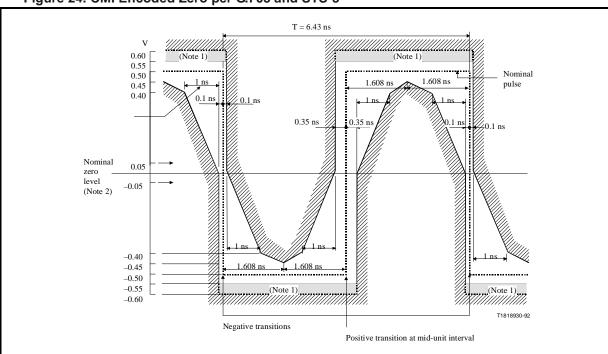

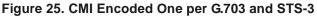

The LXT6155 encodes and decodes CMI signals that are transmitted onto a 75  $\Omega$  coax cable compliant with STM1/STS-3 CMI templates. Please refer to the CMI templates shown in Figures 24 and 25.

Figure 2. LXT6155 System Interface

#### 2.1.2.1 CMI Encoding

Coded Mark Inversion (CMI) is an encoding scheme adopted by SONET STS-3 and SDH STM1 standards. CMI encoding guarantees at least one transition per bit, thereby enhancing the clock recovery process. CMI encodes a "0" with a midpoint positive transition, and a "1" as Low or High, in opposite polarity to the previous encoded "1". Refer to Figures 6, 24 and 25 for encoding and pulse template information.

#### 2.1.3 Tx Clock Monitoring

The LXT6155 provides transmit clock monitoring for both serial and parallel operating modes. When using the crystal clock as a reference, the LXT6155 monitors the TSICLKP/TSICLKN or the TPICLK input(s) for transitions. If no transition is seen within 200ns, the tx\_clk\_alarm flag will be set (reg #15) and the transmitter outputs ttip1/tring1 or ttip0/tring0 will stop sending data to the line. This condition will remain until the LXT6155 detects clock transitions at the transmitter input(s) TSICLKP/TSICLKN or TPICLK. Transmit clock monitoring can be disabled in software mode only.

In remote loopback, transmit clock monitoring is disabled in SW and HW mode. In SW mode, when using transmit clocks as the receive PLL reference, the user must disable transmit clock monitoring by setting reg #1 bit <0> low.

### 2.2 Receiver

## 2.2.1 Analog Front End and Timing Recovery

#### 2.2.1.1 CMI Mode

Received data on RTIP/RRING goes through an adaptive equalizer. An adaptive  $\sqrt{f}$  equalizer and adaptive Automatic Gain Control (AGC) compensate the frequency-and-cable length dependent loss in data signal, and reshapes the signal to the optimal waveform. A Phase Locked Loop (PLL)

then performs clock recovery operation, comparing the reshaped data phase against the receive output clock phase. The receive PLL requires an external reference (e.g. transmit input clock or XTAL clock) to start up the clock recovery process. This clock can be derived from XTALIN, TPICLK or TSICLK (÷8). The recovered clock is used to retime the CMI signals, and to decode CMI to NRZ. Coding errors are detected and flagged via the CMIERR pin in HW mode with the frame detect disabled or in serial mode. In software mode (HWSEL = High) CMI coding errors are indicated via the  $\mu$ P interface interrupt register: Reg #15, mode 05.

#### 2.2.1.2 NRZ Mode

The on chip adaptive equalizer is bypassed. Data goes straight to the clock recovery phase locked loop. The PLL then performs clock recovery operation, comparing the data phase against the clock phase. This clock can be derived from XTALIN, TPICLK or TSICLK (÷8). The receive PLL requires an external reference (e.g. transmit input clock or XTAL clock) to start up the clock recovery process.

The recovered clock is used to retime the data signals. When the recovered clock is within 488 ppm of the reference clock, the LOCK signal asserts. This alarm is also accessible on the  $\mu P$  interface as a status bit (Reg #15, mode 0) and as an interrupt (Reg #15, mode 05). Once the recovered clock has been obtained and the NRZ data has been recovered, the LXT6155 performs frame-detect-and-byte-alignment, and serial-to-parallel conversion. The LXT6155 optionally provides output data RPOD<7:0> aligned to the SDH/SONET byte boundary. The user has the option to enable/disable the frame-alignment function in both hardware and software mode. The frame detect/byte alignment function generates the receive output frame pulse (ROFP). In HW mode (HWSEL = Low) ROFP asserts (high) on the third A2 byte. In SW mode (HWSEL = High) this position is programmable via register #13, bits <6:3>. When byte alignment is disabled and the LXT6155 is in CMI mode, the ROFP pin indicates CMI coding errors including polarity errors for ones and inversion errors for zeroes.

The clock recovery PLL's center frequency comes from either the local crystal or a stable transmit input clock (TSICLKP/TSICLKN or TPICLK). If operated in loop-timed mode or remote loopback mode, an external reference clock must be used to center the internal PLL clock. In remote loopback, the receive reference remains either XTALIN or TSICLK or TPICLK, depending on the control selection. If an independent and stable transmit clock is available, the designer has the option of applying this clock to pin XTALIN to center the PLL, without the external crystal.

The user can also replace the crystal by connecting the TPICLK (19.44MHz) signal to the XTALIN pin. However, a local crystal is recommended for "keep alive" purposes in case the clock becomes unavailable.

#### 2.2.2 Receive Frame Detect and Byte Alignment

Receive Frame Detection only operates in parallel mode, if Frame Detection is enabled. The LXT6155 provides aligned bytes RPOD<7:0> following the distinct SONET OC3/STM1 frame marker word, 3 x A1, followed by 3 x A2, where A1=F6h and A2=28h. The Receive Output Frame Pulse (ROFP) asserts during the third A2 byte, and de-asserts after one complete RPOCLK clock period. If this feature is used, it can be enabled in register #12 bit <3> in software mode  $^1$ , or by setting the RIFE (pin 15) high in hardware mode prior to applying data to Rtip/Rring. Two consecutive frames with correct frame words (A1...A1 A2...A2) are required to change from an out-of-frame state (OOF) to an in-frame state. The OOF alarm is accessible in SW mode (HWSEL = High) as a status or interrupt signal (Reg #15). To declare an OOF condition, four consecutive

<sup>1.</sup> For further details see register #12 description for usage.

frames with incorrect frame words are required. Byte alignment occurs when entering the in-frame state. In case of an OOF event, the byte alignment and frame pulse position are frozen. The ROFP output continues unchanged until re-entering the in-frame state.

Figure 3. Framing State

#### 2.2.2.1 Loss of Signal (LOS)

Loss of Signal provides an alarm signal indicating incoming signal voltage is weak or incoming data does not contain enough transitions. This signal is available in HW mode on pin #45 and in SW mode as status and interrupt (Reg #15, modes 00 and 05).

#### 2.2.2.2 Coax Interface

Loss of Signal provides an alarm output that indicates weak line input signal. The LOS signal asserts when the incoming signals fall below a specified loss threshold, and de-asserts when the line signal rises nominally 2dB above the assert threshold. The threshold is adjustable in SW mode  $(\overline{HWSEL} = High)$  via the  $\mu Processor$  interface.

#### 2.2.2.3 Fiber Interface

If no transition is detected during any 3112 bit times (20  $\mu$ sec), LOS asserts. LOS is cleared when two consecutive frame words with no LOS events between then are received. In SW mode ( $\overline{HWSEL}$  = High) the assertion window is programmable from 128 bits to 4096 bits in four steps. The deassertion criteria can also be configured to 12.5% transition density. The 12.5% density is determined by receipt of at least 4 transitions during a 32 bit sliding window.

Figure 4. Criteria for LOS Output

Figure 5. Receive Frame Synchronization and Frame Pulse Position

Table 2. Standards Compliance

| Item             | SDH/SON           | ET (Fiber)     | SDH/SONET (Coax)                  |                                    |  |

|------------------|-------------------|----------------|-----------------------------------|------------------------------------|--|

| item             | STM1              | OC3            | STM1                              | STS-3                              |  |

| Line Rate (Mbps) | 155               | 155            | 155                               | 155                                |  |

| Line Interface   | 50 Ω LVPECL       | 50 Ω LVPECL    | 75 Ω coax                         | 75 Ω coax                          |  |

| Line Code        | NRZ               | NRZ            | CMI                               | СМІ                                |  |

| Signal Templates | G.957<br>STM1 Eye | OC3<br>OC3 Eye | G.703<br>CMI Template.<br>CMI Eye | STSX-3<br>CMI Template.<br>CMI Eye |  |

| Jitter           | G.958<br>G.825    | GR-253         | G.813<br>G.825                    | GR-253                             |  |

Figure 6. Example of CMI Encoded Binary Signal

#### 2.3 Clocks

#### 2.3.1 Parallel Mode

The LXT6155 accepts TPICLK synchronized with transmit input parallel data TPID<7:0>. The data is serialized and transmitted at TTIP0/TRING0 or TTIP1/TRING1 depending on which line encoding mode is selected. The LXT6155 in turn produces the receive output parallel clock RPOCLK, that is recovered from incoming line data RTIP/RRING, and is synchronized with receive output parallel data RPOD<7:0>.

#### 2.3.1.1 Transmit Parallel Input Clock (TPICLK)

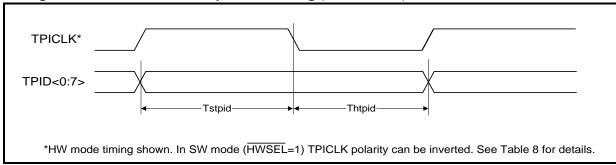

TPICLK is the transmit parallel input clock provided by the systems interface. This clock must be nominally 19.44 MHz, synchronized with parallel input data TPID<7:0>. This clock is then internally multiplied by 8 to produce a serial clock, used for parallel-to-serial conversion, line drivers, and pulse reshaping. In HW mode (HWSEL = Low), TPID data is sampled on the falling edge of TPICLK. In SW mode (HWSEL = High), the clock polarity can be inverted (Reg #0, bit #3).

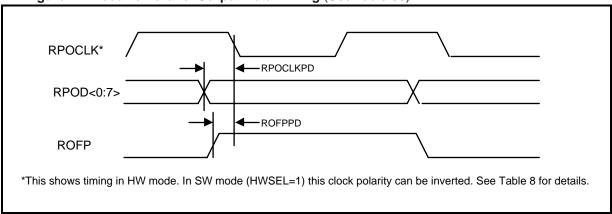

#### 2.3.1.2 Receive Parallel Output Clock (RPOCLK)

RPOCLK is the parallel output clock that is recovered from the line input data RTIP/RRING. This clock is at 19.44 MHz, synchronized with parallel output data RP0D<7:0>. In HW mode (\overline{HWSEL} = Low), the RPOCLK clock rising edge is at the center of eye opening of RPOD<7:0> as shown in Figure 21. In SW mode (\overline{HWSEL} = High), the clock polarity can be inverted (Reg #0, bit #2). Under LOS (LOS=High) or Rx PLL loss of lock (LOCK=Low) conditions RPOCLK is switched to the reference selected by the CIS control in HW mode, or Reg #0 bit #5 in SW mode. Also, the parallel output is forced to all zeros. This feature can be disabled in SW mode (\overline{HWSEL} = High) via register #10, bit #7.

#### 2.3.2 Serial Mode

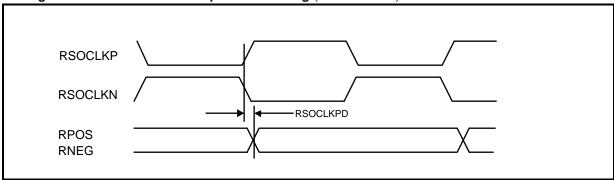

At the transmit systems interface, the LXT6155 accepts the transmit input clock TSICLKP/TSICLKN that is synchronized to incoming serial differential data TPOS/TNEG. At the line interface, the LXT6155 accepts RTIP/RRING data and produces the clocks RSOCLKP/RSOCLKN synchronized to receive output data RPOS/RNEG. RSOCLKP/RSOCLKN clock edges are at the center of RPOS/RNEG.

#### 2.3.2.1 Transmit Serial Input Clock (TSICLKP/TSICLKN)

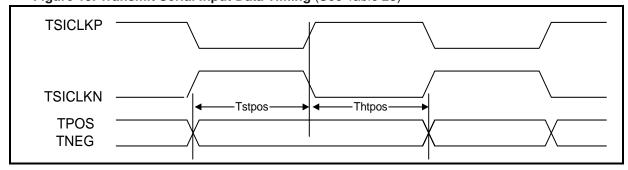

TSICLKP/TSICLKN is the serial input clock from the overhead terminator. This 155.52 MHz clock is rising edge centered with input serial data on TPOS and TNEG. These clock pins should be left open when the LXT6155 operates in parallel mode.

#### 2.3.2.2 Receive Serial Output Clock (RSOCLKP/RSOCLKN)

RSOCLKP/RSOCLKN is the serial clock recovered from the line input data on RTIP/RRING. This 155.52 MHz clock is falling edge centered with receive serial output data on RPOS/RNEG. These clock pins should be left open when the LXT6155 operates in parallel mode. Under LOS

(LOS=High) or Rx PLL loss of lock (LOCK=Low) conditions RSOCLK P/N is switched to the Tx serial clock. Also the serial output data is forced to all zeros. This feature can be disabled in SW mode (HWSEL = High) via register #10, bit #7.

#### 2.3.3 Crystal Reference Clock (XTALIN/XTALOUT)

An optional 19.44 MHz crystal can be connected across the XTALIN and XTALOUT pins. This crystal reference provides an onchip clock that is independent of the external system clock (TSICLKP/TSICLKN or TPICLK). The main functions of the crystal reference clock are threefold: (1) to center the receive PLL at 155 MHz, (2) to keep the PLL centered at 155 MHz when LOS asserts, and (3) In the event incoming data is lost, to provide a reference clock for other devices which require it. The designer has the option to use this crystal reference clock or the transmit input clock (TSICLKP/TSICLKN or TPICLK) to center the receive PLL.

#### 2.4 Jitter

The Bellcore GR-253 standard defines jitter as the "short-term variations of a digital signal's significant instants from their ideal positions in time". Significant instants are the optimum data sampling instants. Jitter parameters can be measured at the line interface, with system interface in loopback mode, yielding jitter accumulated in both transmitter and receiver. Isolated jitter measurements for transmitter and receiver can also be performed. Jitter specs are divided into three categories: jitter tolerance, jitter generation, and jitter transfer. Jitter values, in effect, measure the performance of the receive PLL and the transmit synthesizer PLL.

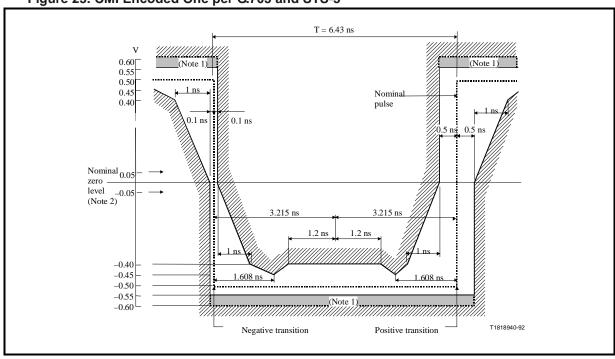

#### 2.4.1 Jitter Tolerance

Jitter tolerance is the peak-to-peak amplitude of sinusoidal jitter applied at the line interface input that causes an equivalent 1 dB SNR loss measured as BER =  $10^{-10}$ . Refer to Figure 26 on page page 44 for the LXT6155 performance.

#### 2.4.2 Jitter Generation (Intrinsic Jitter)

Jitter generation is the amount of transmit jitter at the output of the equipment with a jitter-free transmit input data and clock. For SONET/SDH, jitter generation is less than 0.01 UI rms, measured with a band-pass filter from 12 kHz to 1.3 MHz. Refer to 27 on page 45 for the LXT6155 performance.

#### 2.4.3 Jitter Transfer

Jitter transfer is defined as the ratio of output jitter to input jitter amplitude versus jitter frequency for a given bit rate. Input jitter amplitude is shown in the Jitter Tolerance curve. Output jitter is under the Jitter Transfer template. Refer to Figures 27 and 28 on pages and for the LXT6155 performance.

## 2.5 Operational Modes

The LXT6155 functions in both Hardware standalone and Software modes. The operating mode is set by the state of the  $\overline{HWSEL}$  pin.

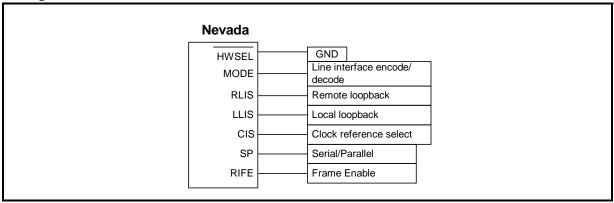

#### 2.5.1 Hardware Mode

By setting HWSEL = Low, the LXT6155 operates in standalone hardware mode, without a serial microprocessor interface. A subset of the functions available in the Software Mode can be set in Hardware Mode. LXT6155 provides a comprehensive flexibility in configuring system clock preference settings, as well as providing pins for activating loopback test modes. Tables 3, 4 and 5 show the settings that enable the functions available in hardware mode.

Figure 7. Hardware Mode

Table 3. Reference Clock Settings<sup>1</sup>

| CIS                                           | Clock Reference | Note                                                                                                                                                                                                                                           |  |

|-----------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Low                                           | TICLK           | Default mode. The LXT6155 uses the transmit input clock as the reference clock for on chip operations. No crystal is needed.                                                                                                                   |  |

| High                                          | XTAL            | The LXT6155 uses the clock signal at XTALIN as the reference clock for Rx operation. This can either be an applied 19.44MHz clock or a 19.44MHz crystal can be connected across XTALIN & XTALOUT. See Table 24 for the crystal specifications. |  |

| 1. For explanation, see clock sections below. |                 |                                                                                                                                                                                                                                                |  |

#### 2.5.1.1 PLL Clock Reference (CIS pin)

The reference clock plays two roles: it centers the receive PLL, and it provides the receive output clocks RSOCLKP/RSOCKLN and RPOCLK in case of Loss of Signal. When the LXT6155 powers up, it looks for this reference clock to start-up internal blocks, including the receive PLL circuitry.

#### 2.5.1.1.1 TICLK

This is the transmit input clock(s): either TSICLKP/TSICLKN in serial mode or TPICLK in parallel mode.

#### 2.5.1.1.2 XTAL

XTAL is an optional clock, created using an external crystal, connected across the XTALIN and XTALOUT pins. The crystal provides an independent and stable clock source. This clock is also used as the reference for the Tx clock monitoring circuitry.

#### 2.5.1.2 Loopback Test (RLIS and LLIS pins)

The LXT6155 allows two types of loopback test: Remote loopback and Local loopback. In Remote loopback, the received data and clock are looped back to the transmit line interface. The LXT6155 still outputs recovered data and clock at the system interface. In Local loopback, the transmit data is looped back to the receive input at the line interface. The LXT6155 also transmit data onto the line interface while looping back. For descriptive diagrams, please refer to Figures 13 and 14.

Table 4. Loopback Selection

| RLIS | LLIS | Description                            |

|------|------|----------------------------------------|

| Low  | Low  | Normal operation. No loopback testing. |

| Low  | High | Local loopback test activate.          |

| High | Low  | Remote loopback test activate.         |

| High | High |                                        |

#### 2.5.1.3 Line Interface Selection (MODE Pin)

The MODE pin sets one of the two line interfaces, as described in Table 5.

Table 5. MODE Line Interface Settings

| MODE | Description                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------------------------------------|

| Low  | Sets LVPECL NRZ mode to interface to a fiber optic module. CMI related blocks (e.g. input/output buffers, equalizer) are disabled. |

| High | Sets CMI mode to interface to a transformer and a 75 $\Omega$ coax cable. NRZ related input/output buffers are disabled.           |

#### 2.5.1.4 Parallel/Serial Mode Selection (SP pin)

In Hardware Mode,  $\overline{HWSEL}$  = Low, the LXT6155 can be set to operate in serial or parallel data mode, depending on how the Serial/Parallel SP pin is set.

Setting the SP pin = High sets the LXT6155 to an 8-bit parallel mode. Parallel pins TPID<7:0>, TPICLK, RPOD<7:0>, ROFP, RPOCLK, LOCK and LOS are be used. Serial pins TPOS, TNEG, TSICLKP, TSICLKN, RPOS, RNEG, RSOCLKP, RSOCLKN are unused and should be left open.

Setting the SP pin = Low sets the LXT6155 to serial mode. Pins TPOS, TNEG, TSICLKP, TSICLKN, RPOS, RNEG, RSOCLKP, RSOCLKN, LOCK and LOS are used. Pins TPID<7:0>, TPICLK, RPOD<7:0> and RPOCLK are unused and should be left open.

#### 2.5.1.5 Tx Amplitude Trim

In Hardware, serial, coax mode, the line driver output amplitude can be controlled via pins 16 to 20. Setting TXTRIMENA (pin #20) high enables the trim capability. The trim rage is -21% to +24% in 3% steps controlled by TXTRIM0-TXTRIM3. The minimum amplitude is at 0000 and the maximum amplitude is at 1111. This is the same control range as in SW mode.

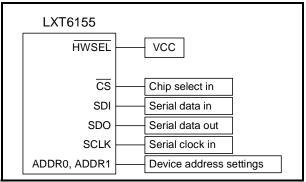

#### 2.5.2 Software Mode

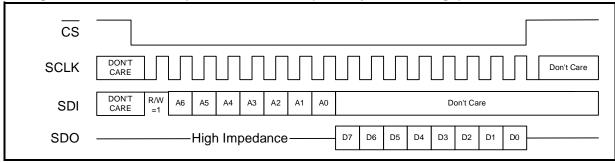

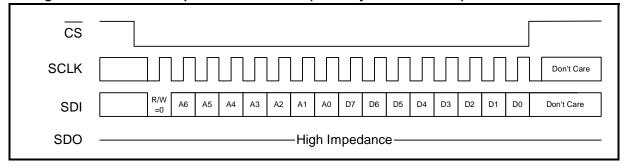

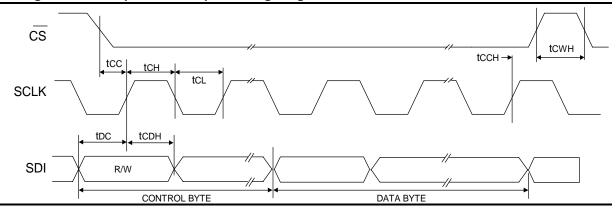

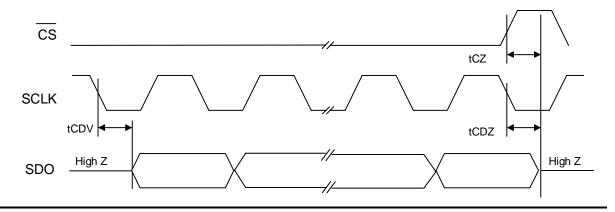

When  $\overline{HWSEL}$  = High, the LXT6155 operates in Software Mode. Control is through an external serial  $\mu P$  interface. Figure 8 shows the pins used in Software Mode. The LXT6155 uses four pins for the industry standard Serial Control Interface (SCP) bus: SCLK,  $\overline{CS}$ , SDI and SDO. SCLK is the serial input control clock pin.  $\overline{CS}$  is the chip select input. SDI is the serial data input pin, and SDO is the serial data output pin. Figures 9 and 10 show the serial interface data structure. A data transaction is initiated by a falling edge on the Chip Select pin  $\overline{CS}$ . A High-to-Low transition on  $\overline{CS}$  is required for each access to the control registers. The first bit is a read/write bit (R/ $\overline{W}$ ), followed by seven address bits (A<6:0>), and eight data bits (D<7:0>). Every data transaction requires 16 SCLK cycles to complete. If R/ $\overline{W}$  = High (Read), the LXT6155 outputs a data byte D<7:0> on the SDO pin. If R/ $\overline{W}$  = Low (Write), the LXT6155 accepts a data byte D<7:0> on the SDI pin, while tristating SDO pin.

It is recommended in SW mode operation, the registers are first initialized by writing a "0" to register #11 bit #6 (reset).

#### 2.5.2.1 Serial Input Clock (SCLK)

This pin accepts a clock up to 4.096 MHz for data transactions between the LXT6155 and the SCP bus. The LXT6155 clocks SDO data out on the falling edge, and clocks SDI data in on the rising edge of SCLK (see Figures 9 and 10).

#### 2.5.2.2 Chip Select Input (CS)

On the falling edge of  $\overline{CS}$ , the LXT6155 starts data transactions. On the rising edge of  $\overline{CS}$ , the LXT6155 stops data transaction. The  $\overline{CS}$  pin must be held Low for at least 16 SCLK cycles to complete a full Read or Write data transaction. If  $\overline{CS}$  is held Low less than 16 SCLK cycles, then the data transaction is ignored. At the end of each Write/Read transaction,  $\overline{CS}$  must return High, between the 16th and 17th clock edges.

#### 2.5.2.3 Serial Input Word (SDI)