# **AK2301A**

# 3.3V Single channel PCM CODEC LSI

## **GENERAL DESCRIPTION**

The AK2301A is a single channel PCM CODEC for speech processing 8kHz sampling PCM data by DSP. The AK2301A interfaces with 14bit linear data (16bit format).

It includes Band limiting filter, A/D and D/A converter, and universal op-amps for construction of the output filter. All functions are provided in small 24pin VSOP package and it is good for reducing the mounting space.

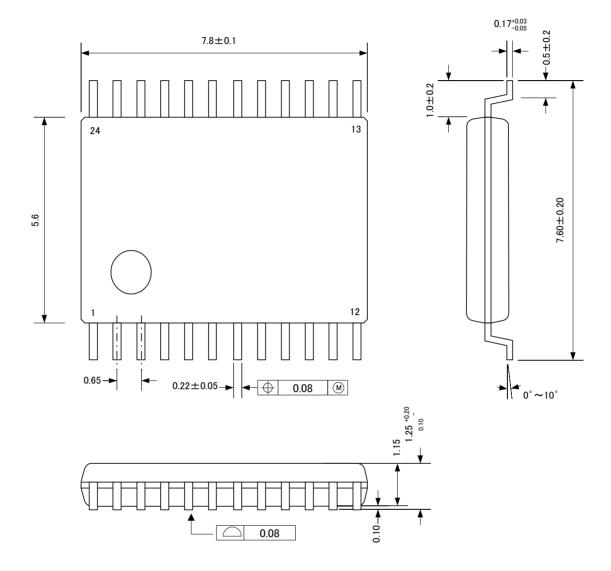

## **PACKAGE**

- 24pin VSOP

- · Pin to pin 7.9mm x 7.6mm

- · Pin pitch 0.65mm

## **FEATURE**

- Single PCM CODEC and filtering systems

- Mute function

- PCM interface; 14bits linear data (16bit format, serial interface)

- Long Frame / Short Frame are selected automatically

- PCM data rate 256kHz/512kHz

- Op-Amp for the external gain adjustment

- Dual universal op-amps

- Single power supply voltage  $+3.3\pm0.3V$

- Low power consumption

- Small package

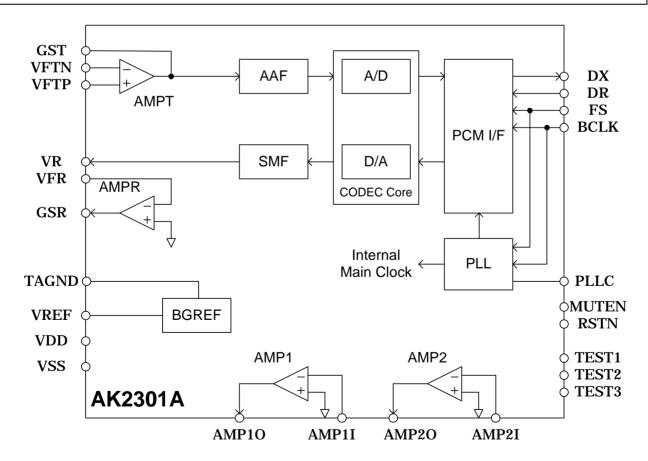

## **BLOCK DIAGRAM**

## CONTENT

|   | ITEMS                           | PAGE |

|---|---------------------------------|------|

|   |                                 |      |

| - | BLOCK DIAGRAM                   | 1    |

| _ | PIN CONDITION                   | 3    |

| - | PIN FUNCTION                    | 4    |

| _ | ABSOLUTE MAXIMUM RATINGS        | 5    |

| - | RECOMMENDED OPERATING CONDITION | ONS5 |

| _ | ELECTRICAL CHARACTERISTICS      | 5    |

| _ | PACKAGE INFORMATION             | 10   |

| _ | PIN ASSIGNMENT                  | 11   |

| _ | MARKING                         | 11   |

| _ | CIRCUIT DESCRIPTION             | 12   |

| _ | FUNCTIONAL DESCRIPTION          | 13   |

| _ | PCM CODEC                       | 13   |

| _ | PCM INTERFACE                   | 14   |

| _ | Long Frame / Short Frame        | 14   |

| _ | MUTE                            |      |

| - | RESET SEQUENCE                  | 17   |

| _ | Universal op-amps               | 18   |

| _ | APPLICATION CIRCUIT EXAMPLE     | 19   |

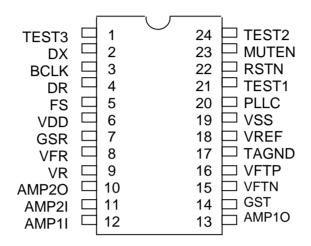

## PIN CONDITION

| Pin# | Name  | I/O | Pin type | AC load<br>(MAX.) | DC load<br>(MIN.)    | Output<br>status<br>(mute) | Remarks                                                                 |

|------|-------|-----|----------|-------------------|----------------------|----------------------------|-------------------------------------------------------------------------|

| 15   | VFTN  | ı   | Analog   |                   |                      |                            |                                                                         |

| 16   | VFTP  | I   | Analog   |                   |                      |                            |                                                                         |

| 14   | GST   | 0   | Analog   | 50pF              | AC load<br>10kΩ (*1) |                            |                                                                         |

| 7    | GSR   | 0   | Analog   | 40pF              | AC load<br>8kΩ (*1)  |                            |                                                                         |

| 8    | VFR   | - 1 | Analog   |                   |                      |                            |                                                                         |

| 9    | VR    | 0   | Analog   | 40pF              | AC load<br>8KΩ (*1)  | Analog ground              |                                                                         |

| 6    | VDD   | -   |          |                   |                      |                            |                                                                         |

| 19   | VSS   | -   |          |                   |                      |                            |                                                                         |

| 5    | FS    |     | CMOS     |                   |                      |                            |                                                                         |

| 3    | BCLK  | Ι   | CMOS     |                   |                      |                            |                                                                         |

| 2    | DX    | 0   | CMOS     | 50pF              |                      | Hi-Z                       |                                                                         |

| 4    | DR    |     | CMOS     |                   |                      |                            |                                                                         |

| 23   | MUTEN | Ι   | CMOS     |                   |                      |                            |                                                                         |

| 22   | RSTN  | Ι   | CMOS     |                   |                      |                            |                                                                         |

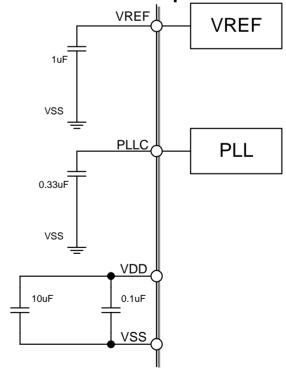

| 18   | VREF  | 0   | Analog   |                   |                      |                            | - External capacitance 1.0µF or more                                    |

| 20   | PLLC  | 0   | Analog   |                   |                      |                            | - External capacitance 0.33µF±40% (Includes temperature characteristic) |

| 17   | TAGND | 0   | Analog   |                   |                      |                            | - External<br>capacitance<br>1.0µF or more<br>- 150uA load max          |

| 11   | AMP2I | I   | Analog   |                   |                      |                            |                                                                         |

| 12   | AMP1I | I   | Analog   |                   |                      |                            |                                                                         |

| 13   | AMP1O | 0   | Analog   | 40pF              | AC load<br>8kΩ (*1)  |                            |                                                                         |

| 10   | AMP2O | 0   | Analog   | 40pF              | AC load<br>8kΩ (*1)  |                            |                                                                         |

| 21   | Test1 | I   | CMOS     | _                 |                      | _                          | - Tie to the VSS                                                        |

| 24   | Test2 | ı   | CMOS     | _                 | _                    | _                          | - Tie to the VSS                                                        |

| 1    | Test3 |     | CMOS     | _                 | _                    | _                          | - Tie to the VSS                                                        |

<sup>\*1)</sup> AC load is a load against AGND. This value includes a feedback resistance of input/output op-amp.

#### PIN FUNCTION Pin types NIN: Normal input TOUT: Try state output AOUT: Analog output PWR: Power / Ground AIN: Analog input Pin# Name Type **Function** Neagative analog input of the transmit OP amp. 15 VFTN AIN Diffelential or single amplifire is composed with the VFTP and the external registers. Transmit gain is defined by the ratio of the external registers. VFTP Positive analog input of the transmit OP amp. 16 AIN 14 GST **AOUT** Output of the transmit OP amp. The external feedback resister is connected between this pin and VFTP. AOUT Output of the receive OP amp. 7 **GSR** Receive gain is defined by the ratio of the external registers. The differential output can be composed with using the VR. 8 VFR AIN Negative analog input of the receive OP amp. VR AOUT Analog output of the D/A convertor equivalent to the received PCM code. 9 PWR Positive supply voltage 6 VDD +3.3V supply Ground (0V) 19 VSS **PWR** Frame sync input FS NIN 5 This clock is input for the internal PLL which gerenates the internal system clocks. FS must be 8kHz clock which synchronized with BCLK and do not stop feeding. NIN Bit clock of PCM data interface 3 **BCLK** This clock defines the input/output timing of DX and RX. The frequency of BCLK should be 256kHz or 512kHz and do not stop feeding. TOUT DX Serial output of PCM data The PCM data is synchronized with BCLK. This output remains in the high impedance except for the period in which PCM data is transmitted. 4 DR NIN Serial input of PCM data The PCM data is synchronized with BCLK. Mute setting pin 23 MUTEN NIN "L" level forces both A/D, D/A output to mute state. NIN Reset signal input pin 22 **RSTN** Reset operation starts by low input. This pin is used for the initialization at the power up. Please use MUTEN pin together to avoid the popping sound output until the LSI finish the initialaization after the power up. (Refer to P.13) VREF **AOUT** Analog ground output 18 External capacitance (1.0µF or more) should be connected between this pin and VSS. Please do not connect external load to this pin. 20 PLLC AOUT PLL loop filter output External capacitance (0.33µF±40%: Includes temperature characteristic) should be connected between this pin and VSS. 17 **TAGND AOUT** Analog ground output for transmitte OP amp 150uA load max. External capacitance (1.0µF or more) should be connected between this pin and VSS. This pin is used as an analog ground for transmit OP amp (AMPT). AIN 11 AMP1I Negative input of the universal OP amp 12 AMP2I 13 AMP10 **AOUT** Output of the universal OP amp 10 AMP20 Test pins ("H"=test mode) 21 TEST1 NIN 24 Please tie to VSS TEST2 1 TEAT3

## ABSOLUTE MAXIMUM RATINGS

| Parameter                                | Symbol | Min  | Max     | Units                  |

|------------------------------------------|--------|------|---------|------------------------|

| Power supply voltage                     |        |      |         |                        |

| Analog/Digital power supply              | VDD    | -0.3 | 4.6     | V                      |

| Digital input voltage                    | VTD    | -0.3 | VDD+0.3 | V                      |

| Analog input voltage                     | VTA    | -0.3 | VDD+0.3 | V                      |

| Input current (except power supply pins) | IIN    | -10  | 10      | m A                    |

| Storage temperature                      | Tstg   | -55  | 125     | $^{\circ}\!\mathbb{C}$ |

Warnig: Exceeding absolute maximum ratings may causepermanent damage. Normal operation is not guranteed at these extermes.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                     | Symbol | Min   | Тур | Max   | Units      |

|-------------------------------|--------|-------|-----|-------|------------|

| Power supply voltage          | VDD    | 3.0   | 3.3 | 3.6   | V          |

| Analog/Digital power supply   |        |       |     |       |            |

| Ambient operating temperature | Ta     | -40   |     | 85    | $^{\circ}$ |

| Frame sync frequency *)       | FS     | -1.0% | 8   | +1.0% | kHz        |

Note) All voltages reference to ground: VSS = 0V

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, guaranteed for VDD =  $+3.3V\pm0.3V$ , Ta =  $-40\sim+85^{\circ}$ C, FS=8kHz, VSS=0V

## **DC Characteristics**

| Parameter                        | Symbol | Conditions                 | Min    | Тур | Max    | Unit           |

|----------------------------------|--------|----------------------------|--------|-----|--------|----------------|

| Power Consumption<br>BCLK=512kHz | PDD1   | All output unloaded<br>*1) |        | 10  | 15     | mA             |

| Output high voltage              | Vон    | Iон=-1.6mА                 | 0.8VDD |     |        | V              |

| Output low voltage               | Vol    | IOL=1.6mA                  |        |     | 0.4    | V              |

| Input high voltage               | VIH    |                            | 0.7VDD |     |        | V              |

| Input low voltage                | VIL    |                            |        |     | 0.3VDD | V              |

| Input leakage current            | ILL    |                            | -10    |     | +10    | μΑ             |

| Anarog ground output voltage     | VRG    |                            | 1.4    | 1.5 | 1.6    | V              |

| Output leakage current           | ILT    | Tri-state mode             | -10    |     | +10    | $\mu$ <b>A</b> |

<sup>\*1)</sup> VFTN/P=1020Hz@0dBm0 input, DR=1020Hz@0dBm0 Code input

<sup>\*)</sup> All the characteristics of the CODEC is definied by 8kHz FS.

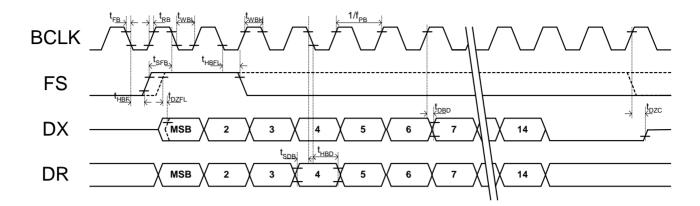

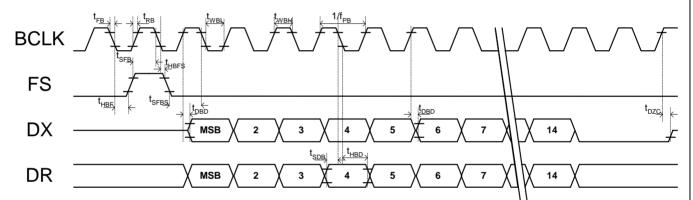

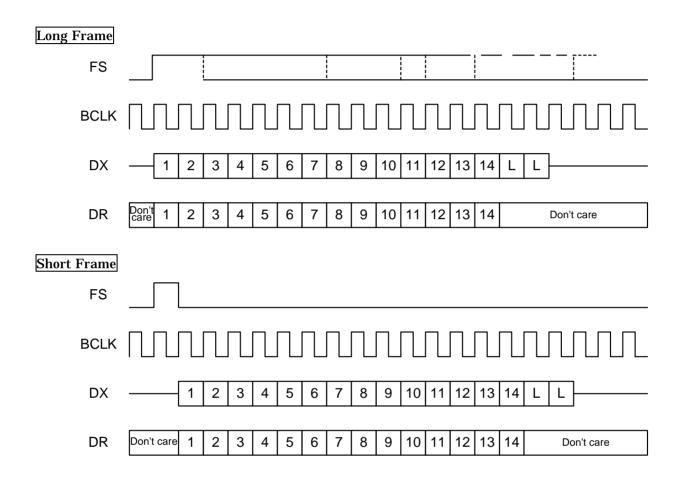

## **PCM INTERFACE** (Lomg Frame, Short Frame)

All timing parameters of the output pins are measured at VOH = 0.8VDD and VOL = 0.4V. Input pins are measured at VIH = 0.7VDD and VIL = 0.3VDD.

## **AC Characteristics**

| Parameter                                                          | Symbol                             | Min   | Тур           | Max   | Unit | Ref Fig |

|--------------------------------------------------------------------|------------------------------------|-------|---------------|-------|------|---------|

| FS Frequency                                                       | f <sub>PF</sub>                    | -1.0% | 8             | +1.0% | kHz  |         |

| BCLK Frequency                                                     | f <sub>PB</sub>                    | ı     | 32FS/<br>64FS | -     | kHz  |         |

| BCLK Pulse Width (High/Low) (BCLK=32×FS=256kHz)                    | t <sub>WBH</sub>                   | 1.563 | 1.953         | 2.344 | μs   |         |

| BCLK Pulse Width (High/Low) (BCLK=64×FS=512kHz)                    | t <sub>WBH</sub>                   | 0.781 | 0.977         | 1.172 | μs   |         |

| Rising/Falling Time: (BCLK,FS0,FS1,DX0,DX1,DR0,DR1)                | t <sub>RB</sub><br>t <sub>FB</sub> |       |               | 40    | ns   |         |

| Hold Time: BCLK Low to FS High                                     | t <sub>HBF</sub>                   | 60    |               |       | ns   | Fig1, 2 |

| Setup Time: FS High to BCLK Low                                    | t <sub>SFB</sub>                   | 60    |               |       | ns   |         |

| Setup Time: DR to BCLK Low                                         | t <sub>SDB</sub>                   | 60    |               |       | ns   |         |

| Hold Time: BCLK Low to DR                                          | t <sub>HBD</sub>                   | 60    |               |       | ns   |         |

| Delay Time: BCLK High to DX valid Note1)                           | t <sub>DBD</sub>                   |       |               | 60    | ns   |         |

| Delay Time: BCLK High to DX High-Z Note1)                          | t <sub>DZC</sub>                   |       |               | 60    | ns   |         |

| Long Frame                                                         |                                    |       |               |       |      |         |

| Hold Time: 2 <sup>nd</sup> period of BCLK Low to FS Low            | t <sub>HBFL</sub>                  | 60    |               |       | ns   |         |

| Delay Time: FS or BCLK High, whichever is later,to DX valid<br>注1) | t <sub>DZFL</sub>                  |       |               | 60    | ns   | Fig1    |

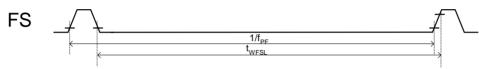

| FS Pulse Width Low                                                 | t <sub>WFSL</sub>                  | 1     |               |       | BCLK |         |

| Short Frame                                                        |                                    |       |               |       |      |         |

| Hold Time: BCLK Low to FS Low                                      | t <sub>HBFS</sub>                  | 60    |               |       | ns   | Fig2    |

| Setup Time: FS Low to BCLK Low                                     | t <sub>SFBS</sub>                  | 60    |               |       | ns   | 1 192   |

Note1) Measured with 50pF load capacitance and 0.2mA drive.

Fig1. Long Frame

Fig2. Short Frame

## CODEC

\* The receive and transmit op-amp's characteristics are measured at the 0dB gain.

The frequency specifications when FS deviation from 8kHz are as follows:

$$\frac{\textit{Used} \quad FS}{8k[Hz]} \times \textit{noted frequency specification} = \textit{Effective frequency specification}$$

## **Absolute Gain**

| Parameter              |               | Conditions         | Min  | Тур   | Max | Unit |

|------------------------|---------------|--------------------|------|-------|-----|------|

| Analog input level     | VFTP,VFTN     | 0dBm0@1020Hz input | _    | 0.531 | _   | Vrms |

| Absolute transmit gain | $\rightarrow$ |                    | -0.6 | _     | 0.6 | dB   |

| Maximum overload level | DX            | 3.14dBm0           | _    | 0.762 | _   | Vrms |

| Analog output level    | DR            | 0dBm0@1020Hz input | _    | 0.531 | _   | Vrms |

| Absolute receive gain  | $\rightarrow$ |                    | -0.6 | _     | 0.6 | dB   |

| Maximum overload level | VR            | 3.14dBm0           | _    | 0.762 | _   | Vrms |

Frequency response

| Parameter                   | Co           | nditions                   | Min    | Typ | Max   | Unit  |

|-----------------------------|--------------|----------------------------|--------|-----|-------|-------|

|                             |              | TIGITIONS                  | IVIIII | Тур | IVIAX | Offic |

| Transmit frequency response | Relative to: | 0.05kHz                    | 30     |     | _     |       |

| (A→D)                       | 0dBm0@1020Hz | 0.06kHz                    | 26     | 1   | _     |       |

|                             |              | 0.2kHz                     | 0      |     | 1.8   |       |

| $VFTP, VFTN \rightarrow DX$ |              | $0.3{\sim}3.0\mathrm{kHz}$ | -0.15  |     | 0.15  | dB    |

|                             |              | 3.4kHz                     | 0      | 1   | 0.8   |       |

|                             |              | 4.0kHz                     | 14     | -   | _     |       |

| Receive frequency response  | Relative to: | $0\sim$ 3.0kHz             | -0.15  |     | 0.15  |       |

| $(D \rightarrow A)$         | 0dBm0@1020Hz | 3.4kHz                     | 0      | 1   | 0.8   | dB    |

| $DR \rightarrow VR$         |              | 4.0kHz                     | 14     | 1   | _     |       |

## **Distortion**

| Parameter                                                                                  | Condtions   |       | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------|-------------|-------|-----|-----|-----|------|

| $\begin{array}{c} \textbf{Transmit signal to Distortion} \\ (A \rightarrow D) \end{array}$ | 1020Hz Tone | 0dBm0 | 70  | 75  | _   | dB   |

| $VFTP, VFTN \rightarrow DX$                                                                | C-message   |       |     |     |     |      |

| Receive signal to Distortion                                                               | 1020Hz Tone |       |     |     |     |      |

| $(D \rightarrow A)$                                                                        |             | 0dBm0 | 70  | 75  | _   | dB   |

| $DR \rightarrow VR$                                                                        | C-message   |       |     |     |     |      |

## Noise

| Parameter                                                                                                         | Condtions                                 | Min | Тур | Max | Unit   |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|-----|-----|--------|

| Idle channel noise $A \rightarrow D$ (*1)<br>VFTP,VFTN $\rightarrow$ DX                                           | C-message                                 | _   | 8   | 13  | dBrnC0 |

| $\begin{array}{ccc} & Idle \ channel \ noise \ D {\rightarrow} A(^*2) \\ & DR  {\rightarrow}  VR,GSR \end{array}$ | C-message                                 | _   | 5   | 10  | dBrnC0 |

| PSRR<br>Transmit path                                                                                             | $VDD=3.3V/\pm 66mVop$<br>f=0 $\sim$ 10kHz | _   | 55  | _   | dB     |

| PSRR<br>Receiver path                                                                                             | $VDD=3.3V/\pm 66mVop$<br>f=0 $\sim$ 10kHz |     | 55  |     | dB     |

<sup>(\*1)</sup> Analog input is set to the analog ground level (\*2) Digital input is set to the +0 CODE

## Crosstalk

| Parameter                                                                                                     | Condtions                                      | Min | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-----|-----|------|

| $\begin{array}{ccc} \text{Transmit to receive} \\ \text{VFTP,VFTN} & \rightarrow & \text{VR,GSR} \end{array}$ | VFTP,VFTN=0dBm0@1020Hz<br>DR=0-Code            | _   | _   | -75 | dB   |

| Receive to transmit $DR \rightarrow DX$                                                                       | DR=0dBm0@1020Hz code level<br>VFTP,VFTN=0 Vrms | _   | _   | -75 | dB   |

Transmit op-amp characteristics:AMPT

| Parameter        | Conditions                             | Min | Тур | Max | Unit |

|------------------|----------------------------------------|-----|-----|-----|------|

| Load resistance  | AC load, Including feedback registance | 10  |     | _   | kΩ   |

| Load capacitance |                                        |     | 1   | 50  | pF   |

| Gain             | Inverting amplifire                    | -12 | _   | 6   | dB   |

Receive signal output characteristics:VR

| Parameter                   | Conditions        | Min | Тур | Max | Unit               |

|-----------------------------|-------------------|-----|-----|-----|--------------------|

| Output voltage (AGND level) | PCM +0 code input |     | 1.5 | _   | V                  |

| Load resistance             | AC load           | 8   | _   | _   | $\mathbf{k}\Omega$ |

| Load capacitance            |                   | _   | _   | 40  | pF                 |

Receive op-amp characteristics: AMPR

| Parameter            | Conditions                                                                    |   | Тур  | Max | Unit               |

|----------------------|-------------------------------------------------------------------------------|---|------|-----|--------------------|

| Load resistance      | AC load, Including feedback registance 8                                      |   | _    | _   | $\mathbf{k}\Omega$ |

| Load capacitance     |                                                                               | _ | _    | 40  | pF                 |

| SINAD                | 0dB setting, 1020Hz@0dBm0 input NAD VR,GSR differential output With C-message |   | 75   |     | dB                 |

| Gain                 | n Inverting amplifire -12                                                     |   | _    | 6   | dB                 |

| Output voltage swing | ng DR = 3.14dBm0 digital code input                                           |   | 2.15 | _   | Vp-p               |

Universal op-amp characteristics: AMP1,2

| Parameter            | Conditions                                                            |     | Тур  | Max | Unit |  |

|----------------------|-----------------------------------------------------------------------|-----|------|-----|------|--|

| Load resistance      | AC load, Including feedback registance 8                              |     | _    | _   | kΩ   |  |

| Load capacitance     |                                                                       | _   | _    | 40  | pF   |  |

| SINAD                | +6dB setting, 1020Hz@1.125V <sub>P-P</sub> input 5Hz~30kHz measurment |     | 87   |     | dB   |  |

| Gain                 | Inverting amplifire                                                   | -12 | _    | 6   | dB   |  |

| Output voltage swing | +6dB setting, 1020Hz@1.125V <sub>P-P</sub> input                      | 2.1 | 2.25 | _   | Vp-p |  |

## 24PIN VSOP

## **PIN ASSIGNMENT**

## **24PIN VSOP**

TEST1, TEST2 and TEST3 are test pins. Please tie them to the VSS.

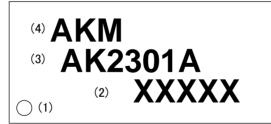

## **MARKING**

(1) 1pin sign

(2) Date Code: 5digit XXXXX(3) Marketing Code: AK2301A

(4) AKM logo

## **CIRCUIT DESCRIPTION**

| BLOCK     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMPT      | Op-amp for input gain adjustment. This op-amp is used as an inverting or differential amplifier. Adjusting the gain with external resistors. The resistor should be larger than $10k\Omega$ for the feedback resistor.                                                                                                                                                                                                                                                                                            |

|           | VFTN: Negative op-amp input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | VFTP: Positive op-amp input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | GST: Op-amp output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AMPR      | Op-amp for output gain adjustment. This op-amp is used as an inverting amplifier. Adjusting the gain with external resistors. The combined resistor larger than $8k\Omega$ is recommended for the feedback and the output load VFR: Negative op-amp input. GSR: Op-amp output. VR and GSR can be used as the differential output.                                                                                                                                                                                 |

| AAF       | Integrated anti-aliasing filter which prevents signals around the sampling rate                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | from folding back into the voice band. AAF is a 2 <sup>nd</sup> order RC active low-pass filter.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CODEC     | Converting the analog signal to 14bit PCM data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | The band limiting filter is also integrated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A/D       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CODEC     | Converting the 14bit PCM data from the DR to the analog signal.  Output of the D/A converter is fed into the SMF to suppress the high frequency                                                                                                                                                                                                                                                                                                                                                                   |

| D/A       | element.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SMF       | Extracts the inband signal from D/A output. It also corrects the sinx/x effect of the D/A output.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BGREF     | Provide the stable analog ground voltage using an on-chip band-gap reference circuit which is temperature compensated. The output voltage is 1.5V for 3.3V An external capacitor of 1.0uF or larger should be connected between VREF and VSS to stabilize analog ground (VREF). Please do not connect external load to this pin. TAGND pin is used as the analog ground level output for the AMPT. An external capacitor of 1.0uF or larger should be connected between TAGND and VSS to stabilize analog ground. |

| PCM I/F   | For the PCM data rate, both 256kHz or 512kHz are available. The 14bit PCM data is input/output by the 2's compliment 16bit serial data format. Two kinds of serial data format (Long Frame/Short Frame) are available. Each data format is automatically detected by AK2301A.  PCM data is input to DR pin and output from DX pin.                                                                                                                                                                                |

| AMP1、AMP2 | Universal op-amp for the filter of the external voice path. The maximum load is $8k\Omega$ (including the feedback resistor and AC load). These op-amps are assumed as using for the inverting LPF with 20kHz cut off frequency.                                                                                                                                                                                                                                                                                  |

## **FUNCTIONAL DESCRIPTIONS**

## **PCM CODEC**

## - A/D

Analog input signal is converted to 14bit PCM data. The analog signal is fed to the anti-aliasing filter (AAF) before the converting PCM data, to prevent signals around the sampling rate from folding back into the voice band. The converted PCM data passes through the band limiting filter which Frequency response is designated in page8, and output from the DX pin with MSB first format. It is synchronized with rising edge of the BCLK. This PCM data is 2's compliment 2digit data and full scale is defined as 3.14dBm0. The analog input of 0.762Vrms is converted to a digital code of 3.14dBm0.

#### D/A

Input PCM data from the DR pin is through the digital filter which Frequency response is designated in page8, and converted analog signal. This analog signal is removed the high frequency element with SMF (fc=30kHz typ) and output from the VR pin. The input PCM data is 2's compliment 2digit data and full scale is defined as 3.14dBm0. When the input signal is 3.14dBm0, the level of the analog output signal becomes 0.762Vrms.

## - PCM digital code

The relation ship between the analog signal and the 14 bit linear code.

| Signal level                     | 14bit linear CODE (MSB First) |  |  |  |

|----------------------------------|-------------------------------|--|--|--|

| + Full scale                     | 01 1111 1111 1111             |  |  |  |

| Peak value of the PCM 0dBm0 CODE | 01 0110 0100 1010             |  |  |  |

| PCM 0-CODE                       | 00 0000 0000 0000             |  |  |  |

| - Full scale                     | 10 0000 0000 0000             |  |  |  |

## **PCM** Data Interface

AK2301A supports the following 2 PCM data formats

- Long Frame Sync (LF)

- Short Frame Sync (SF)

PCM data is interfaced through the pin (DX, DR).

In each case, PCM data is interfaced by the 2's compliment 2digit data with 16bit MSB first format. However, internal CODEC is 14bit format operation, then the lowest 2bits output become to "L" level. For the input, the lowest 2 bits are ignored.

## Selection of the interface format

The AK2301A automatically selects the Long Frame/Short frame by means of detecting the length frame signal.

## LONG FRAME (LF) / SHORT FRAME (SF)

## -Automatic LF/SF detection

AK2301A monitors the duration of the "H" level of FS and automatically selects LF or SF interface format.

| Period of FS="H"          | Frame type |

|---------------------------|------------|

| More than 2clocks of BCLK | LF         |

| 1clock of BCLK            | SF         |

## Timing of the interface

16bit PCM data is accommodated in 1 flame ( $125\mu s$ ) defined by 8kHz frame sync signal. Although there are 4time slot at maximum in 8kHz frame (when BCLK = 512kHz), PCM data for AK2301A occupies first time slot.

## - Frame sync signal (FS)

8kHz reference signal. This signal indicated the timing and the frame position of 8kHz PCM interface. All the internal clock of the LSI is generated based on this FS signal.

## -Bit clock (BCLK)

BCLK defines the PCM data rate. BCLK rate is 256kHz or 512kHz. This clock must be synchronized with FS.

## Important notice!

## Please don't stop feeding FS and BCLK.

Both FS and BCLK is used as the internal reference clock. LSI does not work when the FS and BCLK are not provided.

# **MUTE**

The output of the PCM CODEC can be muted by pin control.

MUTEN pin

| MUTEN pin | Operation | DX pin          | VR pin                 |

|-----------|-----------|-----------------|------------------------|

| 0         | Mute      | High-Impedance  | CODEC analog<br>ground |

| 1         | Normal    | PCM data output | CODEC analog output    |

## [DX pin]

When the MUTEN pin turns to "L" during the data output, the mute function becomes available at the top of the next FS.

## [VR pin]

When the MUTEN pin turns to "L", 0 code is fed to the D/A converter and VR becomes at analog ground level.

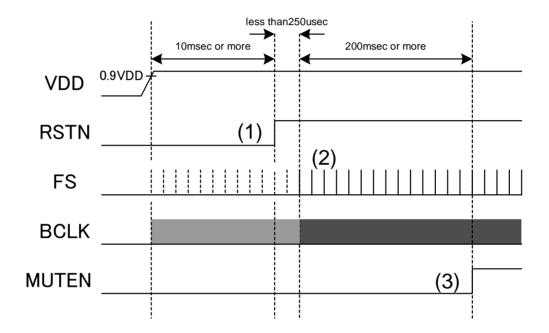

# ASAHI KASEI AK2301A RESET and Start up sequence

Reset operation starts by low input.

This function is used for the initialization at the power up. Please use MUTEN together with RSTN to avoid the popping sound from the output until the AK2301A moves into the stable operation.

## - Start up sequence

- (1) After the power on, please set the RSTN pin to low level for 10msec or more.

- (2) Before the first sequence or less than  $250\mu s$  after the cancellation of reset, please provide the FS and the BCLK.

- (3) Please set the MUTEN pin to low level during the period of the AK2301A's initialization which is less than 200msec after the FS and the BCLK provided. The CODEC voice path is established by releasing the mute function.

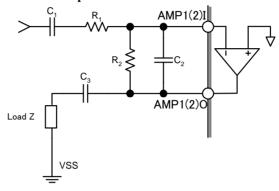

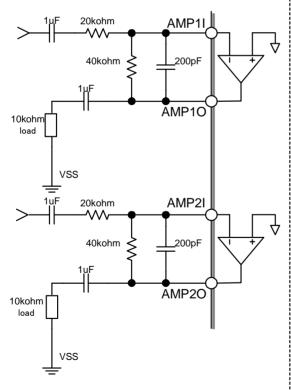

## **Universal op-amps**

The op-amps for construction of the external filter.

The AMP1(2)I is negative input and the AMP1(2)O is output of the op-amp.

## - Circuit example

Please design output load may become  $8k\Omega$  or more. The output load includes a feedback resistor and AC load. These op-amps are assumed to be used for 20kHz max cut off frequency LPF. And please design the gain may become -12~6dB.

The following figure shows the circuit example.

Each parameter is calculated as is shown below.

LPF cut-off frequency  $f_{cL}[Hz]$ :  $f_{cL}=1/(2\pi R_2 C_2)$

Output load  $L[\Omega]$ :  $L=R_2Z/(R_2+Z)$ Gain A[dB]: A=20log  $(R_2/R_1)$

HPF cut-off frequency  $f_{cH}[Hz]$ :  $f_{cH}=1/(2\pi R_1 C_1)$

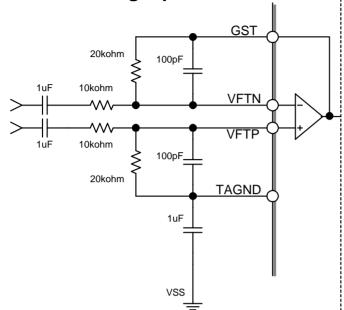

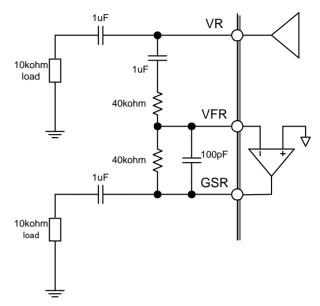

## **APPLICATION CIRCUIT EXAMPLES**

# **Analog input circuit**

# **Analog output circuit**

## **Universal op-amps**

# Power supply, PLL loop filter capacitor and analog ground stabillization capacitor

#### IMPORTANT NOTICE

These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status. AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein. Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials. AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:

(a) A hazard related device or system is one designed or intended for life support or

Representative Director of AKM. As used here:

(a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

(b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

I It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification. from the use of said product in the absence of such notification.