## Am2968A

## Advanced Micro Devices

## 256K Dynamic Memory Controller/Driver

#### DISTINCTIVE CHARACTERISTICS

- Provides control for 16K, 64K, and 256K dynamic RAMs

- Outputs directly drive up to 88 DRAMs, with a guaranteed worst-case limit on the undershoot

- Highest-order two address bits select one of four banks of RAMs

- Separate output enable for multi-channel access to memory on surface-mount packages

- Supports scrubbing operations and other specialty access modes

- Upgrade path to Am29368 1M DRAM Controller

#### **GENERAL DESCRIPTION**

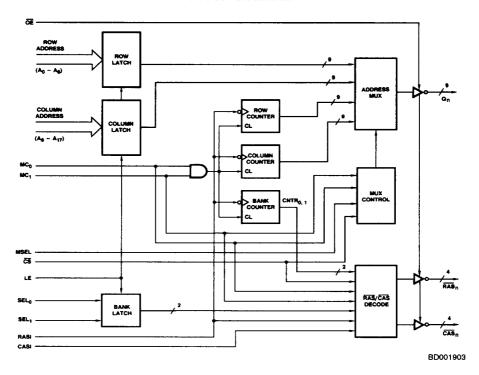

The Am2968A Dynamic Memory Controller/Driver (DMC) is intended to be used with today's high performance memory systems. The DMC acts as the address controller between any processor and dynamic memory array, using its two 9-bit address latches to hold the Row and Column addresses for any DRAM up to 256K. These latches, and the two Row/Column refresh address counters, feed into a 9-bit, 4-input MUX for output to the dynamic RAM address lines. A 2-bit bank select latch for the two high-order address bits is provided to select one each of the four RAS<sub>n</sub> and CAS<sub>n</sub> outputs.

The Am2968A has two basic modes of operation, read/write and refresh. In refresh mode, the two counters cycle through the refresh addresses. If memory scrubbing is not being implemented, only the Row Counter is used, generating up to 512 addresses to refresh a 512-cycle-refresh 256K DRAM. When memory scrubbing is being performed, both the Row and Column counters are used to perform read-modify-write cycles. In this mode all RAS<sub>n</sub> outputs will be active while only one CAS<sub>n</sub> is active at a time.

#### **BLOCK DIAGRAM**

Publication# 04564 Rev. D Amendment /0 Issue Date: January 1990

6-88

#### **RELATED AMD PRODUCTS**

| Part No.  | Description                                      |

|-----------|--------------------------------------------------|

| Am29C668  | 4M Configurable Dynamic Memory Controller/Driver |

| Am29C660D | 12ns 32-Bit Cascadable EDC                       |

| Am29C983A | 9-Bit x 4-Port Multiple Bus Exchange, High Speed |

| Am29C985  | 9-Bit x 4-Port Multiple Bus Exchange w/Parity    |

| Am29C60A  | 16-Bit Cascadable EDC, High Speed                |

| Am29368   | 1M Dynamic Memory Controller/Driver              |

| Am2971A   | 100MHz Enhanced Programmable Event Generator     |

| Am2976    | 11-Bit DRAM Driver                               |

| Am2965/6  | 8-Bit DRAM Driver (Inverting, Non-inverting)     |

| Am29C827A | 10-Bit Buffer                                    |

| Am29C828A | 10-Bit Buffer (Inverting)                        |

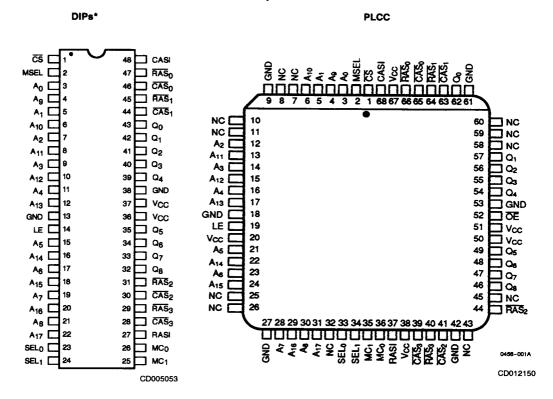

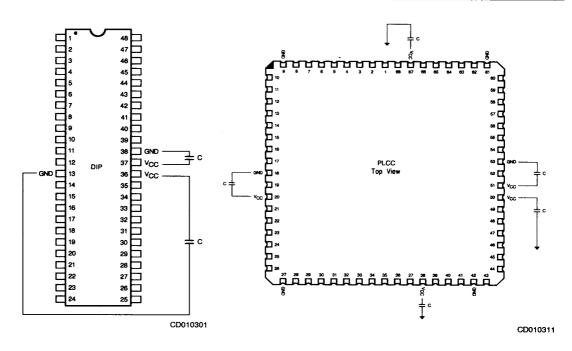

## CONNECTIONS DIAGRAMS Top View

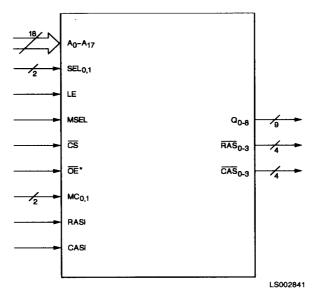

## LOGIC DIAGRAM

Die Size: 0.205" x 0.256"

Gate Count: 300

| Parameter       | CERDIP | PDIP | PLCC | Units |

|-----------------|--------|------|------|-------|

| $\theta_{JA}$   | 37     | 55   | 31   | 35    |

| θ <sub>JC</sub> | 10     | N/A  | 6    | N/A   |

\* Available only on surface mount packages.

6-90

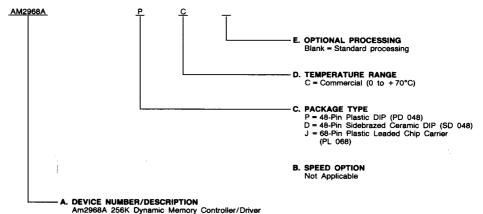

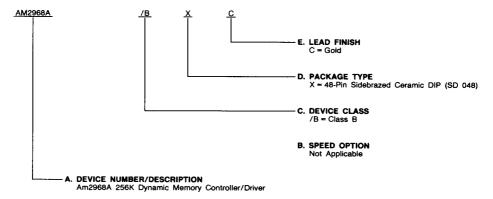

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

# Valid Combinations AM2968A PC, DC, JC

## Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

## **ORDERING INFORMATION (Cont'd.)**

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

#### Valid Combinations

|         | Valid | Cor | nbinations |  |

|---------|-------|-----|------------|--|

| AM2968A |       |     | /BXC       |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of 1, 2, 3, 9, 10, 11

## PIN DESCRIPTION

#### A<sub>0</sub> - A<sub>17</sub> Address inputs (inputs 18)

$A_0$  –  $A_8$  are latched in as the nine-bit Row Address for the RAM. These inputs drive  $Q_0$  –  $Q_8$  when the Am2968A is in the Read/Write mode and MSEL is LOW.  $A_9$  –  $A_{17}$  are latched in as the Column Address, and will drive  $Q_0$  –  $Q_8$  when MSEL is HIGH and the DMC is in the Read/Write mode. The addresses are latched with the Latch Enable (LE) signal.

CAS<sub>0-3</sub> Column Address Strobe (Outputs 4, Active LOW)

During normal Read/Write cycles the two select bits (SEL<sub>0</sub>, SEL<sub>1</sub>) determine which CAS<sub>n</sub> output will go active following CASI going HIGH. When memory scrubbing is performed, only the CAS<sub>n</sub> signal selected by CNTR<sub>0</sub> and CNTR<sub>1</sub> will be active (see CAS Output Function Table). For non-scrubbing cycles, all four CAS<sub>n</sub> outputs remain HIGH.

#### CS Chip Select (Input, Active LOW)

This active-LOW input is used to select the DMC. When  $\overline{CS}$  is active, the Am2968A operates normally in all four modes. When  $\overline{CS}$  goes HIGH, the device will not enter the Read/Write mode. This allows more than one Am2968A DMC to control the same memory, thus providing an easy method for expanding the memory size.

#### LE Latch Enable (Input, Active HIGH)

This active-HIGH input causes the Row, Column, and Bank Select latches to become transparent, allowing the latches to accept new input data. A LOW input on LE latches the input data, assuming it meets the setup and hold time requirements.

#### MC<sub>0-1</sub> Mode Control (Inputs 2)

These inputs are used to specify which of the four operating modes the DMC should be using. The description of the four operating modes is given in Table 1.

### MSEL Multiplexer Select (Input)

This input determines whether the Row or Column Address will be sent to the memory address inputs. When MSEL is HIGH the Column Address is selected, while the Row Address is selected when MSEL is LOW. The address may come from either the address latch or refresh address counter depending on MC<sub>0.1</sub>.

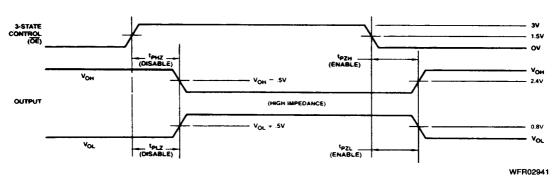

## OE Output Enable (Input, Active LOW, Three-State)

This active-LOW input enables/disables the output signals. When OE is HIGH, the outputs of the DMC enter the high-impedance state. OE is only available on the surface-mount packages.

#### Q<sub>0-8</sub> Address Outputs (Outputs 9)

These address outputs will feed the DRAM address inputs, and provide drive for memory systems up to 500 picofarads in capacitance.

## RAS<sub>0-3</sub> Row Address Strobe (Outputs 4, Active LOW)

Each one of the Row Address Strobe outputs provides a RAS<sub>n</sub> signal to one of the four banks of dynamic memory. Each will go LOW only when selected by SEL<sub>0</sub> and SL<sub>1</sub> and only after RASI goes HIGH. All four go LOW in response to RASI in either of the Refresh modes.

## RASI Row Address Strobe (Input Active High)

During normal memory cycles, the decoded RAS<sub>n</sub> output (RAS<sub>0</sub>, RAS<sub>1</sub>, RAS<sub>2</sub>, or RAS<sub>3</sub>) is forced LOW after receipt of RASI. In either Refresh mode, all four RAS<sub>n</sub> outputs will go LOW following RASI going HIGH.

#### SEL<sub>0-1</sub> Bank Select (Inputs 2)

These two inputs are normally the two higher-order address bits, and are used in the Read/Write mode to select which bank of memory will be receiving the  $\overline{RAS}_n$  and  $\overline{CAS}_n$  signals after RASI and CASI go HIGH.

#### **FUNCTIONAL DESCRIPTION**

#### **Architecture**

The Am2968A provides all the required data and refresh addresses needed by the dynamic RAM memory. In normal

operation, the Row and Column addresses are multiplexed to the dynamic RAM by using MSEL, with the corresponding RAS<sub>n</sub> and CAS<sub>n</sub> signals activated to strobe the addresses into the RAM. High capacitance drivers on the outputs allow the DMC to drive four banks of 16-bit words, including a 6-bit checkword, for a total of 88 DRAMs.

#### Table 1. MODE CONTROL FUNCTION

| MC <sub>1</sub> | MCo | Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | 0   | Refresh without Scrubbing. Refresh cycles are performed with only the Row Counter being used to generate addresses. In this mode, all four RASn outputs are active while the four CASn signals are kept HIGH.                                                                                                                                                                                                                                                                          |

| 0               | 1   | Refresh with Scrubbing/Initialize. During this mode, refresh cycles are done with both the Row and Column counters generating the addresses. MSEL is used to select between the Row and Column counter. All four RAS, go active in response to RASI, while only one CAS, output goes LOW in response to CASI. The Bank Counter keeps track of which CAS, output will go active. This mode is also used on system power-up so that the memory can be written with a known data pattern. |

| 1               | 0   | Read/Write. This mode is used to perform Read/Write cycles. Both the Row and Column addresses are latched and multiplexed to the address output lines using MSEL. SEL <sub>0</sub> and SEL <sub>1</sub> are decoded to determine which RAS <sub>0</sub> and CAS <sub>0</sub> will be active.                                                                                                                                                                                           |

| 1               | 1   | Clear Refresh Counter. This mode will clear the three refresh counters (Row, Column, and Bank) on the HIGH-to-LOW transition of RASI, putting them at the start of the refresh sequence. In this mode, all four RAS <sub>n</sub> are driven LOW upon receipt of RASI so that DRAM wake-up cycles may be performed.                                                                                                                                                                     |

Table 2. ADDRESS OUTPUT FUNCTION

| CS | MC <sub>1</sub> | MCo   | MSEL | Mode                      | MUX Output             |

|----|-----------------|-------|------|---------------------------|------------------------|

|    | 0               | 0     | Х    | Refresh without Scrubbing | Row Counter Address    |

|    | 0               |       | 1    | Refresh with Scrubbing    | Column Counter Address |

| 0  | "               | ' [   | 0    | Refresh with Scrubbing    | Row Counter Address    |

| v  | 4               | 0     | 1    | Read/Write                | Column Address Latch   |

|    | ,               | ا ٽ ا | 0    | nead/ wille               | Row Address Latch      |

|    | 1               | 1     | х    | Clear Refresh Counter     | Zero                   |

|    | 0               | 0     | Х    | Refresh without Scrubbing | Row Counter Address    |

|    | 0               | _     | 1    | Refresh with Scrubbing    | Column Counter Address |

| 1  | '               | ' [   | 0    | Heiresh with Scrubbing    | Row Counter Address    |

|    | 1               | 0     | Х    | Read/Write                | Zero                   |

|    | . 1             | 1     | Х    | Clear Refresh Counter     | Zero                   |

Table 3. RAS OUTPUT FUNCTION

| RASI | CS        | MC <sub>1</sub> | MC <sub>0</sub> | SEL <sub>1</sub> | SEL <sub>0</sub> | Mode                      | RAS <sub>0</sub> | RAS <sub>1</sub> | RAS <sub>2</sub> | RAS <sub>3</sub> |

|------|-----------|-----------------|-----------------|------------------|------------------|---------------------------|------------------|------------------|------------------|------------------|

| 0    | Х         | X               | ×               | ×                | ×                | ×                         | 1                | 1                | 1                | 1                |

|      |           | 0               | 0               | ×                | ×                | Refresh without Scrubbing | 0                | 0                | 0                | 0                |

|      |           | 0               | 1               | ×                | ×                | Refresh with Scrubbing    | 0                | 0                | 0                | 0                |

| 0    |           | 0 0             |                 | 0                | 1                | 1                         | 1                |                  |                  |                  |

|      | 0         | ١.              | 0               | 0                | 1                | Read/Write                | 1                | 0                | 1                | 1                |

|      |           | '               | "               | 1                | 0                | nead/ write               | 1                | 1                | 0                | 1                |

| '    |           |                 |                 | 1                | 1                | 1                         | 1                | 1                | 1                | 0                |

|      |           | 1               | 1               | ×                | X                | Clear Refresh Counter     | 0                | 0                | 0                | 0                |

|      |           | 0               | 0               |                  |                  | Refresh without Scrubbing | 0                | 0                | 0                | 0                |

|      |           | 0               | 1               | ×                | l x              | Refresh with Scrubbing    | 0                | 0                | 0                | 0                |

|      | 1 1 0 1 1 | ^               | Read/Write      | 1                | 1                | 1                         | 1                |                  |                  |                  |

|      |           | 1               | 1               |                  |                  | Clear Refresh Counter     | 0                | 0                | 0                | 0                |

Table 4. CAS OUTPUT FUNCTION

|      |    | Inp             | uts |                  |                  | Inte              | rnal              |                  | Out              | puts             |                  |

|------|----|-----------------|-----|------------------|------------------|-------------------|-------------------|------------------|------------------|------------------|------------------|

| CASI | CS | MC <sub>1</sub> | MCo | SEL <sub>1</sub> | SEL <sub>0</sub> | CNTR <sub>1</sub> | CNTR <sub>0</sub> | CAS <sub>0</sub> | CAS <sub>1</sub> | CAS <sub>2</sub> | CAS <sub>3</sub> |

|      |    | 0               | 0   | Х                | Х                | ×                 | ×                 | 1                | 1                | 1                | 1                |

|      |    |                 |     |                  |                  | 0                 | 0                 | 0                | 1                | 1                | 1                |

|      |    |                 | 1   | ×                | ,                | 0                 | 1                 | 1                | 0                | 1                | 1                |

|      |    | "               | '   | ^                | ×                | 1                 | 0                 | 1                | 1                | 0                | 1                |

|      | 0  |                 |     |                  |                  | 1                 | 1                 | 1                | 1                | 1                | 0                |

|      | U  |                 |     | 0                | 0                |                   |                   | 0                | 1                | 1                | 1                |

|      |    | 1               |     | 0                | 1                | 1 x               | <sub>×</sub>      | 1                | 0                | 1                | 1                |

|      |    | '               |     | 1                | 0                | 1 ^               | ^                 | 1                | 1                | 0                | 1                |

| 1    |    |                 |     | 1                | 1                | 1                 |                   | 1                | 1                | 1                | 0                |

|      |    | 1               | 1   | Х                | Х                | Х                 | ×                 | 1                | 1                | 1                | 1                |

|      |    | 0               | 0   | Х                | Х                | Х                 | X                 | 1                | 1                | 1                | 1                |

|      |    |                 |     |                  |                  | 0                 | 0                 | 0                | 1                | 1                | 1                |

|      |    |                 | 1   | ×                | ×                | 0                 | 1                 | 1                | 0                | 1 .              | 1                |

|      | 1  | "               | '   | _ ^              | ^                | 1                 | 0                 | 1                | 1                | 0                | 1                |

|      |    |                 |     |                  |                  | 1                 | 1                 | 1                | 1                | 1                | 0                |

|      |    | 1               | 0   | ×                | ×                | ×                 | ×                 | _                |                  |                  |                  |

|      |    | 1               | 1   | 1 ^              | <b>,</b>         |                   | ^                 | 1                | 1                | 1                | 1                |

| 0    | Х  | X               | X   | Х                | Х                | х                 | Х                 | 1                | 1                | 1                | 1                |

#### Input Latches

For those systems where addresses and data are multiplexed onto a single bus, the DMC has latches to hold the address information. The twenty input latches (Row, Column, and Bank Select) are transparent when Latch Enable (LE) is HIGH and will latch the input data meeting setup and hold time requirements when LE goes LOW. For systems where the processor has separate address and data buses, LE may be permanently enabled HIGH.

#### **Refresh Counters**

The two 9-bit refresh counters make it possible to support 128, 256, and 512 line refresh. External control over which type of refresh is to be performed allows the user maximum flexibility when choosing the refreshing scheme. Transparent (hidden), burst, synchronous or asynchronous refresh modes are all possible.

The refresh counters are advanced at the HiGH-to-LOW transition of RASI. This assures a stable counter output for the next refresh cycle.

#### Refresh with Error Correction

The Am2968A makes it possible to correct single-bit errors in parallel with performing dynamic RAM refresh cycles. This "scrubbing" of memory can be done periodically as a back-

ground routine when the memory is not being used by the processor. In a memory scrubbing cycle ( $MC_{1,0}=01$ ), the Row Address is strobed into all four banks with all four  $\overline{RAS}_n$  outputs going LOW.

The Column Address is strobed into a single bank with the activated  $\overline{CAS}_n$  output being selected by the Bank Counter. This type of cycle is used to simultaneously refresh the addressed row in all banks and read and correct (if necessary) one word in memory; thereby reducing the overhead associated with Error Detection and Correction. When doing refresh with memory scrubbing, both the Row and Column counters are multiplexed to the dynamic RAM address lines by using MSEL. Using the Refresh with Memory Scrubbing mode implies the presence of an error correcting facility such as the Am29C60A EDC unit. When doing refresh without scrubbing, all four RAS<sub>n</sub> still go LOW but the  $\overline{CAS}_n$  outputs are all driven HIGH so as not to activate the output lines of the memory.

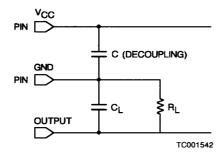

#### Decoupling

Due to the high switching speeds and high drive capability of the Am2968A, it is necessary to decouple the device for proper operation.  $1\mu F$  multilayer ceramic capacitors are recommended for decoupling (see Figure 1a). It is important to mount the capacitors as close as possible to the power pins (V<sub>CC</sub>, GND) to minimize lead inductance and noise. A ground plane is recommended.

Figures 1a

Decoupling Connection Diagrams

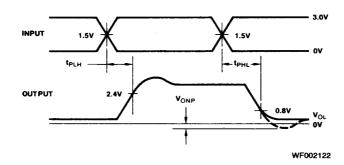

#### VONP

The guaranteed maximum undershoot voltage of the Am2968A is -0.5 volts. VONP is measured with respect to

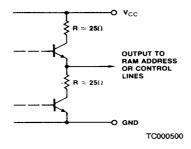

ground (Fig. 1b). Note that the ground of the capacitive load must be the same as for the  $V_{CC}$  pin(s). As loading increases,  $V_{ONP}$  will approach zero.

Figure 1b

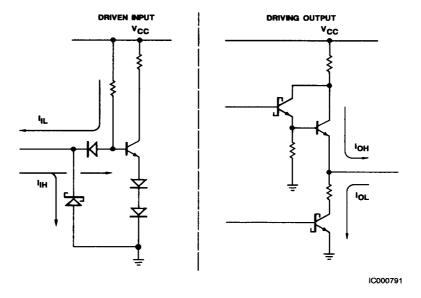

The RAM Driver symmetrical output design offers significant improvement over a standard Schottky output by providing a balanced drive output impedance ( $\approx\!25\Omega$  both HIGH and LOW), and by pulling up to MOS  $v_{OH}$  levels. External resistors, not required with the RAM Driver, protect standard Schottky drivers from error causing undershoot but also slow the output rise by adding to the internal R.

The RAM Driver is optimized to drive LOW at maximum speed based on safe undershoot control and to drive HIGH with a symmetrical speed characteristic. This is an optimum approach because the dominant RAM loading characteristic is input capacitance.

#### TYPICAL OUTPUT DRIVER

#### **APPLICATIONS**

### **Timing Control**

To obtain optimum performance and maximum design flexibility, the timing and control logic for the memory system has

been kept a separate function. For systems implementing Error Detection and Correction, the Am29C60A EDC unit may be used in 16-bit systems. The Am29C983 MBE serves as a data bus buffer.

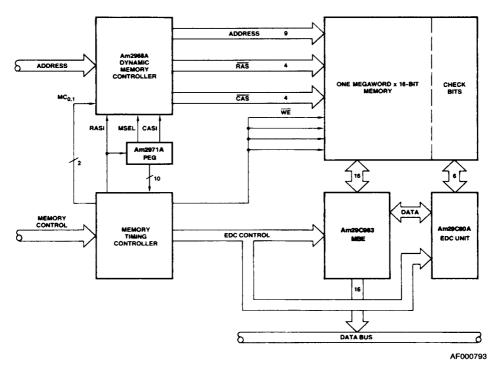

Figure 2a. One Megaword Dynamic Memory with Error Detection and Correction

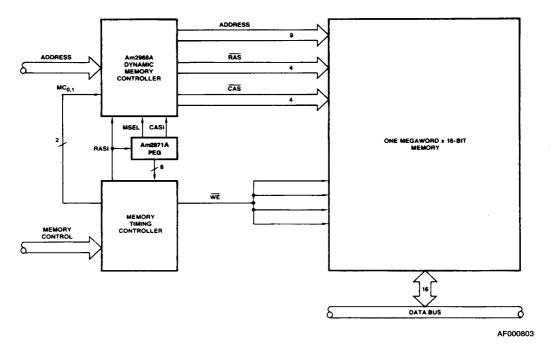

Figure 2b. One Megaword Dynamic Memory

## **Memory Expansion**

With a 9-bit address path, the Am2968A can control up to one megaword memory when using 256K dynamic RAMs. If a larger memory size is desired, the DMC's chip select  $\overline{\text{(CS)}}$

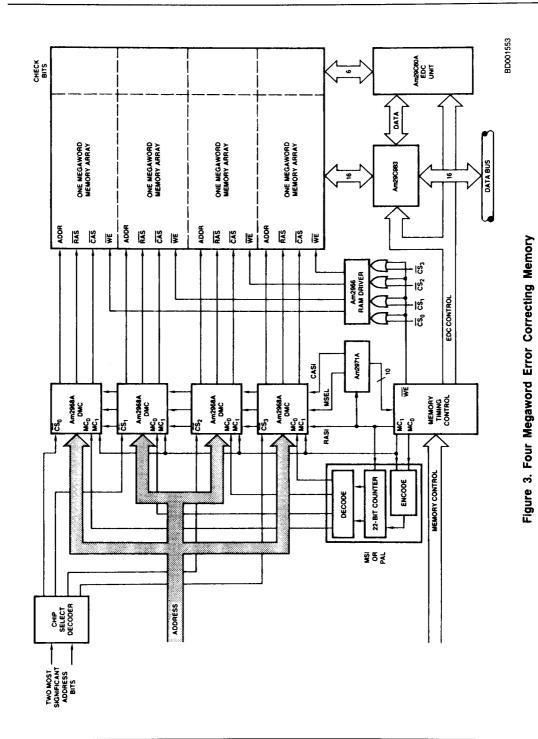

makes it easy to double the memory size by using two Am2968As. Memory can be increased in one megaword increments by adding another DMC unit. A four-megaword memory system implementing EDC is shown in Figure 3.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C              |

|------------------------------------------------|

| Ambient Temperature with                       |

| Power Applied55°C to +125°C                    |

| Supply Voltage to Ground Potential             |

| Continuous0.5 V to +7.0 V                      |

| DC Voltage Applied to Outputs For              |

| High Output State0.5 V to +V <sub>CC</sub> max |

| DC Input Voltage0.5 V to +5.5 V                |

| DC Input Current -30 mA to +50 mA              |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

| Commercial (C) Devices |              |

|------------------------|--------------|

| TA (Ambient)           | 0 to +70°C   |

| V <sub>CC</sub>        | 5.0 V ±10%   |

|                        | 4.50 V       |

| Max                    | 5.50 V       |

| Military* (M) Devices  |              |

| T <sub>C</sub> (Case)  | 55 to +125°C |

|                        | 5.0 V ±10%   |

|                        | 4.50 V       |

| Max                    | 5.50 V       |

|                        |              |

Operating ranges define those limits between which the functionality of the device is guaranteed.

DC CHARACTERISTICS over operating ranges unless otherwise specified; Included in Group A, Subgroup 1, 2, 3 tests unless otherwise noted.

| Parameters      | Descriptions                 | Test Con                                                                        | ditions (Note 1)       | Min. | Тур. | Max. | Units |

|-----------------|------------------------------|---------------------------------------------------------------------------------|------------------------|------|------|------|-------|

| VoH             | Output HIGH Voltage          | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | COMM                   | 2.7  |      | 1    | Volts |

|                 |                              | I <sub>OH</sub> = -1 mA                                                         |                        | 2.5  |      |      |       |

| V <sub>OL</sub> | Output LOW Voltage           | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OL</sub> = 1 mA |      |      | 0.5  | Volts |

| V <sub>IH</sub> | Input HIGH Level             | Guaranteed input lo                                                             |                        | 2.0  |      | 0.0  | Volts |

| V <sub>IL</sub> | Input LOW Level              | Guaranteed input logical-LOW voltage for all inputs                             |                        |      |      | 0.8  | Volts |

| VI              | Input Clamp Voltage          | V <sub>CC</sub> = Min., I <sub>IN</sub> = -18 mA                                |                        |      |      | -1.2 | Volts |

| lil.            | Input LOW Current            | V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = 0.4 V                              |                        |      | -400 | μΑ   |       |

| Ін              | Input HIGH Current           | V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = 2.4 V                              |                        |      |      | 20   | μΑ    |

| lj .            | Input HIGH Current           | V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = 5.5 V                              |                        |      |      | 100  | μΑ    |

| lozн            | Off-State Current            | V <sub>O</sub> = 2.4 V                                                          |                        |      |      | 50   | μΑ    |

| lozL            | Off-State Current            | V <sub>O</sub> = 0.4 V                                                          |                        | 1    |      | -50  | μΑ    |

| loL             | Output Sink Current          | V <sub>OL</sub> = 2.0 V                                                         |                        | 45   |      |      | mA    |

| Isc             | Output Short-Circuit Current | V <sub>CC</sub> = Max. (Note 2)                                                 | )                      | -60  | - 95 | -275 | mA    |

|                 |                              |                                                                                 | 25°C, 5 V              | 1    | 230  |      |       |

| lcc             | Power Supply Current         | $V_{CC} = Max.$ 0°C to +70°C                                                    |                        |      |      | 280  | mA.   |

|                 | 1                            |                                                                                 | -55°C to 125°C         |      |      | 295  |       |

Notes: 1. For conditions shown as Min or Max, use the appropriate value specified under Operating Range for the applicable device type.

<sup>\*</sup>Military Product 100% tested at  $T_C$  = 25°C, +125°C, and -55°C.

<sup>2.</sup> Not more than one output should be shorted at a time. Duration of the short-circuit test should not exceed one second.

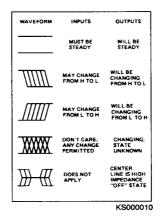

#### **KEY TO SWITCHING WAVEFORMS**

## SWITCHING TEST CIRCUITS

\*tpd specified at CL = 50 and 500 pF

## A. Capacitive Load Switching

B. Three-State Enable/Disable (for PLCC only)

#### SWITCHING TEST WAVEFORMS

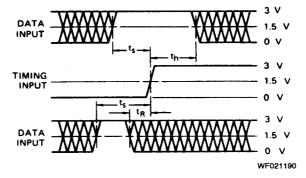

## A. Setup, Hold, and Release Times

Notes: 1. Diagram shown for HIGH data only. Output transition may be opposite sense.

2. Cross-hatched are "don't care" condition.

Am2968A

6-101

## SWITCHING TEST WAVEFORM (Cont'd.)

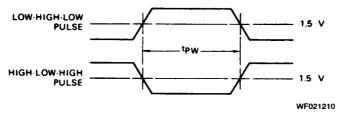

B. Puise Width

#### C. Output Drivers Levels

Note: Decoupling is needed for all AC tests

D. Three-State Control Levels (for Surface-mount packages only)

6-102

#### **GENERAL TEST NOTES**

Incoming test procedures on this device should be carefully planned, taking into account the complexity and power levels of the part. The following notes may be useful.

- Insure the part is adequately decoupled at the test head.

Large changes in V<sub>CC</sub> current as the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- 3. Do not attempt to perform threshold tests at high speed. Following an input transition, ground current may change by as much as 400 mA in 5-8 ns. Inductance in the ground

- cable may allow the ground pin at the device to rise by hundreds of millivolts momentarily.

- 4. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach  $V_{IL}$  or  $V_{IH}$  until the noise has settled. AMD recommends using  $V_{IL} \leqslant 0$  V and  $V_{IH} \geqslant 4$  V for AC tests.

- To simplify failure analysis, programs should be designed to perform DC, Function, and AC tests as three distinct groups of tests.

- Automatic tester hardware and handler add additional round trip A.C. delay to test measurements. Actual propagation delay testing may incorporate a correlation factor to negate the additional delay.

Am2968A 6-103

## SWITCHING CHARACTERISTICS over operation range for C<sub>L</sub> = 50 pF; included in Group A, Subgroup 9, 10, 11 tests unless otherwise noted

| Born | meter            | Parameter                                              | _                  |       | CO      |      |                                       |    |

|------|------------------|--------------------------------------------------------|--------------------|-------|---------|------|---------------------------------------|----|

|      | mbol             | Parameter<br>Description                               | Te<br>Condi        |       | Тур.    | Min. | Min. Max.                             |    |

| 1    | t <sub>PD</sub>  | A <sub>n</sub> to Q <sub>n</sub> Delay                 |                    |       | 12      | 3    | 20                                    | ns |

| 2    | ŧРD              | RASI to RAS <sub>n</sub>                               | ]                  |       | 10      | 3    | 18                                    | ns |

| 3    | t <sub>PD</sub>  | CASI to CAS <sub>n</sub>                               |                    |       | 8       | 3    | 17                                    | ns |

| 4    | teo              | MSEL to Q <sub>n</sub>                                 | ]                  |       | 12      | 3    | 20                                    | ns |

| 5    | teo              | MC <sub>n</sub> to Q <sub>n</sub>                      | ]                  |       | 15      | 5    | 24                                    | ns |

| 6    | t <sub>PD</sub>  | LE to RAS <sub>n</sub>                                 | Ì                  |       | 15      |      | 25                                    | ns |

| 7    | t <sub>PD</sub>  | LE to CAS,                                             | 1                  |       | 14      |      | 24                                    | ns |

| 8    | t <sub>PD</sub>  | MC <sub>n</sub> to RAS <sub>n</sub>                    | 1                  |       | 14      | 3    | 21                                    | ns |

| 9    | t <sub>PD</sub>  | MC <sub>n</sub> to CAS <sub>n</sub>                    | 1                  |       | 12      | 3    | 19                                    | ns |

| 10   | teo              | LE to Q <sub>n</sub>                                   | 1                  |       | 15      | 5    | 25                                    | ns |

| 11   | tews             | RASI, CASI                                             | 1                  |       | 10      | 20   |                                       | ns |

| 12   | <b>I</b> PWH     | RASI, CASI                                             | 1                  |       | 10      | 20   |                                       | ns |

| 13   | ts               | A <sub>n</sub> to LE                                   | 1 .                |       | 1       | 5    |                                       | ns |

| 14   | Ч                | A <sub>n</sub> to LE                                   | Fig. A a           | nd C  | 1       | 5    |                                       | ns |

| 15   | t <sub>PD</sub>  | CS to Q <sub>n</sub>                                   | 1                  |       | 16      |      | 23                                    | ns |

| 16   | t <sub>PD</sub>  | CS to RAS <sub>n</sub>                                 |                    |       | 12      |      | 20                                    | ns |

| 17   | t <sub>PD</sub>  | CS to CAS <sub>n</sub>                                 | ]                  |       | 11      |      | 19                                    | ns |

| 18   | t <sub>PD</sub>  | SEL <sub>n</sub> to RAS <sub>n</sub>                   | 1                  |       | 12      |      | 20                                    | ns |

| 19   | teo              | SEL <sub>n</sub> to CAS <sub>n</sub>                   |                    |       | 11      |      | 18                                    | ns |

| 20   | ts               | SEL <sub>n</sub> to LE                                 | 1                  |       | 1       | 5    |                                       | ns |

| 21   | tн               | SEL <sub>n</sub> to LE                                 | 1                  |       | 1       | 5    |                                       | ns |

| 22   | tskew            | $Q_n$ to $\overline{RAS}_n$ (MC <sub>n</sub> = 10)     |                    |       | 10      |      | 17                                    | ns |

| 23   | İSKEW            | $Q_n$ to $\overline{RAS}_n$ (MC <sub>n</sub> = 00, 01) |                    |       | 10      |      | 17                                    | ns |

| 24   | tskew            | Q <sub>n</sub> to RAS <sub>n</sub>                     |                    |       | 2       |      | 10                                    | ns |

| 25   | tskew            | Q <sub>n</sub> to CAS <sub>n</sub>                     |                    |       | 12      |      | 17                                    | ns |

| 26   | t <sub>H</sub>   | MC <sub>1</sub> to RASI                                | C <sub>L</sub> = 5 | 0 pF  | <b></b> | 5    |                                       | ns |

| 27   | ts               | CS to RASI                                             | C <sub>L</sub> = 5 |       |         | 5    | · · · · · · · · · · · · · · · · · · · | ns |

| 28   | ts               | SEL <sub>I</sub> to RASI                               | C <sub>L</sub> = 5 | 0 pF  |         | 5    |                                       | ns |

|      | t <sub>PLZ</sub> | Output Disable Time                                    |                    | S = 1 | 15      |      | 22                                    | ns |

|      | t <sub>PHZ</sub> | From LOW, HIGH (Note 1)                                | Fig. D and B       | S = 2 | 13      |      | 20                                    | ns |

|      | t <sub>PZL</sub> | Output Enable Time                                     | Cia David S        | S = 1 | 13      |      | 19                                    | ns |

|      | tрzн             | From LOW, HIGH (Note 1)                                | Fig. D and B       | S = 2 | 14      |      | 21                                    | ns |

| +    | VONP             | Output Undershoot Voltage (Note 2)                     | Fig. A and C       |       | 0       |      | -0.5                                  | ٧  |

### Notes:

<sup>1.</sup> Three-state (OE) applies only to PLCC package.

<sup>2.</sup> Not tested in production. Guaranteed by characterization data.

<sup>† =</sup> Not included in Group A testing

## **SWITCHING CHARACTERISTICS** over operating range for $C_L = 150$ pF; included in Group A, Subgroup 9, 10, 11 tests unless otherwise noted (Note 3)

|      |                  |                                                              | Test                    |      |           | CIAL AND<br>TARY |       |  |

|------|------------------|--------------------------------------------------------------|-------------------------|------|-----------|------------------|-------|--|

| Para | meter            | Description                                                  | Conditions              | Тур. | Min. Max. |                  | Units |  |

| 1    | tpD              | An to Qn Delay                                               |                         | 16   | 9         | 24               | ns    |  |

| 2    | teo              | RASI to RAS <sub>n</sub>                                     |                         | 15   | 9         | 23               | ns    |  |

| 3    | tPD              | CASI to CAS <sub>n</sub>                                     |                         | 14   | 9         | 22               | ns    |  |

| 4    | tPD              | MSEL to Qn                                                   |                         | 17   | 9         | 26               | ns    |  |

| 5    | tpD              | MC <sub>n</sub> to Q <sub>n</sub>                            |                         | 18   | 10        | 28               | ns    |  |

| 6    | tPD              | LE to RAS <sub>n</sub>                                       |                         | 20   |           | 28               | ns    |  |

| 7    | tPD              | LE to CAS <sub>n</sub>                                       |                         | 19   | Ĭ         | 27               | ns    |  |

| 8    | tPD              | MC <sub>n</sub> to RAS <sub>n</sub>                          |                         | 19   | 9         | 25               | ns    |  |

| 9    | tPD              | MC <sub>n</sub> to CAS <sub>n</sub>                          |                         | 17   | 9         | 23               | ns    |  |

| 10   | tPD              | LE to Qn                                                     |                         | 20   | 10        | 27               | ns    |  |

| 11   | tpwL             | RASI, CASI                                                   |                         | 10   | 20        |                  | ns    |  |

| 12   | t <sub>PWH</sub> | RASI, CASI                                                   |                         | 10   | 20        |                  | ns    |  |

| 13   | ts               | An to LE                                                     | Fig. A and C            | 1    | 5         |                  | ns    |  |

| 14   | tн               | An to LE                                                     |                         | 1    | 5         |                  | ns    |  |

| 15   | tPD              | CS to Q <sub>n</sub>                                         |                         | 19   |           | 27               | ns    |  |

| 16   | tPD              | CS to RAS <sub>n</sub>                                       |                         | 14   |           | 22               | ns    |  |

| 17   | tPD              | CS to CAS <sub>n</sub>                                       |                         | - 14 |           | 22               | ns    |  |

| 18   | tPD              | SELn to RASn                                                 |                         | 15   |           | 23               | ns    |  |

| 19   | tPD              | SELn to CASn                                                 |                         | 14   |           | 22               | ns    |  |

| 20   | ts               | SELn to LE                                                   |                         | 1    | 5         |                  | ns    |  |

| 21   | tн               | SELn to LE                                                   |                         | 1    | 5         |                  | ns    |  |

| 22   | tskew            | Q <sub>n</sub> to RAS <sub>n</sub> (MC <sub>n</sub> = 10)    |                         | 10   |           | 15               | ns    |  |

| 23   | tskew            | Q <sub>n</sub> to RAS <sub>n</sub> (MC <sub>n</sub> = 00,01) |                         | 10   |           | 17               | ns    |  |

| 24   | tskew            | Q <sub>n</sub> to RAS <sub>n</sub>                           |                         | 2    |           | 8                | ns    |  |

| 25   | tskew            | Q <sub>n</sub> to CAS <sub>n</sub>                           |                         | 15   |           | 17               | ns    |  |

| 26   | tH               | MC <sub>1</sub> to RASI                                      | C <sub>L</sub> = 150 pF |      | 5         |                  | ns    |  |

| 27   | ts               | CS to RASI                                                   | C <sub>L</sub> = 150 pF |      | 5         |                  | ns    |  |

| 28   | ts               | SEL1 to RASI                                                 | C <sub>L</sub> = 150 pF |      | 5         |                  | ns    |  |

| †    | VONP             | Output Undershoot Voltage                                    |                         | 0    |           | -0.5             | V     |  |

Note: 3. Production AC testing at 150pF load is not do ne. Performance at 150pF load is guaranted by characterization data and correlation to the 50pF and 500pF measurements.

<sup>+ =</sup> Not included in Group A tests

## **SWITCHING CHARACTERISTICS** over operating range for C<sub>L</sub> = 500 pF. Included in Group A, Subgroup 9, 10, 11 tests unless otherwise noted

| Parameter |                 | Description                                               | Test<br>Conditions      | Тур. | COMMERCIAL AND<br>MILITARY |      |       |

|-----------|-----------------|-----------------------------------------------------------|-------------------------|------|----------------------------|------|-------|

|           |                 |                                                           |                         |      | Min.                       | Max. | Units |

| 1         | tpD             | An to Qn Delay                                            |                         | 29   | 12                         | 40   | ns    |

| 2         | tPD             | RASI to RAS <sub>n</sub>                                  |                         | 28   | 12                         | 40   | ns    |

| 3         | tPD             | CASI to CAS <sub>n</sub>                                  |                         | 26   | 12                         | 37   | ns    |

| 4         | tPD             | MSEL to Qn                                                |                         | 29   | 12                         | 42   | ns    |

| 5         | tPD             | MC <sub>n</sub> to Q <sub>n</sub>                         |                         | 30   | 12                         | 44   | ns    |

| 6         | tpD             | LE to RAS <sub>n</sub>                                    |                         | 32   |                            | 46   | ns    |

| 7         | tPD             | LE to CAS <sub>n</sub>                                    |                         | 31   |                            | 45   | ns    |

| 8         | t <sub>PD</sub> | MC <sub>n</sub> to RAS <sub>n</sub>                       |                         | 30   | 12                         | 40   | ns    |

| 9         | tpD             | MC <sub>n</sub> to CAS <sub>n</sub>                       |                         | 28   | 12                         | 40   | ns    |

| 10        | tpD             | LE to Q <sub>n</sub>                                      |                         | 32   | 12                         | 46   | ns    |

| 11        | tpwL            | RASI, CASI                                                |                         | 10   | 20                         |      | ns    |

| 12        | tpwH            | RASI, CASI                                                |                         | 10   | 20                         |      | ns    |

| 13        | ts              | An to LE                                                  | Fig. A and C            | 1    | 5                          |      | ns    |

| 14        | tH              | An to LE                                                  |                         | 1    | 5                          |      | ns    |

| 15        | t <sub>PD</sub> | CS to Q <sub>n</sub>                                      |                         | 30   |                            | 45   | ns    |

| 16        | tPD             | CS to RAS <sub>n</sub>                                    |                         | 27   |                            | 40   | ns    |

| 17        | tPD             | CS to CAS <sub>n</sub>                                    |                         | 26   |                            | 38   | ns    |

| 18        | t <sub>PD</sub> | SEL <sub>n</sub> to RAS <sub>n</sub>                      |                         | 31   |                            | 42   | ns    |

| 19        | tpD             | SEL <sub>n</sub> to CAS <sub>n</sub>                      |                         | 28   |                            | 41   | ns    |

| 20        | ts              | SELn to LE                                                |                         | 1    | 5                          |      | ns    |

| 21        | ŧн              | SELn to LE                                                |                         | 1    | 5                          |      | ns    |

| 22        | tskew           | Q <sub>n</sub> to RAS <sub>n</sub> (MC <sub>n</sub> = 10) |                         | 10   |                            | 18   | ns    |

| 23        | tskew           | $Q_n$ to $\overline{RAS}_n$ (MC <sub>n</sub> = 00,01)     |                         | 10   |                            | 18   | ns    |

| 24        | tskew           | Q <sub>n</sub> to RAS <sub>n</sub>                        |                         | 2    |                            | 8    | ns    |

| 25        | tSKEW           | Q <sub>n</sub> to CAS <sub>n</sub>                        |                         | 15   |                            | 20   | ns    |

| 26        | tн              | MC <sub>1</sub> to RASi                                   | C <sub>L</sub> = 500 pF |      | 5                          |      | ns    |

| 27        | ts              | CS to RASI                                                | C <sub>L</sub> = 500 pF |      | 5                          |      | ns    |

| 28        | ts              | SEL1 to RASI                                              | C <sub>L</sub> = 500 pF |      | 5                          | 1    | ns    |

| +         | VONP            | Output Undershoot Voltage                                 |                         | 0    |                            | -0.5 | V     |

<sup>† =</sup> Not included in Group A tests

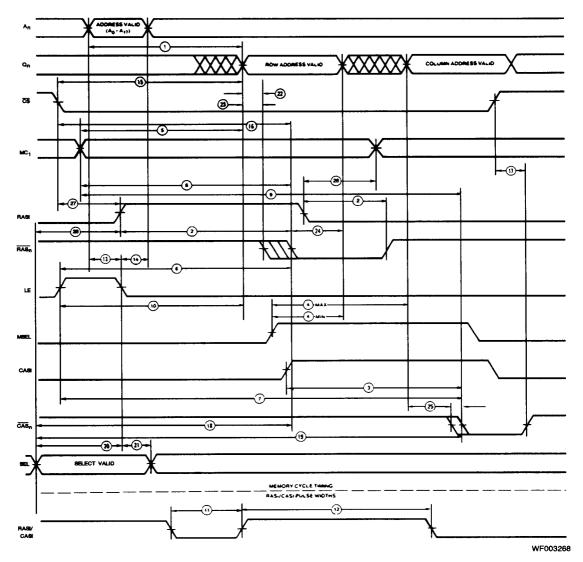

## **SWITCHING WAVEFORMS**

Am2968A Dynamic Memory Controller Timing

Am2968A 6-107

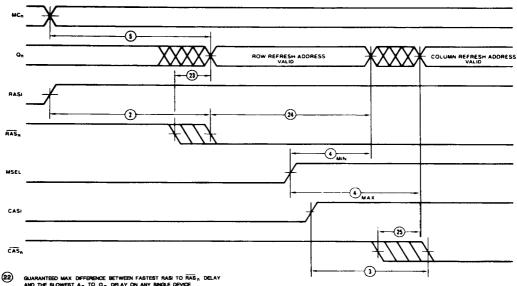

#### **MEMORY CYCLE TIMING**

The relationship between DMC specifications and system timing requirements are shown in Figure 4.  $T_1$ ,  $T_2$  and  $T_3$ represent the minimum timing requirements at the DMC inputs to guarantee that RAM timing requirements are met and that maximum system performance is achieved.

The minimum requirement for T1, T2 and T3 are as follows:

T1 Min. = tASR + t22

T2 Min. = tRAH + t24

T3 Min. = T2 + t25 + tASC

See RAM data sheet for applicable values for  $t_{\mbox{\scriptsize RAH}}$ ,  $t_{\mbox{\scriptsize ASC}}$  and

Figure 4. Memory Cycle Timing a. Specifications Applicable to Memory Cycle Timing  $(MC_n = 1, 0)$

- 22)

WF003285

Am2968A 6-108

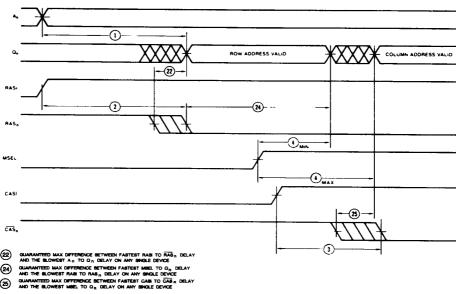

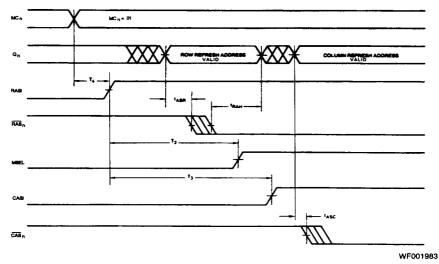

The timing relationships for refresh are shown in Figure 5.

T4 Min. = tASR + t23

Figure 5. Refresh Cycle Timing a. Specifications Applicable to Refresh Cycle Timing ( $MC_n = 00, 01$ )

- GUARANTEED MAX DIFFERENCE BETWEEN FASTEST RASI TO  $\overline{\rm RAS}_{\,\Omega}$  DELAY AND THE SLOWEST  $\rm A_{\,\Omega}$  TO  $\rm Q_{\,\Omega}$  DELAY ON ANY SINGLE DEVICE

- Guaranteed Max difference between fastest rasi to  $\overline{\text{Ras}}_n$  delay and the slowest MCn to  $\text{O}_n$  delay on any single device **(23)**

- Guaranteed max difference between fastest migel to  $\mathbf{Q}_0$  delay and the slowest rasi to  $\overline{\text{MAS}}_0$  delay on any single device

- GUARANTEED MAX DIFFERENCE BETWEEN FASTEST CASI TO CAS, DELAY AND THE SLOWEST MISEL TO  $\mathbf{Q}_{n}$  DELAY ON ANY SINGLE DEVICE

WE003273

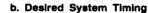

b. Desired Timing: Refresh with Scrubbing

Am2968A

6-109

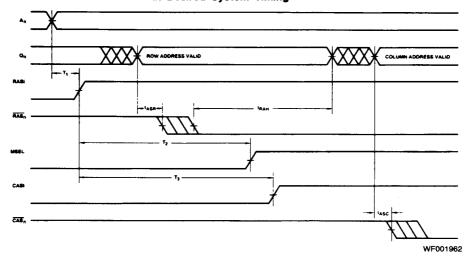

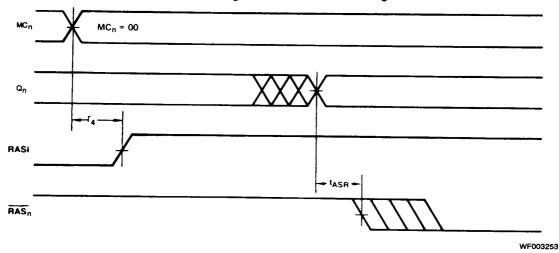

## REFRESH CYCLE TIMING

Figure 5. Refresh Cycle Timing (Cont'd.)

### c. Desired Timing: Refresh without Scrubbing

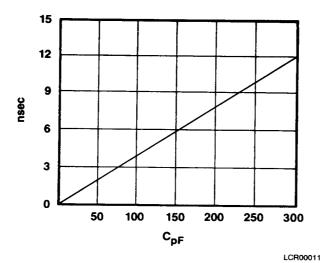

## NANOSECONDS VERSUS PICOFARADS

To help calculate how the AC performance of the DMC will vary for capacitive loads other than 50, 150, and 500pF refer to the table below.

Example: For a system capacitive load of 250pF, add the delay associated with 100pF from the table to the AC specs done at 150pF.

# Change in Propagation Delay versus Loading Capacitance (TYPICAL)

6-110 Am2968A

## INPUT/OUTPUT CURRENT DIAGRAM

Am2968A 6-111