### FLF10 Series

### High Density FLASH Memory Card 32, 64, 96, 128, 160, 192 MEGABYTE

### **General Description**

WEDC's Flash memory cards - FLF10 Series - offer high density linear Flash memory for code and data storage, high performance disk emulation, mobile PC and embedded applications.

The WEDC FLF10 series is based on Intel's Multi Level Cell (MLC) Flash memory technology, providing high density Flash components at a significantly lower cost per megabyte. MLC technology allows for two bits of information to be stored in a single cell. This leads to reduced die size and reduced cost per megabyte.

WEDC's FLF10 series cards are built with Intel's 128Mb memory component, 28F128J3A, with a manufacturer/device ID of  $89/18_{\text{H}}$ . The FLF10 series is available in densities of 32, 64, 96, 128, 160, and 192MB.

WEDC's FLF10 series provides densities from 32MB to 192MB, in 32MB increments. The cards up to the 64MB density operate in the regular PCMCIA mode. The densities beyond the 64MB density are implemented using a "paging scheme", which is also supported by the PCMCIA standard. By writing a page address to the Configuration Option Register (address 4000H), an additional page of memory can be accessed. The current FLF10 series supports densities to 192MB: total of 3 pages: page 0 := 64MB, page 1 := 64MB, and page 2 := 64MB.

The FLF10 series card operates in a wide, universal voltage range, from 3V to 5V, allowing full "plug and play" functionality and upgrade solutions in all mobile, battery powered applications.

Each memory component in the card also has a 128-bit Protection Register, containing 64 bits of User Programmable OTP (One Time Programmable) Cells. These cells can be programmed with a numeric security measure, such as an electronic signature.

To provide a 16 bit word wide access supported by the PCMCIA standard, devices are paired on the card. Therefore, the Flash array is structured in 128K word (256kB) blocks. Write, read and block erase operations can be performed as either a word or byte wide operation.

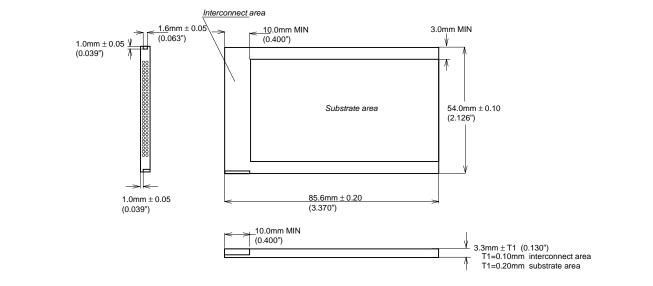

The FLF10 series cards conform to the PC Card 95 Standard supported by PCMCIA and JEIDA, providing electrical and physical compatibility. The PC Card form factor offers an industry standard pinout and mechanical outline, allowing density upgrades without system design changes.

WEDC's standard cards are shipped with WEDC's Flash Logo. Cards are also available with blank housings (no Logo). The blank housings are available in both, a recessed (for label) or flat housing. Please contact your WEDC sales representative for further information on Custom artwork.

#### **Features**

• Low cost, high density Linear Flash Card

• Universal 3V to 5V operating range providing full "plug and play" exchangeability between different systems

• Based on Intel 28F128J3A (MLC) Components

- Fast Read Performance

- 250ns Maximum Access Time

- (200ns optional)

•PCMCIA compatible - x8/x16 Data Interface

• 32-Byte Write Buffer (per Memory Device)

- 6µs per Byte Effective Write Time

•128-bit Protection Register (per Memory Device)

-64-bit Unique Device Identifier -64-bit User Programmable OTP Cells

•Cross-Compatible Command Support

- Common Flash Interface (CFI)

- Intel Basic Command Set

- Scaleable Command Set

- Power-Down Mode

- Reset, Power Down Registers

- 100,000 Erase Cycles per Block

- 128K word symmetrical Block Architecture

- PC Card Standard Type I Form Factor

#### **FLF10 Series**

# FLF10 Flash Card based on Strata Flash 28F128J3A

### **FLF10 Series**

### <u>Pinout</u>

| Pin | Signal name | I/O | Function       | Active |

|-----|-------------|-----|----------------|--------|

| 1   | GND         |     | Ground         |        |

| 2   | DQ3         | I/O | Data bit 3     |        |

| 3   | DQ4         | I/O | Data bit 4     |        |

| 4   | DQ5         | I/O | Data bit 5     |        |

| 5   | DQ6         | I/O | Data bit 6     |        |

| 6   | DQ7         | I/O | Data bit 7     |        |

| 7   | CE1#        | Ι   | Card enable 1  | LOW    |

| 8   | A10         | Ι   | Address bit 10 |        |

| 9   | OE#         | Ι   | Output enable  | LOW    |

| 10  | A11         | Ι   | Address bit 11 |        |

| 11  | A9          | Ι   | Address bit 9  |        |

| 12  | A8          | Ι   | Address bit 8  |        |

| 13  | A13         | Ι   | Address bit 13 |        |

| 14  | A14         | Ι   | Address bit 14 |        |

| 15  | WE#         | Ι   | Write Enable   | LOW    |

| 16  | RDY/BSY#    | 0   | Ready/Busy     | LOW(1) |

| 17  | Vcc         |     | Supply Voltage |        |

| 18  | Vpp1        |     | Prog. Voltage  | N.C.   |

| 19  | A16         | Ι   | Address bit 16 |        |

| 20  | A15         | Ι   | Address bit 15 |        |

| 21  | A12         | Ι   | Address bit 12 |        |

| 22  | A7          | Ι   | Address bit 7  |        |

| 23  | A6          | Ι   | Address bit 6  |        |

| 24  | A5          | Ι   | Address bit 5  |        |

| 25  | A4          | Ι   | Address bit 4  |        |

| 26  | A3          | Ι   | Address bit 3  |        |

| 27  | A2          | Ι   | Address bit 2  |        |

| 28  | A1          | Ι   | Address bit 1  |        |

| 29  | A0          | Ι   | Address bit 0  |        |

| 30  | DQ0         | I/O | Data bit 0     |        |

| 31  | DQ1         | I/O | Data bit 1     |        |

| 32  | DQ2         | I/O | Data bit 2     |        |

| 33  | WP          | 0   | Write Potect   | HIGH   |

| 34  | GND         |     | Ground         |        |

| Pin | Signal name | I/O | Function            | Active |

|-----|-------------|-----|---------------------|--------|

| 35  | GND         |     | Ground              |        |

| 36  | CD1#        | 0   | Card Detect 1       | LOW    |

| 37  | DQ11        | I/O | Data bit 11         |        |

| 38  | DQ12        | I/O | Data bit 12         |        |

| 39  | DQ13        | I/O | Data bit 13         |        |

| 40  | DQ14        | I/O | Data bit 14         |        |

| 41  | DQ15        | Ι   | Data bit 15         |        |

| 42  | CE2#        | Ι   | Card Enable 2       | LOW    |

| 43  | VS1         | 0   | Voltage Sense 1     | NC (2) |

| 44  | RFU         |     | Reserved            |        |

| 45  | RFU         |     | Reserved            |        |

| 46  | A17         | Ι   | Address bit 17      |        |

| 47  | A18         | Ι   | Address bit 18      |        |

| 48  | A19         | Ι   | Address bit 19      |        |

| 49  | A20         | Ι   | Address bit 20      |        |

| 50  | A21         | Ι   | Address bit 21      |        |

| 51  | Vcc         |     | Supply Voltage      |        |

| 52  | Vpp2        |     | Prog. Voltage       | N.C.   |

| 53  | A22         | Ι   | Address bit 22      |        |

| 54  | A23         | Ι   | Address bit 23      |        |

| 55  | A24         | Ι   | Address bit 24      |        |

| 56  | A25         | Ι   | Address bit 25      |        |

| 57  | VS2         | 0   | Voltage Sense 2     | N.C.   |

| 58  | RST         | Ι   | Card Reset          | HIGH   |

| 59  | Wait#       | 0   | Extended Bus cycle  | LOW(3) |

| 60  | RFU         |     | Reserved            |        |

| 61  | REG#        | Ι   | Attrib Mem Select   |        |

| 62  | BVD2        | 0   | Bat. Volt. Detect 2 | (3)    |

| 63  | BVD1        | 0   | Bat. Volt. Detect 1 | (3)    |

| 64  | DQ8         | I/O | Data bit 8          |        |

| 65  | DQ9         | I/O | Data bit 9          |        |

| 66  | DQ10        | 0   | Data bit 10         |        |

| 67  | CD2#        | 0   | Card Detect 2       | LOW    |

| 68  | GND         |     | Ground              |        |

WHITE ELECTRONIC DESIGNS

#### Notes:

1. RDY/BSY signal is an open drain type output, pull-up resistors are required on the host side.

2. VS1 is connected to GND.

3. Wait#, BVD1 and BVD2 are internally connected to Vcc by resistors for compatibility.

## **Mechanical**

## **Card Signal Description**

| Symbol       | Туре         | Name and Function                                                             |

|--------------|--------------|-------------------------------------------------------------------------------|

| A0 - A25     | INPUT        | ADDRESS INPUTS: A0 through A25 enable direct addressing of up                 |

|              |              | to 64MB of memory on the card. Signal A0 is not used in word access           |

|              |              | mode. A25 is the most significant bit                                         |

| DQ0 - DQ15   | INPUT/OUTPUT | <b>DATA INPUT/OUTPUT:</b> DQ0 THROUGH DQ15 constitute the                     |

|              |              | bi-directional databus. DQ15 is the MSB.                                      |

| CE1 #, CE2 # | INPUT        | <b>CARD ENABLE 1 AND 2:</b> CE1 # enables even byte accesses, CE2 #           |

|              |              | enables odd byte accesses. Multiplexing A0, CE1 # and CE2 # allows 8-         |

|              |              | bit hosts to access all data on $DQ0$ - $DQ7$ (see truth table).              |

| OE#          | INPUT        | <b>OUTPUT ENABLE:</b> A ctive low signal gating read data from the            |

|              |              | memory card.                                                                  |

| WE#          | INPUT        | <b>WRITE ENABLE:</b> Active low signal gating write data to the memory        |

|              |              | card.                                                                         |

| RDY/BSY#     | OUTPUT       | <b>READY/BUSY OUTPUT:</b> Indicates status of internally timed erase          |

|              |              | or program algorithms. A high output indicates that the card is ready to      |

|              |              | accept accesses. A low output indicates that one or more devices in the       |

|              |              | memory card are busy with internally timed erase or write activities.         |

| CD1 #, CD2 # | OUTPUT       | CARD DETECT 1 and 2: Provide card insertion detection. These                  |

| 021,022      |              | signals are internally connected to ground on the card. The host shall        |

|              |              | monitor these signals to detect card insertion. Pulled up on host side.       |

| WP           | OUTPUT       | <b>WRITE PROTECT:</b> Write protect reflects the status of the Write          |

|              | 001101       | Protect switch on the memory card. WP set to high = write protected,          |

|              |              | providing internal hardware write lockout to the Flash array.                 |

|              |              | If card does not include optional write protect switch, this signal will be   |

|              |              | pulled low internally indicating write protect = "off".                       |

| VPP1, VPP2   | N.C.         | PROGRAMMING VOLTAGES: Not connected                                           |

| VCC          | 11.0.        | <b>CARD POWER SUPPLY:</b> Universal 3V to 5V Supply                           |

| GND          |              | CARD GROUND                                                                   |

| REG #        | INPUT        | <b>ATTRIBUTE MEMORY SELECT:</b> Active low signal, enables                    |

| KEG#         |              | access to attribute memory space, occupied by the Card Information            |

|              |              | Structure (CIS) and Card Registers.                                           |

| RST          | INPUT        | <b>RESET:</b> Active high signal for placing card in Power-on default state.  |

| K31          | INPUT        |                                                                               |

|              |              | Reset can be used as a Power-Down control for the memory array.               |

| WAIT#        | OUTPUT       | <b>WAIT:</b> This signal is pulled high internally for compatibility. No wait |

|              |              | states are generated.                                                         |

| BVD1, BVD2   | OUTPUT       | <b>BATTERY VOLTAGE DETECT:</b> These signals are pulled high to               |

|              |              | maintain SRAM card compatibility.                                             |

| VS1, VS2     | OUTPUT       | <b>VOLTAGE SENSE:</b> Notifies the host socket of the card's VCC              |

|              |              | requirements. VS1 grounded and VS2 is open to indicate a 3/5V card.           |

| RFU          |              | RESERVED FOR FUTURE USE                                                       |

| N.C.         |              | NO INTERNAL CONNECTION TO CARD: pin may be driven                             |

|              |              | or left floating.                                                             |

## **Functional Truth Table**

| READ function         |      | READ function |    |     |     |      | Common Memory |           |      | Attribute Memory |           |  |

|-----------------------|------|---------------|----|-----|-----|------|---------------|-----------|------|------------------|-----------|--|

| Function Mode         | /CE2 | /CE1          | A0 | /OE | /WE | /REG | D15-D8        | D7-D0     | /REG | D15-D8           | D7-D0     |  |

| Standby Mode          | Н    | Н             | Х  | Х   | Х   | Х    | High-Z        | High-Z    | Х    | High-Z           | High-Z    |  |

| Byte Access (8 bits)  | Н    | L             | L  | L   | Н   | Н    | High-Z        | Even-Byte | L    | High-Z           | Even-Byte |  |

|                       | Н    | L             | Н  | L   | Н   | Н    | High-Z        | Odd-Byte  | L    | High-Z           | Not Valid |  |

| Word Access (16 bits) | L    | L             | Х  | L   | Н   | Н    | Odd-Byte      | Even-Byte | L    | Not Valid        | Even-Byte |  |

| Odd-Byte Only Access  | L    | Н             | Х  | L   | Н   | Н    | Odd-Byte      | High-Z    | L    | Not Valid        | High-Z    |  |

| WRITE function        |      |               |    |     |     |      |               |           |      |                  |           |  |

| Standby Mode          | Н    | Н             | Х  | Х   | Х   | Х    | Х             | Х         | Х    | Х                | Х         |  |

| Byte Access (8 bits)  | Н    | L             | L  | Н   | L   | Н    | Х             | Even-Byte | L    | Х                | Even-Byte |  |

|                       | Н    | L             | Н  | Н   | L   | Н    | Х             | Odd-Byte  | L    | Х                | Х         |  |

| Word Access (16 bits) | L    | L             | Х  | Н   | L   | Н    | Odd-Byte      | Even-Byte | L    | Х                | Even-Byte |  |

| Odd-Byte Only Access  | L    | Н             | Х  | Н   | L   | Н    | Odd-Byte      | Х         | L    | Х                | Х         |  |

### FLF10 Series

#### **Card Interface**

The FLF10 series flash card complies with PC Card standard (PCMCIA, March 1997). While maintaining PCMCIA compatibility, the FLF10 series card has integrated special features to extend functionality. The card has built-in 2 control registers:

- Configuration Option Register (COR) Address =  $4000_{\rm h}$

- Configuration and Status Register (CSR)  $Address = 4002_{h}$

**COR register:** provides a soft reset function (bit D7) and additional page bits (bits D0 and D1) to extend card capacity beyond 64MB.

#### SReset

As defined by PCMCIA, setting the SReset bit to 1, places the card in the reset state. During this state all memory devices are placed in power down mode, minimizing power consumption. Returning this bit to 0 leaves the reset cycle and places the card in the same condition as following a power up or hardware reset. This bit must be cleared to 0, to access any device on the card.

Complete soft reset cycle must consist of a 2 step write sequence to the SReset bit:

- 1. Initialization: write 1 to SReset

- reset cycle begin

- memory devices enters Power-Down mode aborting all operations and clearing all registers.

- 2. Write 0 to SReset

- Reset cycle ends

- memory devices and registers enter power on default state

The card can also be placed in Power Down mode by activating the Reset signal (pin58) or by controlling the bit D2 (PwrDwn) in the CSR register.

#### LevlRequest

Not supported

#### **Configuration Index**

Configuration Index bits (D0 - D5) are defined to provide address extension bits -page address, to extend card capacity beyond 64MB.

Only bits D0 and D1 are supported:

- D1D0 set to  $00_{bin} (0_H)$  selects page 0

- D1D0 set to  $01_{bin} (1_H)$  selects: page 1

- D1D0 set  $to10_{bin}$  (2<sub>H</sub>) selects: page 2

- D1D0 set to11<sub>bin</sub> (3<sub>H</sub>) selects: page 3 (No Memory Access)

D1D0 is set to the value of  $00_{bin} (0_H)$  during any reset cycle (Power on Reset, Hardware Reset, and SReset). Attempting to access page 3 will not result in the writing or reading of data.

**CSR register:** provides a power control of the memory array. Only bit D2 is supported; all other bits are "don't care"

#### PwrDwn

Writing 1 to PwrDwn bit (D2) forces each memory device on the card into a reset/power down mode by asserting all the devices RP# pins. Writing 0 to the bit returns the array to stand by mode.

The Card Information Structure (CIS) contains information about Register addressing and Memory structure.

Cards with memory capacity up to 64MB do not support Configuration Index bits.

#### Notes:

- 1. Reading from undefined address location or unsupported bits will return random data.

- 2. Writing to undefined address location may result in card malfunctioning due to limited address decoding.

- 3. See block diagram for more details about control registers.

Writing commands to the CUI enables reading of device data, query, identifier codes, inspection and clearing of the status register, and, when  $V_{PEN} = V_{PENH}$ , block erasure, program, and lock-bit configuration.

The Block Erase command requires appropriate command data and an address within the block to be erased. The Byte/Word Program command requires the command and address of the location to be written. Set Block Lock-Bit commands require the command and block within the device to be locked. The Clear Block Lock-Bits command requires the command and address within the device.

The CUI does not occupy an addressable memory location. It is written when the device is enabled and WE# is active. The address and data needed to execute a command are latched on the rising edge of WE# or the first edge of  $CE_0$ ,  $CE_1$ , or  $CE_2$  that disables the device. Standard microprocessor write timings are used.

# For information regarding modes of operation, commands, and programming details for the memory components, please consult the Intel 28F128J3A data sheet.

# Absolute Maximum Ratings (2)

Operating Temperature TA (ambient) Commercial Storage Temperature Voltage on any pin relative to VSS VCC supply Voltage relative to VSS

0°C to +60 °C -10°C to +70 °C -0.5V to VCC+0.5V -0.5V to +7.0V

#### Note:

Stress greater than those listed under "Absolute Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended Supply Voltage**

| VCC  | Tolerance  |

|------|------------|

| 3.3V | $\pm 0.3V$ |

| 5.0V | ± 0.5V     |

Note: The FLF10 Series Card will function at either 3.3V or 5.0V

### DC Characteristics (1)

| Symbol | Parameter              | Density<br>(Mbytes)       | Notes | Typ <sup>(3)</sup> | Max  | Units | Test Conditions                |

|--------|------------------------|---------------------------|-------|--------------------|------|-------|--------------------------------|

| ICCR   | VCC Read Current       | 32,64,96,128,<br>160,192  |       | 70                 | 110  | mA    | VCC = VCCmax<br>tcycle = 200ns |

| ICCW   | VCC Program<br>Current | 32,64,96,128,<br>160, 192 |       | 70                 | 120  | mA    | 2 memory devices               |

| ICCE   | VCC Erase Current      | 32,64,96,128,<br>160,192  |       | 70                 | 140  | mA    | 2 memory devices               |

| ICCD   | VCC Power-down         | 32                        | 2     | 100                | 200  | μA    | VCC = VCCmax                   |

|        | Current                | 64                        |       | 200                | 400  |       | Control Signals = VCC          |

|        |                        | 96                        |       | 300                | 600  |       | Reset = VCC (active)           |

|        |                        | 128                       | -     | 400                | 800  |       |                                |

|        |                        | 160                       | -     | 500                | 1000 |       |                                |

|        |                        | 192                       |       | 600                | 1200 |       |                                |

| ICCS   | VCC Standby            | 32                        | 2     | 0.1                | 0.2  | mA    | VCC = VCCmax                   |

| (CMOS) | Current                | 64                        |       | 0.2                | 0.4  |       | Control Signals = VCC          |

|        |                        | 96                        |       | 0.3                | 0.6  |       |                                |

|        |                        | 128                       |       | 0.4                | 0.8  |       |                                |

|        |                        | 160                       |       | 0.5                | 1.0  |       | Reset = 0V (not active)        |

|        |                        | 192                       |       | 0.6                | 1.2  |       |                                |

CMOS Test Conditions: VCC = 5V  $\pm$  5%, VIL = VSS  $\pm$  0.2V, VIH = VCC  $\pm$  0.2V

#### Notes:

- 1. All currents are RMS values unless otherwise specified. ICCR, ICCW and ICCE are based on Word wide operations (2 memory devices activated).

- 2. Control Signals:  $CE_1$ #,  $CE_2$ #, OE#, WE#.

- 3. Typical: VCC = 5V or VCC = 3V, T =  $+25^{\circ}C$ .

#### VCC = 3.3V or 5V

| Symbol | Parameter                         | Notes | Min     | Max         | Units | Test Conditions                 |

|--------|-----------------------------------|-------|---------|-------------|-------|---------------------------------|

| ILI    | Input Leakage Current             | 1, 2  |         | ±20         | μA    | VCC = VCCMAX<br>Vin =VCC or GND |

| ILO    | Output Leakage Current            | 1     |         | <u>+</u> 20 | μA    | VCC = VCCMAX<br>Vin =VCC or GND |

| VIL    | Input Low Voltage                 | 1     | 0       | 0.8         | V     |                                 |

| VIH    | Input High Voltage                | 1     | 0.7xVCC | VCC+0.5     | V     |                                 |

| VOL    | Output Low Voltage                | 1     |         | 0.4         | V     | IOL = 3.2mA                     |

| VOH    | Output High Voltage               | 1     | VCC-0.4 | VCC         | V     | IOH = -2.0mA                    |

| VLKO   | VCC Erase/Program<br>Lock Voltage | 1     | 2.0     |             | V     |                                 |

#### Notes:

1. Values are the same for byte and word wide modes for all card densities.

2. Exception: Leakage current on control signals with internal pull up resistors (see block diag) will be < 500μA when VIN=GND.

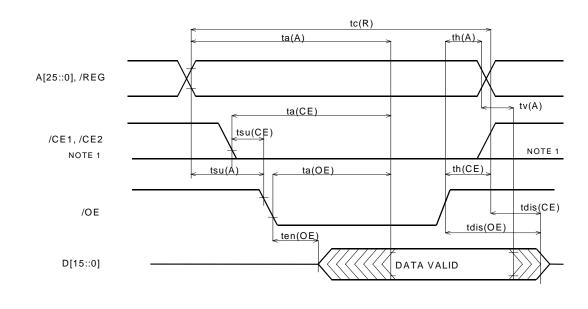

## **AC Characteristics**

Read Timing Parameters

VCC = 3.3V or 5V

|                        |                                                  | 200ns |     | 250ns |     |      |

|------------------------|--------------------------------------------------|-------|-----|-------|-----|------|

| SYMBOL<br>(PCMCIA)     | Parameter                                        | Min   | Max | Min   | Max | Unit |

| t <sub>c</sub> (R)     | Read Cycle Time                                  | 200   |     | 250   |     | ns   |

| t <sub>a</sub> (A)     | Address Access Time                              |       | 200 |       | 250 | ns   |

| t <sub>a</sub> (CE)    | Card Enable Access Time                          |       | 200 |       | 250 | ns   |

| t <sub>a</sub> (OE)    | Output Enable Access Time                        |       | 90  |       | 100 | ns   |

| t <sub>su</sub> (A)    | Address Setup Time                               |       | 20  |       | 30  | ns   |

| t <sub>su</sub> (CE)   | Card Enable Setup Time                           |       | 0   |       | 0   | ns   |

| t <sub>h</sub> (A)     | Address Hold Time                                |       | 20  |       | 20  | ns   |

| t <sub>h</sub> (CE)    | Card Enable Hold Time                            |       | 20  |       | 20  | ns   |

| t <sub>v</sub> (A)     | Output Hold from Address<br>Change               |       | 0   |       | 0   | ns   |

| t <sub>dis</sub> (CE)  | Output Disable Time from CE#                     |       | 90  |       | 100 | ns   |

| t <sub>dis</sub> (OE)  | Output Disable Time from OE#                     |       | 90  |       | 100 | ns   |

| t <sub>en</sub> (CE)   | Output Enable Time from CE#                      | 5     |     | 5     |     | ns   |

| t <sub>en</sub> (OE)   | Output Enable Time from OE#                      | 5     |     | 5     |     | ns   |

| t <sub>rec</sub> (RST) | Power Down recovery to Output<br>Delay. VCC = 5V |       | 500 |       | 500 | ns   |

**Note:** AC timing diagrams and characteristics are guaranteed to meet or exceed PCMCIA 2.1 specifications.

### Read Timing Diagram

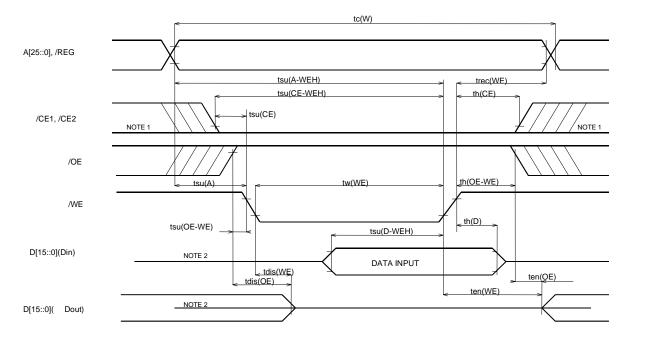

Write Timing Parameters

VCC = 3.3V or 5V

|                          |                                 | 200ns |     | 250ns |     |      |

|--------------------------|---------------------------------|-------|-----|-------|-----|------|

| SYMBOL<br>(PCMCIA)       | Parameter                       | Min   | Max | Min   | Max | Unit |

| t <sub>c</sub> W         | Write Cycle Time                | 200   |     | 250   |     | ns   |

| t <sub>w</sub> (WE)      | Write Pulse Width               | 120   |     | 150   |     | ns   |

| t <sub>su</sub> (A)      | Address Setup Time              | 20    |     | 30    |     | ns   |

| t <sub>su</sub> (A-WEH)  | Address Setup Time for WE#      | 140   |     | 180   |     | ns   |

| t <sub>su</sub> (CE-WEH) | Card Enable Setup Time for WE#  | 140   |     | 180   |     | ns   |

| t <sub>su</sub> (D-WEH)  | Data Setup Time for WE#         | 60    |     | 80    |     | ns   |

| t <sub>h</sub> (D)       | Data Hold Time                  | 30    |     | 30    |     | ns   |

| t <sub>rec</sub> (WE)    | Write Recover Time/Address hold | 30    |     | 30    |     | ns   |

| t <sub>dis</sub> (WE)    | Output Disable Time from WE#    |       | 90  |       | 100 | ns   |

| t <sub>dis</sub> (OE)    | Output Disable Time from OE#    |       | 90  |       | 100 | ns   |

| t <sub>en</sub> (WE)     | Output Enable Time from WE#     | 5     |     | 5     |     | ns   |

| t <sub>en</sub> (OE)     | Output Enable Time from OE#     | 5     |     | 5     |     | ns   |

| t <sub>su</sub> (OE-WE)  | Output Enable Setup from WE#    | 10    |     | 10    |     | ns   |

| t <sub>h</sub> (OE-WE)   | Output Enable Hold from WE#     | 50    |     | 50    |     | ns   |

| t <sub>su</sub> (CE)     | Card Enable Setup Time from OE# | 0     |     | 0     |     | ns   |

| t <sub>h</sub> (CE)      | Card Enable Hold Time           | 20    |     | 20    |     | ns   |

| t <sub>rec</sub> (WEL)   | Reset recovery to WE going low  | 1     |     | 1     |     | μs   |

Note: AC timing diagrams and characteristics are guaranteed to meet or exceed PCMCIA 2.1 specifications.

#### Write Timing Diagram

## **Data Write and Erase Performance** (1,3)

$VCC = 5V \pm 5\%$ ,  $T_A = 0C$  to + 70C

| SYM                | Parameter                                          | Notes | Min | Typ <sup>(1)</sup> | Max | Units | Test Conditions                                 |

|--------------------|----------------------------------------------------|-------|-----|--------------------|-----|-------|-------------------------------------------------|

| t <sub>WHQV1</sub> | Word/Byte Program time                             | 2,4   |     | 6.3                |     | μs    | Effective time per Byte<br>(using Write Buffer) |

| t <sub>WHQV3</sub> | Byte Program Time (using Byte program command)     |       |     | 180                |     | μs    |                                                 |

|                    | Block Program Time (using write to buffer command) | 2     |     | 0.8                |     | sec   | Word Program Mode                               |

| t <sub>WHQV4</sub> | Block Erase Time                                   | 2     |     | 0.7                |     | sec   |                                                 |

| t <sub>whRH</sub>  | Erase Suspend Latency<br>Time to Read              |       |     | 26                 | 35  | μs    |                                                 |

#### Notes:

- 1. Typical: Nominal voltages and  $T_A = 25C$ .

- 2. Excludes system overhead.

- 3. Valid for all speed options.

- 4. To maximize system performance RDY/BSY# signal should be polled.

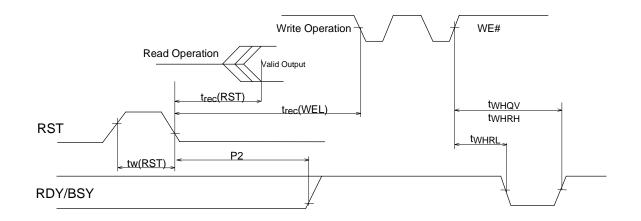

## **Waveforms for Reset Operation**

| SYMBOL                | Parameter                                         | Min | Max | Unit |

|-----------------------|---------------------------------------------------|-----|-----|------|

| t <sub>w(RST)</sub>   | Reset pulse High time                             | 35  |     | μs   |

| P2                    | RST Low to reset during<br>Erase/Program/Lock-bit |     | 100 | ns   |

| t <sub>rec(RST)</sub> | Reset Low to output delay                         |     | 500 | ns   |

| t <sub>rec(WEL)</sub> | Reset Recovery to WE going Low                    | 1   |     | μs   |

| t <sub>WHRI</sub>     | WE High to Rdy/Bsy going low                      |     | 100 | ns   |

# CIS DATA FOR FLF10 32MB & 64 MB CARDS BASED ON INTEL 28F128J3A

| Address | Value | Description                     | Address | Value | Description              |

|---------|-------|---------------------------------|---------|-------|--------------------------|

| 00H     | 01H   | CISTPL_DEVICE                   | 48H     | 05H   | TPL_LINK(05H)            |

| 02H     | 03H   | TPL_LINK                        | 4AH     | F6H   | EDI TPLMID_MANF: LSB     |

| 04H     | 51H   | FLASH = 250ns (device writable) | 4CH     | 01H   | EDI TPLMID_MANF: MSB     |

| 06H     | 7EH   | CARD SIZE: 32MB                 | 4EH     | 00H   | LSB: Number Not Assigned |

|         | FEH   | 64MB                            | 50H     | 00H   | MSB: Number Not Assigned |

| 08H     | FFH   | END OF DEVICE                   | 52H     | FFH   | END OF TUPLE             |

| 0AH     | 1CH   | CISTPL_DEVICE_OC                | 54H     | 1AH   | CISTPL_CONF              |

| 0CH     | 04H   | TPL_LINK                        | 56H     | 06H   | TPL_LINK                 |

| 0EH     | 02H   | 3 VOLT OPERATION                | 58H     | 01H   | TPCC_SZ                  |

| 10H     | 51H   | FLASH = 250ns (device writable) | 5AH     | 00H   | TPCC_LAST                |

| 12H     | 7EH   | CARD SIZE:32MB                  | 5CH     | 00H   | TPCC_RADR                |

|         | FEH   | 64MB                            | 5EH     | 40H   | TPCC_RADR                |

| 14H     | FFH   | END OF DEVICE                   | 60H     | 00H   | TPCC_RMSK                |

| 16H     | 18H   | CISTPL_JEDEC_C                  | 62H     | FFH   | END OF TUPLE             |

| 18H     | 03H   | TPL_LINK                        | 64H     | 1BH   | CISTPL_CFTABLE_ENTRY     |

| 1AH     | 89H   | Manufacturer ID -INTEL          | 66H     | 03H   | TPL_LINK                 |

| 1CH     | 18H   | Device ID - 28F0128J3A          | 68H     | 00H   | TPCE_INDEX               |

| 1EH     | FFH   | END OF DEVICE                   | 6AH     | 00H   | TPCE_FS (no selection)   |

| 20H     | 17H   | CISTPL_DEVICE_A                 | 6CH     | FFH   | END OF TUPLE             |

| 22H     | 03H   | TPL_LINK                        | 6EH     | 15H   | CISTPL_VERS1             |

| 24H     | 42H   | EEPROM - 200ns                  | 70H     | 7FH   | TPL_LINK                 |

| 26H     | 01H   | Device Size = 2KBytes           | 72H     | 04H   | TPLLV1_MAJOR             |

| 28H     | FFH   | END OF TUPLE                    | 74H     | 01H   | TPLLV1_MINOR             |

| 2AH     | 1DH   | CISTPL DEVICE OA                | 76H     | 37H   | 7                        |

| 2CH     | 03H   | TPL_LINK                        | 78H     | 50H   | Р                        |

| 2EH     | 02H   | 3 VOLT OPERATION                | 7AH     | 30H   | 0                        |

| 30H     | 11H   | ROM - 250ns                     | 7CH     | 33H   | 3                        |

| 32H     | FFH   | END OF DEVICE                   | 7EH     | 32H   | 2                        |

| 34H     | 1EH   | CISTPL_DEVICEGEO                | 80H     | 46H   | F                        |

| 36H     | 07H   | TPL_LINK                        | 82H     | 4CH   | L                        |

| 38H     | 02H   | DGTPL_BUS                       | 84H     | 46H   | F                        |

| 3AH     | 12H   | DGTPL_EBS                       | 86H     | 31H   | 1                        |

| 3CH     | 01H   | DGTPL_RBS                       | 88H     | 32H   | 2                        |

| 3EH     | 01H   | DGTPL_WBS                       | 8AH     | 2DH   | -                        |

| 40H     | 01H   | DGTPL_PART                      | 8CH     | 2DH   | -                        |

| 42H     | 01H   | FLASH DEVICE                    | 8EH     | 2DH   | -                        |

|         |       | NON-INTERLEAVED                 | 90H     | 32H   | 2                        |

| 44H     | FFH   | END OF TUPLE                    | 92H     | 35H   | 5                        |

| 46H     | 20H   | CISTPL_MANFID                   | 94H     | 20H   | SPACE                    |

# CIS DATA FOR FLF10 32MB & 64 MB CARDS BASED ON INTEL 28F128J3A (CONT.)

| Address | Value | Description |  |  |

|---------|-------|-------------|--|--|

| 96H     | 00H   | END TEXT    |  |  |

| 98H     | 43H   | С           |  |  |

| 9AH     | 4FH   | 0           |  |  |

| 9CH     | 50H   | Р           |  |  |

| 9EH     | 59H   | Ŷ           |  |  |

| A0H     | 52H   | R           |  |  |

| A2H     | 49H   | 1           |  |  |

| A4H     | 47H   | G           |  |  |

| A6H     | 48H   | Н           |  |  |

| A8H     | 54H   | Т           |  |  |

| AAH     | 20H   | SPACE       |  |  |

| ACH     | 57H   | W           |  |  |

| AEH     | 48H   | Н           |  |  |

| B0H     | 49H   | 1           |  |  |

| B2H     | 54H   | Т           |  |  |

| B4H     | 45H   | E           |  |  |

| B6H     | 20H   | SPACE       |  |  |

| B8H     | 45H   | E           |  |  |

| BAH     | 4CH   | L           |  |  |

| BCH     | 45H   | E           |  |  |

| BEH     | 43H   | С           |  |  |

| C0H     | 54H   | Т           |  |  |

| C2H     | 52H   | R           |  |  |

| C4H     | 4FH   | 0           |  |  |

| C6H     | 4EH   | N           |  |  |

| C8H     | 49H   | 1           |  |  |

| CAH     | 43H   | С           |  |  |

| CCH     | 20H   | SPACE       |  |  |

| CEH     | 44H   | D           |  |  |

| D0H     | 45H   | E           |  |  |

| D2H     | 53H   | S           |  |  |

| D4H     | 49H   | 1           |  |  |

| D6H     | 47H   | G           |  |  |

| D8H     | 4EH   | N           |  |  |

| DAH     | 53H   | S           |  |  |

| DCH     | 20H   | SPACE       |  |  |

| DEH     | 43H   | C           |  |  |

| E0H     | 4FH   | 0           |  |  |

| E2H     | 52H   | R           |  |  |

| E4H     | 50H   | Р           |  |  |

| E6H     | 4FH   | 0           |  |  |

| E8H     | 52H   | R           |  |  |

| Address | Value      | Description |

|---------|------------|-------------|

| EAH     | 41H        | А           |

| ECH     | 54H        | Т           |

| EEH     | 49H        | 1           |

| F0H     | 4FH        | 0           |

| F2H     | 4EH        | N           |

| F4H     | 20H        | SPACE       |

| F6H     | <b>00H</b> | END TEXT    |

| F8H     | 31H        | 1           |

| FAH     | 39H        | 9           |

| FCH     | 39H        | 9           |

| Ē       | 39H        | 9           |

| 100H    | <b>00H</b> | END TEXT    |

| 102H    | <b>00H</b> | NULL        |

| 104H    | FFH        | END OF LIST |

# CIS DATA FOR FLF10 96MB - 192MB CARDS BASED ON INTEL 28F128J3A

| Address | Value | Description                            | Address | Value | Description              |

|---------|-------|----------------------------------------|---------|-------|--------------------------|

| 00H     | 01H   | CISTPL_DEVICE                          | 48H     | 02H   | DGTPL_BUS                |

| 02H     | 03H   | TPL_LINK                               | 4AH     | 12H   | DGTPL_EBS                |

| 04H     | 51H   | FLASH = 250ns (device writable)        | 4CH     | 01H   | DGTPL_RBS                |

| 06H     | FEH   | CARD SIZE: 64MB (1 <sup>st</sup> page) | 4EH     | 01H   | DGTPL_WBS                |

| 08H     | FFH   | END OF DEVICE                          | 50H     | 01H   | DGTPL_PART               |

| 0AH     | 1CH   | CISTPL_DEVICE_OC                       | 52H     | 01H   | FLASH DEVICE             |

| 0CH     | 04H   | TPL_LINK                               |         |       | NON-INTERLEAVED          |

| 0EH     | 02H   | 3 VOLT OPERATION                       | 54H     | FFH   | END OF TUPLE             |

| 10H     | 51H   | FLASH = 250ns (device writable)        | 56H     | 20H   | CISTPL_MANFID            |

| 12H     | 7EH   | CARD SIZE:64MB (1 <sup>st</sup> page)  | 58H     | 05H   | TPL_LINK(05H)            |

| 14H     | FFH   | END OF DEVICE                          | 5AH     | F6H   | EDI TPLMID_MANF: LSB     |

| 16H     | 09H   | CISTPL_EXTDEVICE                       | 5CH     | 01H   | EDI TPLMID_MANF: MSB     |

| 18H     | 06H   | TPL_LINK                               | 5EH     | 00H   | LSB: Number Not Assigned |

| 1AH     | 0CH   | Mem Paging Info:2bit/COR/64MB          | 60H     | 00H   | MSB: Number Not Assigned |

| 1CH     | 51H   | Flash = 250 ns                         | 62H     | FFH   | END OF TUPLE             |

| 1EH     | 07H   | Device Size Extender                   | 64H     | 1AH   | CISTPL_CONF              |

| 20H     | 01H   | 1x64MB (for 96MB and 128MB)            | 66H     | 06H   | TPL_LINK                 |

|         | 02H   | 2x64MB (for 160MB and 192MB)           | 68H     | 01H   | TPCC_SZ                  |

|         |       |                                        | 6AH     | 00H   | TPCC_LAST                |

| 22H     | 7DH   | +32MB (for 96MB and 160MB)             | 6CH     | 00H   | TPCC_RADR                |

|         | FEH   | +64MB (for 128MB and 192 MB)           | 6EH     | 40H   | TPCC_RADR                |

| 24H     | FFH   | END OF TUPLE                           | 70H     | 03H   | TPCC_RMSK                |

| 26H     | 18H   | CISTPL_JEDEC_C                         | 72H     | FFH   | END OF TUPLE             |

| 28H     | 03H   | TPL_LINK                               | 74H     | 15H   | CISTPL_VERS1             |

| 2AH     | 89H   | Manufacturer ID - INTEL                | 76H     | 7FH   | TPL_LINK                 |

| 2CH     | 18H   | Device ID - 28F0128J3A                 | 78H     | 04H   | TPLLV1_MAJOR             |

| 2EH     | FFH   | END OF DEVICE                          | 7AH     | 01H   | TPLLV1_MINOR             |

| 30H     | 17H   | CISTPL_DEVICE_A                        | 7CH     | 37H   | 7                        |

| 32H     | 03H   | TPL_LINK                               | 7EH     | 50H   | Р                        |

| 34H     | 42H   | EEPROM - 200ns                         | 80H     | 30H   | 0                        |

| 36H     | 01H   | Device Size = 2Kbytes                  | 82H     | 39H   | 9                        |

| 38H     | FFH   | END OF TUPLE                           | 84H     | 36H   | 6                        |

| 3AH     | 1DH   | CISTPL_DEVICE_OA                       | 86H     | 46H   | F                        |

| 3CH     | 03H   | TPL_LINK                               | 88H     | 4CH   | L                        |

| 3EH     | 02H   | 3 VOLT OPERATION                       | 8AH     | 46H   | F                        |

| 40H     | 11H   | ROM - 250ns                            | 8CH     | 31H   | 1                        |

| 42H     | FFH   | END OF DEVICE                          | 8EH     | 32H   | 2                        |

| 44H     | 1EH   | CISTPL_DEVICEGEO                       | 90H     | 2DH   | -                        |

| 46H     | 07H   | TPL_LINK                               | 92H     | 2DH   | -                        |

## CIS DATA FOR FLF10 96MB - 192MB CARDS BASED ON INTEL 28F128J3A (CONT.)

| Address | Value      | Description |  |  |

|---------|------------|-------------|--|--|

| 94H     | 2DH        | -           |  |  |

| 96H     | 32H        | 2           |  |  |

| 98H     | 35H        | 5           |  |  |

| 9AH     | 20H        | SPACE       |  |  |

| 9CH     | <b>00H</b> | END TEXT    |  |  |

| 9EH     | 43H        | С           |  |  |

| A0H     | 4FH        | 0           |  |  |

| A2H     | 50H        | Р           |  |  |

| A4H     | 59H        | Ŷ           |  |  |

| A6H     | 52H        | R           |  |  |

| A8H     | 49H        | 1           |  |  |

| AAH     | 47H        | G           |  |  |

| ACH     | 48H        | Н           |  |  |

| AEH     | 54H        | Т           |  |  |

| B0H     | 20H        | SPACE       |  |  |

| B2H     | 57H        | W           |  |  |

| B4H     | 48H        | Н           |  |  |

| B6H     | 49H        | Ι           |  |  |

| B8H     | 54H        | Т           |  |  |

| BAH     | 45H        | E           |  |  |

| BCH     | 20H        | SPACE       |  |  |

| BEH     | 45H        | E           |  |  |

| COH     | 4CH        | L           |  |  |

| C2H     | 45H        | E           |  |  |

| C4H     | 43H        | С           |  |  |

| C6H     | 54H        | Т           |  |  |

| C8H     | 52H        | R           |  |  |

| CAH     | 4FH        | 0           |  |  |

| CCH     | 4EH        | N           |  |  |

| CEH     | 49H        | 1           |  |  |

| D0H     | 43H        | С           |  |  |

| D2H     | 20H        | SPACE       |  |  |

| D4H     | 44H        | D           |  |  |

| D6H     | 45H        | E           |  |  |

| D8H     | 53H        | S           |  |  |

| DAH     | 49H        | 1           |  |  |

| DCH     | 47H        | G           |  |  |

| DEH     | 4EH        | N           |  |  |

| E0H     | 53H        | S           |  |  |

| E2H     | 20H        | SPACE       |  |  |

| E4H     | 43H        | С           |  |  |

| E6H     | 4FH        | 0           |  |  |

| Address | Value | Description |

|---------|-------|-------------|

| E8H     | 52H   | R           |

| EAH     | 50H   | Р           |

| ECH     | 4FH   | 0           |

| EEH     | 52H   | R           |

| F0H     | 41H   | А           |

| F2H     | 54H   | Т           |

| F4H     | 49H   | 1           |

| F6H     | 4FH   | 0           |

| F8H     | 4EH   | N           |

| FAH     | 20H   | SPACE       |

| FCH     | 00H   | END TEXT    |

| FEH     | 31H   | 1           |

| 100H    | 39H   | 9           |

| 102H    | 39H   | 9           |

| 104H    | 39H   | 9           |

| 106H    | 00H   | END TEXT    |

| 108H    | 00H   | NULL        |

| 10AH    | FFH   | END OF LIST |

**FLF10 Series**

| PRODUCT MARKING    |                                                                                                                                                                                                                                   |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WED 7P             | 032FLF1200C15 C995 9915                                                                                                                                                                                                           |  |

| EDI                | Date code                                                                                                                                                                                                                         |  |

|                    | Lot code / trace number                                                                                                                                                                                                           |  |

|                    | Part number                                                                                                                                                                                                                       |  |

|                    | <u>Com</u> pany Name                                                                                                                                                                                                              |  |

| transition period, | re currently marked with our pre-merger company name/acronym (EDI). During our<br>some products will also be marked with our new company name/acronym (WED).<br>2000 all PCMCIA products will be marked only with the WED prefix. |  |

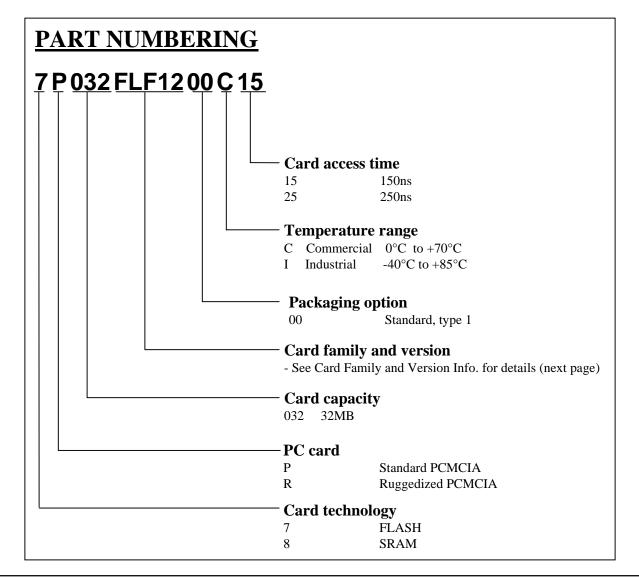

# 7P XXX FLF YY SS T ZZ

| where |     |                                 |

|-------|-----|---------------------------------|

| XXX:  | 032 | 32MB                            |

|       | 064 | 64MB                            |

|       | 096 | 96MB                            |

|       | 128 | 128MB                           |

|       | 160 | 160MB                           |

|       | 192 | 192MB                           |

| YY:   | 12  | based on 28F128J3A              |

|       |     | With Attribute Memory           |

|       | 14  | based on 28F128J3A              |

|       |     | With Attribute Memory and       |

|       |     | Write Protect Switch (optional) |

| SS:   | 00  | WEDC Logo                       |

|       | 01  | Blank Housing Type 1            |

|       | 02  | Blank Housing T1 (Recessed)     |

| T:    | С   | Commercial                      |

| ZZ:   | 20  | 200ns                           |

|       | 25  | 250ns                           |

| REVISION HISTORY |         |                                                |  |

|------------------|---------|------------------------------------------------|--|

| Date of Revision | Version | Description                                    |  |

| 22-Jul-99        | -000    | Initial Release                                |  |

| 31-May-00        | -001    | Add Pg. 16                                     |  |

| 01-Aug-00        | -002    | Corrected Timing Errors, Pgs. 9 & 10           |  |

| 06-Nov-00        | -003    | Corrected CIS Errors, Pg. 14, and Added Memory |  |

|                  |         | Chip Information, Pg. 6                        |  |

### White Electronic Designs Corporation

One Research Drive, Westborough, MA 01581, USA tel: (508) 366 5151 fax: (508) 836 4850 www.whiteedc.com