#### TC5092AP C2MOS 13-BIT A/D CONVERTER

#### GENERAL DESCRIPTION

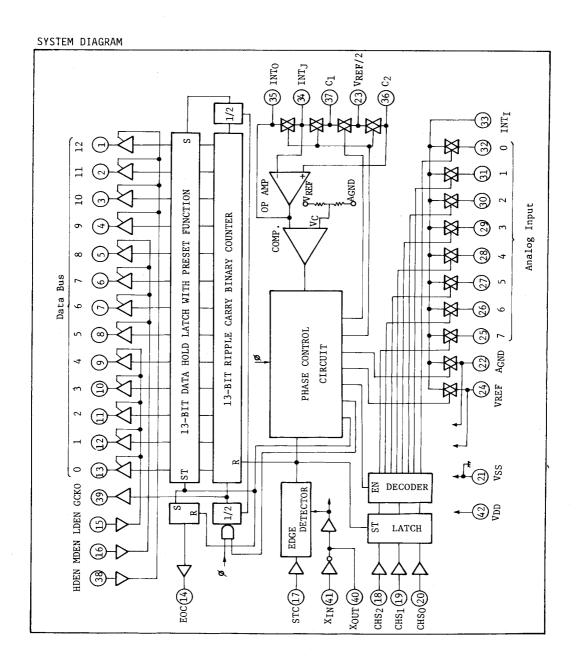

The TC5092AP is an integration 13-bit A/D converter of high precision and low power consumption. The 13-bit, 3-state data output is capable of independent enable in 4 bits so as to be connected directly to 4-bit/8-bit/12-bit data bus. (LSB is common to lower order 4 bits.)

Further, since this converter has an 8-channel analog multiplexer, and a serial clock output function, it is most suitable as data collection unit of various industrial control instruments.

#### FEATURES:

- . High precision......±1 LSB(Typ.)

- . Low power consumption....10mW(Typ.)

- . Single power supply.....VDD=5V±0.5V

- . High-speed conversion....fcp Max.=5MHz

- . 8-channel analog multiplexer contained

- . TLL/CMOS compatible digital Input/Output . Capable of direct connection to 4-/8-/12-bit bus

### APPLICATIONS:

- . Various industrial control instruments

- . Data collection modules

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL            | RATING                                     | UNIT                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $v_{\mathrm{DD}}$ | Vss-0.5~Vss+7                              | V                                                                                                                                                                                                                                                                 |

| VIN               | Vss-0.5~VDD+0.5                            | V                                                                                                                                                                                                                                                                 |

| VREF              | V <sub>AGND</sub> ~V <sub>DD</sub> +0.5    | V                                                                                                                                                                                                                                                                 |

| VAGND             | $v_{SS}$ -0.5~ $v_{REF}$                   | V                                                                                                                                                                                                                                                                 |

| V <sub>OUT</sub>  | V <sub>SS</sub> -0.5~ V <sub>DD</sub> +0.5 | V                                                                                                                                                                                                                                                                 |

| IIN               | ±10                                        | mA                                                                                                                                                                                                                                                                |

| PD                | 300                                        | mW                                                                                                                                                                                                                                                                |

| Topr              | -40 <b>~</b> 85                            | °C                                                                                                                                                                                                                                                                |

| Tstg              | -65 <b>~</b> 150                           | °C                                                                                                                                                                                                                                                                |

|                   | VDD VIN VREF VAGND VOUT IIN PD Topr        | VDD         VSS-0.5~VSS+7           VIN         VSS-0.5~VDD+0.5           VREF         VAGND~VDD+0.5           VAGND         VSS-0.5~VREF           VOUT         VSS-0.5~VDD+0.5           IIN         ±10           PD         300           Topr         -40~85 |

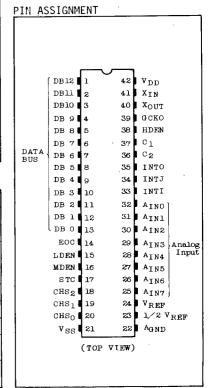

| FUNCTION | OF | EACH | PIN |

|----------|----|------|-----|

|----------|----|------|-----|

| PIN<br>NO. | Symbol           | NAME & FUNCTION                                                                                                                             | PIN<br>NO.                                               | Symbol             | NAME & FUNCTION                                                                                |                                                 |

|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 2 3        | DB12 DB11 DB10   |                                                                                                                                             | 23                                                       | V <sub>REF/2</sub> | Reference voltage supply terminal, which supplies the voltage of $\frac{V_{REF} - A_{GND}}{2}$ |                                                 |

| 4 5        | DB 9             | 3-State Parallel                                                                                                                            | 24                                                       | VREF               | Reference voltage supply terminal                                                              |                                                 |

| 6          | DB 7             | Data Outputs                                                                                                                                | 25                                                       | AIN7               | Analog input terminal Input voltage range:                                                     |                                                 |

| 7<br>8     | DB 6<br>DB 5     | DB12 : MSB DB 0 : LSB                                                                                                                       | 26                                                       | A <sub>IN6</sub>   | AGND ∿ VREF<br>Arbitrary input can be se-                                                      |                                                 |

| 9          | DB 4             |                                                                                                                                             | 27                                                       | A <sub>IN5</sub>   | CHS <sub>0</sub> CHS <sub>1</sub> CHS <sub>2</sub> A <sub>IN</sub>                             |                                                 |

| 11         | DB 2             |                                                                                                                                             | 28                                                       | AIN4               | L L L AINO                                                                                     |                                                 |

| 12         | DB 1             |                                                                                                                                             |                                                          | 1                  | H L L AIN1                                                                                     |                                                 |

| 13         | DB O             |                                                                                                                                             | 29                                                       | AIN3               | L H L AIN2                                                                                     |                                                 |

|            |                  | End of Conversion                                                                                                                           | 30                                                       | A <sub>IN2</sub>   | H H L AIN3                                                                                     |                                                 |

| 14         | 14 EOC           | EOC goes to "L" level at the fall of STC signal, and re-                                                                                    |                                                          |                    | L L H AIN4                                                                                     |                                                 |

| 14         | EOC              | turns to "H" level at the                                                                                                                   |                                                          |                    | H L H AIN5                                                                                     |                                                 |

|            |                  | end of conversion.                                                                                                                          |                                                          |                    | L H H AIN6                                                                                     |                                                 |

| 15         | LDEN             | Low Data Enable<br>DB <sub>o</sub> ∿ DB₄ are read by "H"<br>level input.                                                                    | 32                                                       | AINO               | H H H AIN7  Integrator Input                                                                   |                                                 |

| 16         | MDEN             | Medium Data Enable<br>DB₅∿DB₅ are read by "H"<br>level input.                                                                               | 33                                                       | INTI               | Integrator Junction Integrator Output The integrator consists of these three terminals.        |                                                 |

| 17         | STC              | Start Conversion Conversion starts at the fall time, if pulse input at "H" level is provided. "L" level should be kept during con- version. | 34                                                       | INTJ               | INTI INTI INTO                                                                                 |                                                 |

| 18         | CHS <sub>2</sub> | Channel Select Inputs These pins are addressinputs                                                                                          | _                                                        |                    | RI and CI should satisfy the<br>following formula and be set<br>as small a value as possible   |                                                 |

| 19         | CHS <sub>1</sub> | for selecting eight analog inputs of AINO ~ AIN7, and                                                                                       | for selecting eight analog inputs of AINO ~ AIN7, and 35 | 35                 | INTO                                                                                           | $R_{I} \cdot C_{I} > \frac{13000}{f_{OSC}}$ [S] |

| 20         | CHS <sub>0</sub> | are taken into the internal latch                                                                                                           |                                                          |                    | However, R of 1 $^{\circ}$ 2M $^{\Omega}$ should be used.                                      |                                                 |

| 21         | VSS              | Digital Ground                                                                                                                              | 26                                                       |                    | Capacitors connection terminals                                                                |                                                 |

| 22         | AGND             | Analog Ground                                                                                                                               | 36                                                       | C <sub>2</sub>     | for offset calibration.                                                                        |                                                 |

# FUNCTION OF EACH PIN

| PIN<br>NO. | Symbol            | NAME & FUNCTION                                                                                   |

|------------|-------------------|---------------------------------------------------------------------------------------------------|

| 37         | c <sub>1</sub>    | 0.1 $\mu F$ is connected between C2 and C1, and 0.01 $\mu F$ C1 and VSS, respectively.            |

| 38         | HDEN              | High Data Enable<br>DB9 ∿ DB12 are read by "H"<br>level input.                                    |

| 39         | GCKO              | Gated Clock Output Pulses of number equivalent to conversion data are out- put during conversion. |

| 40         | X <sub>OUT</sub>  | Terminals for system clock oscillation. Crystal oscillators are con-                              |

| 41         | XIN               | nected to both the ends of terminals.                                                             |

| 42         | $v_{\mathrm{DD}}$ | Supply Voltage 5V±0.5V                                                                            |

--- AIN = AGND

# FUNCTIONAL DESCRIPTION

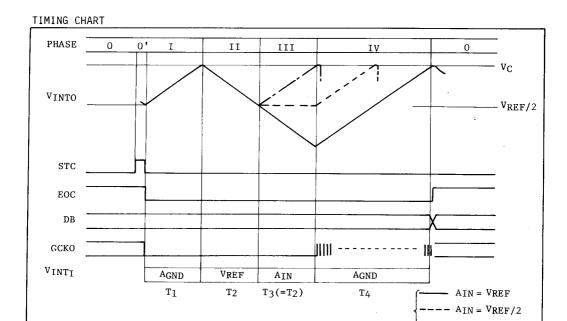

#### (1) Conversion cycle

In the state of PHASE 0', the operation of L3I is at a stop and the integrating amplifier performs as voltage follower. Under this condition the external capactor  $(0.1\mu F \text{ across } C_1 \text{ and } C_2)$

When STC is given, the offset voltage charged into external capacitors is applied to non-inversion of the integrator, thus cancelling the offset volage equivalently. In PHASE I, the integrator continues to integrate AGND until its output reaches VC.

In PHASE III the integrator integrates the analog input for the same period of time as  $T_2$  after it has integrated  $V_{\rm REF}$  for a fixed period of time ( $T_2$ ) in PHASE II.

Finally, in PHASE IV the integrator continues to integrate  $^{A}\text{GND}$  until its output reaches  $\text{V}_{\text{C}}.$

Let the time in PHASE IV be T4. Then the following equation is made (formed) by omitting error factors such as offset drift.

$$V_{AIN} = \frac{T_4}{2T_2} V_{REF}$$

(AGND=0V) ... (1)

In case of this LSI,  $T_2$  is designed by  $4096 \times 2 \cdot T_{OSC}$  ( $T_{OSC}$  denotes reference clock synchronization). Therefore, the above formula letting  $2 \cdot T_{OSC}$  be T is changed as follows:

$$\frac{V_{AIN}}{V_{REF}} = \frac{T_4}{8192T} \qquad .... \qquad (2)$$

That is, 13-bit resolution A/D conversion

of FS (full scale) = 8192 can be made by

counting the period of T4 by use of a clock having T frequency.

However, it is recommended that  $R_{

m I}$  and  $C_{

m I}$  composing the integrator be set to the

values close to 13000/fosc as possible after having satisfied the following formula.

Power On

Voltage Follower

STC ON?

Offset Correction

Calibration Cycle

Analog Input

Integration

Digital Conversion

Update Data

YES

NO

PHASE 0

PHASE 0'

PHASE I

PHASE II

PHASE III

PHASE IV

$$R_{\rm I}C_{\rm I}$$

> 13000 / f<sub>OSC</sub>,  $R_{\rm I}$  = 1  $\sim$  2M $\Omega$  is used. ....... (3)

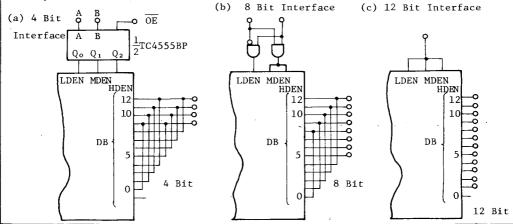

#### (2) Output data format

13-bit output data are output to 13 independent 3-state data buses DB $_0$  DB $_1$ . Since 13-bit outputs can be independently placed on 3-state every group of High, Medium and Low of 4 bits/4 bits/5 bits from the higher order, it is easy to connect the microcomputer to buses of 4, 8, 12 bits.

|      |                |                           | TRUTH TAI                | 3LE  |   |   |                 |      |     |     |   |     |   |    |    |   |

|------|----------------|---------------------------|--------------------------|------|---|---|-----------------|------|-----|-----|---|-----|---|----|----|---|

| LDEN | MDEN           | HDEN                      | Analog Input             |      |   |   | DAT             | `A ( | OUT | PUT | S | (DB | ) |    |    |   |

| BDLN | HDEN           | IIDEN                     | Analog Input             |      | 1 | 2 | 3               | 4    | 5   | 6   | 7 | 8   | 9 | 10 | 11 | 1 |

| L    | L              | L                         |                          |      |   | Z | -               |      |     |     |   |     |   | •  |    |   |

| Н    | L              | L                         |                          | D    | D | D | D               | D    |     | 2   | Z |     |   |    | Z  |   |

| L    | Н              | L                         |                          |      |   | Z |                 | •    | D   | D   | D | D   |   |    | 2  |   |

| Н    | Н              | L                         | Don't Care               | D    | D | D | D               | D    | D   | D   | D | D   |   |    |    |   |

| L    | L              | Н                         |                          |      |   | Z | J               | L    | Z   |     |   | D   | D | D  |    |   |

| Н    | L              | Н                         |                          | D    | D | D | D               | D    |     |     |   | D   | D | D  |    |   |

| L    | Н              | Н                         |                          |      |   | Z | 4               |      | D   | D   | D | D   | D | D  | D  |   |

|      |                |                           | <1/2LSB                  | L    | L | L | L               | L    | L   | L   | L | L   | L | L  | L  | 1 |

|      |                | :                         | $1/2$ LSB $\sim 3/2$ LSB | Н    | L | L | L               | L    | L   | L   | L | L   | L | L  | L  | 1 |

| Н    | Н              | Н                         |                          | Stra |   |   | Straight Binary |      |     |     |   |     |   | •  |    |   |

|      | "F             | "FS"-5/2LSB ~ "FS"-3/2LSB | L                        | Н    | Н | Н | Н               | Н    | Н   | Н   | Н | Н   | н | Н  | I  |   |

| "FS" | "FS"-3/2 LSB < | Н                         | Н                        | Н    | Н | Н | Н               | Н    | Н   | Н   | Н | Н   | Н | ı  |    |   |

Note : FS  $\cdots$  Full Scale, 1 LSB = (VREF-AGND)/8192, Z  $\cdots$  High Impedance D  $\cdots$  "H" or "L" Level

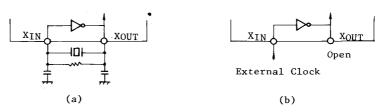

#### (3) Basic clock

Since this LSI operates on the basis of the frequency given to  $X_{\rm IN}$  input, a stable clock (4f < 0.005%) must be used for the clock to be given to  $X_{\rm IN}$ .

Therefore, it is proper that the oscillation circuit is configured as shown in the following figure (a) by the use of externally mounted crystal because the LSI has a built-in inverter for crystal oscillation.

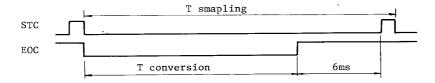

(4) How to give STC input, Conversion time, and Sampling cycle

STC input is taken in with the reference clock of LSI, but the positive pulse having the pulse width for at least two cycles is required for internal starting.

The conversion time of from the fall of STC input to the rise of EOC output. Letting this time be Tc MAX(Maximum conversion time), then the following equation is obtained.

For example, when  $f_{CP}$ =5MHz, TcMAX=8.2ms. For one-time sampling, an accurate output can be obtained from the falling edge of STC input after the lapse of TcMAX.

For consecutive sampling, however, STC input must be given after the lapse of a given period of time (6ms) from the rise of EOC. This period (6ms) is the time required for the recovery of LSI to normal state.

Therefore, the minimum sampling cycle TsMIN is as follows:

$$T_{SMIN} = 41000 \times T_{OSC} + 0.006 + t_{w}(STC) [S] \dots (5)$$

Note: When power is set ON, following start-up procedure is required due to indefinite state of internal circuitry.

- 1. Applying clock, STC is to be set high over 10ms.

- 2. Complete at least one cycle as a dummy conversion cycle.

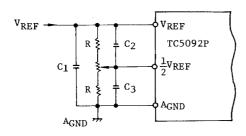

(5) Reference voltage

This LSI has three reference input voltage terminals of  $A_{GND}$ ,  $\frac{1}{2}$   $V_{REF}$ , and  $V_{REF}$ . Since analog input signal is quantized to 1/8192 in the range of  $A_{GND} \sim A_{REF}$  for digitization, stable voltages must be supplied to  $\frac{1}{2}$   $V_{REF}$  and  $V_{REF}$ .

Espacially the value of  $\frac{1}{2}$  VREF voltage has direct effects upon conversion accuracy; therefore, it is recommonded that adjustment be made so as to agree output data with analog input by actually making A/D convert by use of input voltage at FS (full scale) or 1/2FS level.

The left figure shows an example of reference voltage supplying circuit.  $C_1 \sim C_3$  are filter capacitors for preventing reference voltage variations to be caused by ripple or induction noise. Generally the value of capacitor is about  $0.01 \sim 0.1 \mu F$ , though it varies with the system.

#### (6) BUS Interface

For connecting a microcomputer to BUS line, three independent enable terminals are used. These three enable terminals permit the processing in the unit of 4 bits (5 bits for the low order digit only). The microcomputer can be directly connected to the BUS of  $4 \, ^{\circ} 12$  bits easily by allocating proper address of microcomputer to the TC5092AP.

# RECOMMENDED OPERATING CONDITION

| ITEM                     | SYMBOL            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN. | TYP. | MAX.              | UNIT |

|--------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------|------|

| Supply Voltage           | $v_{\mathrm{DD}}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5  | 5.0  | 5.5               | v    |

| Digital Input Voltage    | VIN               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    | -    | $v_{\mathrm{DD}}$ | v    |

| Analog Input Voltage     | VAIN              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AGND | -    | VREF              | -    |

| Reference Supply Voltage | VREF              | , and the second | 4.0  | _    | $v_{\mathrm{DD}}$ | v    |

| Analog Ground Voltage    | VAGND             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    | 0    | 0.5               | V    |

# ELECTRICAL CHARACTERISTICS (VDD = 5V $\pm$ 10%, VSS = 0V, Ta = -40 $\sim$ 85°C)

| ITEM                         | SYMBOL           | TEST CONDITION                                                 | V <sub>DD</sub> (V) | MIN. | TYP.  | MAX. | UNIT |

|------------------------------|------------------|----------------------------------------------------------------|---------------------|------|-------|------|------|

| Output High Voltage          | VOH              | I <sub>OH</sub> =-lμA,Digital outp                             | ut 5                | 4.9  | 5.0   | -    | v    |

| Output Low Voltage           | VOL              | IOL=1μΑ, Digital outp                                          | ut 5                | -    | 0.0   | 0.1  |      |

|                              |                  | Digital Input except >                                         | IN 5                | 2.4  | _     | _    |      |

| Input High Voltage           | AIH              | XIN                                                            | 5                   | 4.5  | -     | _    |      |

|                              | **               | Digital Input except >                                         | IN 5                | -    | -     | 0.8  | v    |

| Input Low Voltage            | AIL              | X <sub>IN</sub>                                                | 5                   | -    | _     | 0.5  |      |

| Output High Current          | I <sub>OH</sub>  | VOH = 2.4V Digital output except XC                            | 4.75                | -1.0 | -     | _    | mA   |

| Output Low Current           | IOL              | V <sub>OL</sub> = 0.4V<br>Digital output except X <sub>O</sub> | 4.75                | 1.6  | -     | _    | ·mA  |

|                              | IDH              | $v_{OH}$ = 5.5 $v$ , $DB_0 \sim DB_{12}$                       | 5.5                 | _    | 10-3  | 5    |      |

| Output Disable Current       | IDL              | $V_{OL} = 0.0V$ , $DB_0 \sim DB_{12}$                          | 5.5                 | _    | -10-3 | -5   | μA   |

|                              | IIH              | V <sub>IN</sub> =5.5V,Digital inpu                             | it 5.5              | _    | 10-5  | 1.0  | μA   |

| Input Current                | IIL              | V <sub>IL</sub> =0.0V,Digital inpu                             | it 5.5              | -    | -10-5 | -1.0 |      |

| Analog Switch Off-Leak       | I <sub>OFF</sub> | Analog input/output                                            | 5.5                 | _    | ±10-4 |      | μΑ   |

| Analog Switch<br>On Resistor | RON              | $R_L = 10k\Omega$                                              | 5                   | _    |       | _    | Ω    |

| Operating Consump-           | T                | VREF = VDD fcp=5M                                              | Hz. 5               | -    | 2     | -    | mA   |

| tion Current                 | I <sub>DD</sub>  | Digital open f <sub>CP</sub> =1M                               | Hz 5                | -    | 1     | -    |      |

SWITCHING CHARACTERISTICS ( $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ ,  $T_a = 25 \,^{\circ}\text{C}$ ,  $C_L = 50 \, \text{pF}$ )

| ITEM                    | SYMBOL                             | TEST CONDITION  | MIN. | TYP. | MAX. | UNIT |

|-------------------------|------------------------------------|-----------------|------|------|------|------|

| Output Rise Time        | tTLH                               | Digital output  | -    | 50   | 150  |      |

| Output Fall Time        | tTHL                               | Digital output  | -    | 40   | 150  | ns   |

| Output Enable Time      | t ZL<br>t ZH                       | LDEN )          | -    | 80   | 250  |      |

| Output Disable Time     | t <sub>LZ</sub><br>t <sub>HZ</sub> | MDEN -DB Output | -    | 280  | 500  | ns   |

| Max. Clock Frequency    | fMAXø                              | XIN Duty 40~60% | 5.0  |      | _    |      |

| Min. Clock Frequency    | fminø                              | XIN Duty 40~60% | -    | -    | -    | MHz  |

|                         | CIN                                | Digital input   | -    | 5    | -    | •    |

| Input Capacity          | CIN                                | Analog input    |      | -    | -    | pF   |

| 3-State Output Capacity | C <sub>OUT</sub>                   | DB Output       | -    | 8    | -    |      |

# SYSTEM CHARACTERISTICS ( $V_{DD} = 5V \pm 10\%$ , $V_{SS} = 0V$ , $T_a = 25$ °C)

| ITEM                 | SYMBOL | TEST CONDITION           | MIN.        | TYP.       | MAX.   | UNIT |    |

|----------------------|--------|--------------------------|-------------|------------|--------|------|----|

| Resolution           | n      |                          | -           | 13         | -      | Bit  |    |

|                      |        | $f_{CP} = 5 \text{ MHz}$ | - 1         | _          | 8.2    |      |    |

| Conversion Time      | Tc     | Tc                       | fcP = 1 MHz | -          | -      | 41   | ms |

| Sampling Cycle       | m      | $f_{CP} = 5 \text{ MHz}$ | 14.2        | _          | -      |      |    |

|                      | TSPL   | fcp = 1 MHz              | 47          | -          | _      | ms   |    |

| Nonlinearity         |        |                          | -           | ±1         |        |      |    |

| Zero Scale Error     | Ezp    |                          | -           | <b>±</b> 2 |        | LSB  |    |

| Full Scale Error     | EFS    | $V_{DD} = V_{REF}$       | -           | ±1         |        |      |    |

| STC Min. Pulse Width | tw     |                          | -           | -          | 2/fosc | s    |    |