# The MRFIC Line

# 900 MHz LDMOS Integrated Power Amplifier

This integrated circuit is intended for two–way paging applications and for other Industrial, Scientific and Medical (ISM) at 900 MHz band applications. The three stage design is implemented in Motorola's low cost, high performance LDMOS process and housed in a low–cost surface mount SOIC package. Input and output matching is implemented off–chip for maximum flexibility while interstage matching is on–chip. A power control pin is included allowing 60 dB dynamic range.

- 30.5 dBm Output Power for 3 dBm Input Power at 900 MHz

- 32 dB Typ Small Signal Gain

- 40% Efficiency Min at 30.5 dBm Output Power

- 4.0 to 5.5 Volt Operation

- Low-Cost, Low Profile Plastic SOIC Package

- Order MRFIC0914R2 for Tape and Reel.

R2 Suffix = 2,500 Units per 16 mm, 13 inch Reel.

- Device Marking = M0914

# **MRFIC0914**

900 MHz PAGING POWER AMPLIFIER SI MONOLITHIC INTEGRATED CIRCUIT

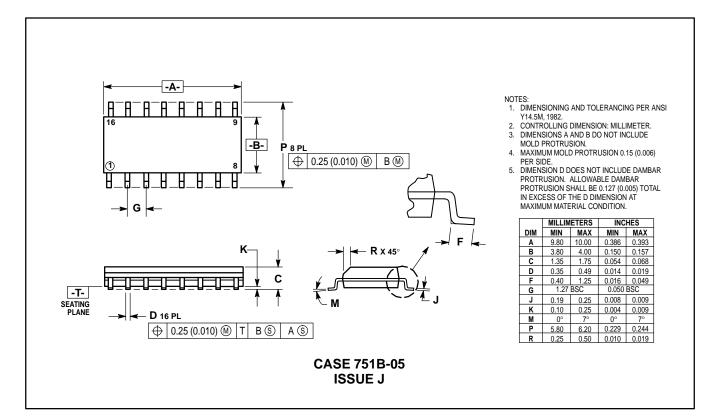

CASE 751B-05 (SOIC-16)

# ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted)

| Rating                               | Symbol                                              | Value       | Unit |

|--------------------------------------|-----------------------------------------------------|-------------|------|

| Supply Voltage                       | V <sub>D1</sub> , V <sub>D2</sub> , V <sub>D3</sub> | 9           | Vdc  |

| Supply Current                       | I <sub>Dtotal</sub>                                 | 2           | Adc  |

| Power Control Voltage                | VCNTRL                                              | 4.8         | Vdc  |

| Input Power                          | Pin                                                 | 6           | dBm  |

| Ambient Operating Temperature        | TA                                                  | -30 to +80  | °C   |

| Storage Temperature                  | T <sub>stg</sub>                                    | -65 to +150 | °C   |

| Thermal Resistance, Junction to Case | θJC                                                 | 26          | °C/W |

# **RECOMMENDED OPERATING RANGES**

| Parameter             | Symbol                                                 | Value      | Unit |

|-----------------------|--------------------------------------------------------|------------|------|

| Supply Voltage        | V <sub>D1</sub> , V <sub>D2</sub> ,<br>V <sub>D3</sub> | 3.6 to 5.8 | Vdc  |

| Power Control Voltage | VCNTRL                                                 | 0 to 4.8   | Vdc  |

| RF Frequency Range    | fRF                                                    | 890 to 928 | MHz  |

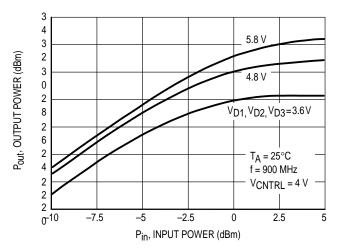

**ELECTRICAL CHARACTERISTICS** ( $V_{D1}$ ,  $V_{D2}$ ,  $V_{D3}$  = 4.8 V, f = 900 MHz,  $P_{in}$  = 3 dBm, 1 ms, 10% duty cycle,  $V_{CNTRL}$  Adjusted for  $I_{Dtotal}$  = 583 mA,  $T_A$  = 25°C unless otherwise noted. Measured in Circuit Configuration Shown in Figure 1.)

| Characteristic                                                                | Min  | Тур | Max | Unit |

|-------------------------------------------------------------------------------|------|-----|-----|------|

| Output Power                                                                  | 1.12 | _   | _   | W    |

| Efficiency                                                                    | 40   | _   | _   | %    |

| Output Power at 1 dB Gain Compression                                         |      | 29  | _   | dBm  |

| Saturated Output Power                                                        |      | 31  | _   | dBm  |

| Output Third Order Intercept Point                                            |      | 36  | _   | dBm  |

| Dynamic Range (V <sub>CNTRL</sub> = 0 to 4.8 V)                               |      | 60  | _   | dB   |

| Input Return Loss                                                             | 7    | 12  | _   | dB   |

| Output Power, Low Voltage ( $V_{D1}$ , $V_{D2}$ , $V_{D3} = 3.84 \text{ V}$ ) | 0.56 | _   | _   | W    |

| Spurious Output (Load VSWR = 20:1, All Phase Angles)                          | _    | -60 | -50 | dBc  |

| Harmonic Output (With External Matching Circuit)                              | _    | _   | -45 | dBc  |

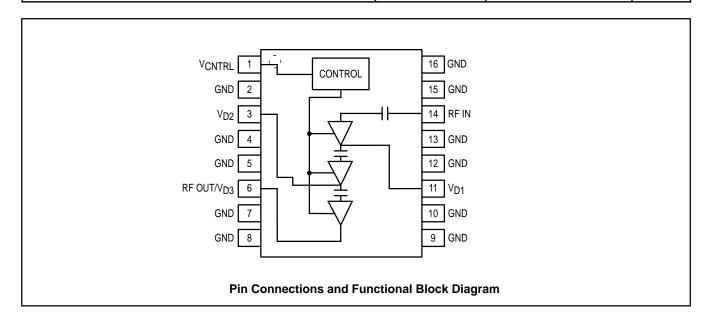

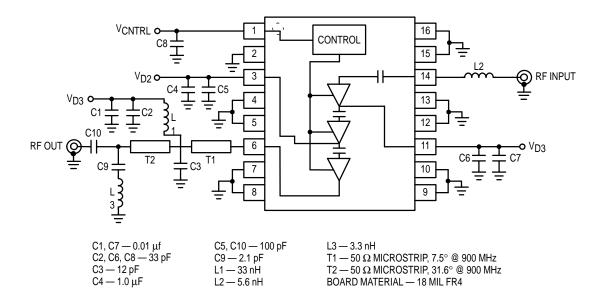

Figure 1. Application Circuit Configuration

Figure 2. Output Power versus Input Power

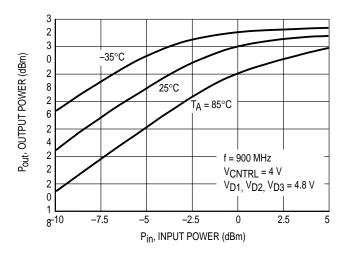

Figure 3. Output Power versus Input Power

Figure 4. Supply Current versus Input Power

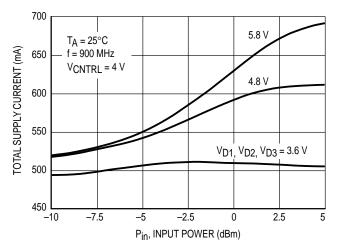

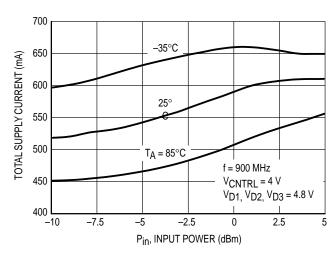

Figure 5. Supply Current versus Input Power

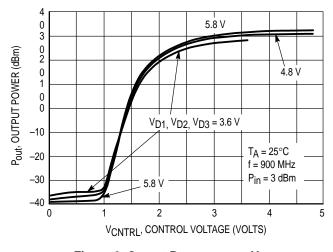

Figure 6. Output Power versus VCNTRL

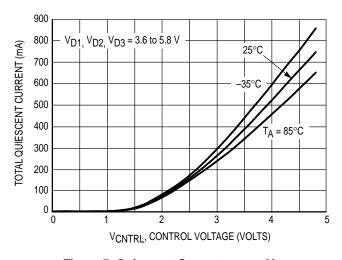

Figure 7. Quiescent Current versus VCNTRL

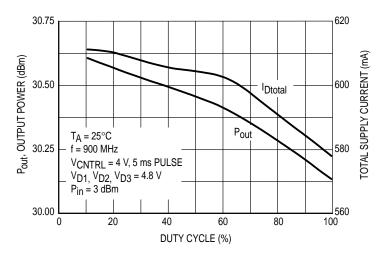

Figure 8. Output Power versus Duty Cycle

| f    | Z <sub>in</sub> (Ω) |       | <b>Z<sub>OL</sub></b> * (Ω) |      |

|------|---------------------|-------|-----------------------------|------|

| MHz  | R                   | jХ    | R                           | jΧ   |

| 800  | 48.8                | -16.3 | 2.56                        | 14.3 |

| 850  | 49.0                | -17.9 | 3.30                        | 14.4 |

| 900  | 49.0                | -19.6 | 2.80                        | 13.1 |

| 950  | 49.4                | -21.2 | 3.94                        | 14.0 |

| 1000 | 49.8                | -23.1 | 3.95                        | 12.6 |

Table 1. Device Impedances Derived from Circuit Characterization

#### APPLICATIONS INFORMATION

#### **DESIGN PHILOSOPHY**

The MRFIC0914 three stage LDMOS integrated power amplifier was designed for low cost and flexibility. While the target application was two—way paging, the device can be used in a variety of 800 to 1000 MHz applications and it is particularly suited to burst mode digital transmissions with constant envelope modulation schemes. Only one supply is required. The VCNTRL pin allows the setting of the gate bias of the three stages simultaneoulsy for optimum gain and efficiency and serves as a transmit control with more than 60 dB dynamic range.

#### **CIRCUIT DETAILS**

In Figure 1, the 900 MHz applications circuit, note that each stage has a separate supply pin, including the RF Output for the third stage. Care should be taken in bypassing these supply connections to avoid low frequency oscillation. Chip capacitors should be mounted as close to the leads and ground vias as possible. Ground vias should be provided close to the indicated ground leads as well. L1 is a bias choke supplying the third stage and could be replaced with a quarter wave line or air—wound inductor.

RF performance is sensitive to the output matching network. C9 and L3 form a second harmonic trap which enhances efficiency. Placement of C3 along the  $50\Omega$  line at the device output is critical to gain and efficiency. L2, the input matching inductor, is optional. Without this inductor, the input match is still typically better than 2:1 VSWR.

It should be note that Figure 1 does not portray the parasitics of the chip components nor their solder mounting pads. The board material is 18 mil dielectric thickness FR4. The impedances shown in Table 1 were derived from circuit characterization and are given as an aid to original designs.

#### **EVALUATION BOARDS**

Evaluation boards are available for RF Monolithic Integrated Circuits by adding a "TF" to the device type. For a complete list of currently available boards and ones in development for newly introduced products, please consult your local Motorola Distributor or Sales Office.

# **PACKAGE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Mfax is a trademark of Motorola, Inc.

How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 303–675–2140 or 1–800–441–2447

**JAPAN**: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 4–32–1, Nishi–Gotanda, Shinagawa–ku, Tokyo 141, Japan. 81–3–5487–8488

Mfax™: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 – US & Canada ONLY 1–800–774–1848

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

INTERNET: http://motorola.com/sps

MRFIC0914/D