## **Dual-Cell Lithium Ion Battery Control IC**

#### **FEATURES**

- Over-Charge Protection

- Over-Discharge Protection

- Short Circuit Current Limiting

- Battery Open-Circuit Center Tap Protection

- Cell Voltage Balancing

- Undervoltage Lockout

- Individual Cell Voltage Monitoring

- Low Operating Current (30 μA) and Shutdown Current (1 μA)

- Internal N-Channel MOSFET Driver

- High Noise Immunity

- Accurate (±1.19%) Over-Charge Voltage Detection

- Four Different Cell Types Covered

#### **DESCRIPTION**

The Si9730 monitors the charging and discharging of dual-cell lithium-ion battery packs (carbon or coke chemistry) ensuring that battery capacity is fully utilized while ensuring safe operation. The Si9730 provides protection against overcharge, over-discharge, and short circuit conditions which are hazardous to the battery and the environment.

Battery voltages of each individual cell are monitored at the center-tap connection by an internal A/D converter through the  $V_{\rm C}$  pin. If one or both of the cells is determined to be

overcharged, an internal cell balancing network "bleeds" off current at 15  $\mu A$  until both cells are charged to the same maximum level. Depending on the condition of each cell, the Si9730 will switch two external source-connected n-channel MOSFETs on or off to allow the cells to be charged or to provide current to the load.

The Si9730 is available in an 8-pin SOIC package with an operating temperature range of -25 to 85°C. The Si9730 is available in both standard and lead (Pb)-free packages.

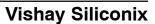

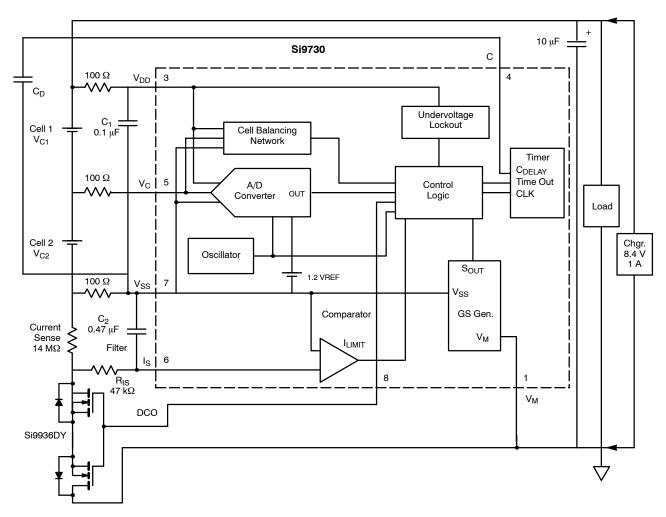

#### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

#### **ABSOLUTE MAXIMUM RATINGS**

| $V_{M}$ $V_{DD}$ –15 V to $V_{DD}$ +15 V                       | Maximum Operating Junction Temperature |

|----------------------------------------------------------------|----------------------------------------|

| $V_{DD}$                                                       | Power Dissipation                      |

| $V_{C}$ $V_{SS}$ -0.3 V to $V_{DD}$ +0.3 V                     | Thermal Impedance (P <sub>O,IA</sub> ) |

| $I_{S}$ $(V_{SS} \ge V_{M})$ $V_{M}$ -0.3 V to $V_{DD}$ +0.3 V | Thermal impedance (FOJA)               |

| $(V_{M} \ge V_{SS})$ $V_{SS}$ -0.3 V to $V_{DD}$ +0.3 V        | Storage Temperature                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING RANGE**

| $C_{VC} < 10 \text{ pF from V}_{C} \text{ toV}_{DD} \text{ andV}_{SS}$ , Total  | $V_{DD}$ to $V_{SS}$                    |

|---------------------------------------------------------------------------------|-----------------------------------------|

| $C_D$ Open to 1.0 $\mu F$                                                       | $V_{DD}$ to $V_{M}$                     |

| $R_{\text{IS}}$ series resistance to sense resistor $\dots < 27~\text{k}\Omega$ | Operating Temperature Range –25 to 85°C |

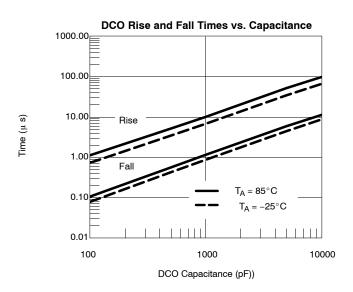

| DCO Load Capacitance                                                            |                                         |

| SPECIFICATIONS                                      |                          |                                                                                                                                                      |                                                                                                           |                                            |      |                      |          |

|-----------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------|------|----------------------|----------|

|                                                     |                          | Test Condition<br>Unless Otherwise Specified                                                                                                         |                                                                                                           | <b>Limits</b> T <sub>A</sub> = -25 to 85°C |      |                      |          |

| Parameter                                           | Symbol                   |                                                                                                                                                      |                                                                                                           | Min <sup>a</sup>                           | Typb | Max <sup>a</sup>     | Unit     |

| Power Supply                                        | -                        |                                                                                                                                                      |                                                                                                           |                                            |      |                      |          |

| Supply Current, Charging Operation                  | I <sub>DD_C</sub>        | V <sub>C1</sub> = V <sub>C2</sub> = 2                                                                                                                | $2.6 \text{ V}, \text{ V}_{DD} - \text{V}_{M} = 8.4 \text{ V}$                                            |                                            |      | 60                   |          |

| Supply Current, Normal Operation                    | I <sub>DD</sub>          | 01 02                                                                                                                                                | e = 4.05 V, V <sub>M</sub> = V <sub>SS</sub>                                                              |                                            |      | 30                   | μΑ       |

| Supply Current, Normal Operation                    | I <sub>DD_UVL</sub>      | $V_{M} = V_{DD}$                                                                                                                                     | $V_{C1} = V_{C2} = 1.7 \text{ V}$                                                                         |                                            |      | 1                    |          |

| Undervoltage Lockout Threshold                      | V <sub>UVL</sub>         |                                                                                                                                                      | at V <sub>DD</sub> – V <sub>SS</sub> (Falling)<br><sub>2</sub> , V <sub>DD</sub> – V <sub>M</sub> = 5.5 V | 3.5                                        | 3.7  | 4.0                  | ٧        |

| V <sub>M</sub> Leakage Current                      | I <sub>VM_UVL</sub>      | $V_{C1} = V_{C2}$                                                                                                                                    | <sub>2</sub> = 1.7 V, V <sub>DD</sub> = V <sub>M</sub>                                                    |                                            |      | 1                    |          |

| V <sub>M</sub> Operating Current                    | I <sub>VM</sub>          | $V_{C1} = V_{C2} = 2$                                                                                                                                | $2.6 \text{ V}, \text{ V}_{DD} - \text{V}_{M} = 8.4 \text{ V}$                                            |                                            |      | 30                   | μΑ       |

| Control Logic                                       |                          |                                                                                                                                                      |                                                                                                           |                                            |      |                      |          |

| DCO Output High Voltage                             | V <sub>OH</sub>          | $I_{OH} = -10 \mu A$ , $V_{C1} = V_{C2} = 3.3 \text{ V}$<br>$V_{DD} - V_{M} = 6.6 \text{ V}$                                                         |                                                                                                           | V <sub>DD</sub> – 0.1                      |      |                      | ٧        |

| DCO Rise Time (10% to 80%)                          | t <sub>r</sub>           | V <sub>C1</sub> = 2 V, V <sub>C2</sub> = 2.4 V                                                                                                       |                                                                                                           |                                            |      | 7.5                  | <u> </u> |

| DCO Fall Time (80% to 10%)                          | t <sub>f</sub>           | $V_{DD} - V_{M} = 8.4 V_{M}$                                                                                                                         | $/ C_L = 500 \text{ pF, DCO to V}_{SS}$                                                                   |                                            |      | 1                    | μS       |

| DCO Output Low Voltage                              | Vol                      | I <sub>OL</sub> = 10 μA                                                                                                                              | $V_{M} = V_{DD}$<br>$V_{C1} = 2 \text{ V}, V_{C2} = 2.4 \text{ V}$                                        |                                            |      | V <sub>SS</sub> +0.4 | V        |

| Doo Guipat Low Voltago                              | VOL                      | $V_{M} = V_{SS}$<br>$V_{C1} = V_{C2} = 4.4 \text{ V}, I_{S} = V_{DD}$                                                                                |                                                                                                           |                                            |      | V <sub>M</sub> +0.52 | ,        |

| Analog Section                                      |                          |                                                                                                                                                      |                                                                                                           |                                            |      |                      |          |

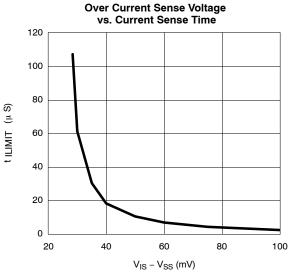

| Current-Limit Comparator Trip Point                 | V <sub>ILIMIT</sub>      | $V_{C1} = V_{C2} = 4.05 \text{ V}, V_{M} = V_{SS} + 0.25 \text{ V}$ $I_{S}$ Rising, $I_{A} = 25^{\circ}\text{C}$                                     |                                                                                                           | 25.5                                       | 28   | 32                   | mV       |

| Current-Limit<br>Comparator Temperature Coefficient | dV <sub>ILIMIT</sub> /dT |                                                                                                                                                      |                                                                                                           |                                            | 0.18 |                      | %/°C     |

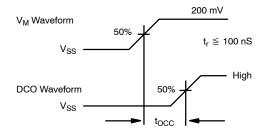

| Current-Limit<br>Comparator Response Time           | t <sub>ILIMIT</sub>      | V <sub>C1</sub> = V <sub>C2</sub> =3.3 V, V <sub>M</sub> = V <sub>SS</sub> + 0.25 V<br>C <sub>L</sub> = 50 pF, DCO to V <sub>SS</sub> , See Figure 2 |                                                                                                           |                                            |      | 25                   | μs       |

| Current Limit Comparator<br>Input Bias Current      | I <sub>IS</sub>          | V <sub>C1</sub> = V <sub>C2</sub> =3.5                                                                                                               | 3 V, V <sub>DD</sub> = V <sub>M</sub> , V <sub>IS</sub> = V <sub>SS</sub>                                 | -125                                       |      |                      | nA       |

|                                                         |             |                                     | Total Countilities                                                                                                     |                                                                                 | <b>Limits</b><br>T <sub>A</sub> = -25 to 85°C |                                   |      |                 |  |

|---------------------------------------------------------|-------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------|------|-----------------|--|

| Parameter                                               |             | Symbol                              |                                                                                                                        | Condition<br>erwise Specified                                                   | Min <sup>a</sup>                              | Typ <sup>b</sup> Max <sup>a</sup> |      | Uni             |  |

| Analog Section (cont'd)                                 |             |                                     | L                                                                                                                      | ·                                                                               | 1                                             |                                   |      |                 |  |

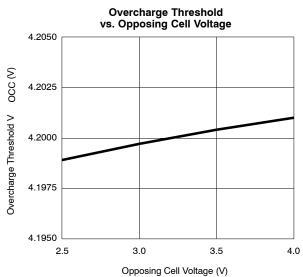

|                                                         | 1           |                                     |                                                                                                                        | T <sub>A</sub> = 25°C                                                           | 4.15                                          | 4.20                              | 4.25 | I               |  |

|                                                         |             | V <sub>OC1</sub><br>Cell 1          | $V_{C2} = 4.05 \text{ V}$                                                                                              | T <sub>A</sub> = -25°C                                                          | 4.1                                           |                                   | 4.27 |                 |  |

|                                                         | Α           |                                     | $V_{DD} - V_{M} = 8.6 \text{ V}$                                                                                       | T <sub>A</sub> = 85°C                                                           | 4.1                                           |                                   | 4.27 |                 |  |

|                                                         | Suffix      |                                     |                                                                                                                        | T <sub>A</sub> = 25°C                                                           | 4.15                                          | 4.20                              | 4.25 |                 |  |

|                                                         |             | V <sub>OC2</sub><br>Cell 2          | $V_{C1} = 4.05 \text{ V}$<br>$V_{DD} - V_{M} = 8.6 \text{ V}$                                                          | T <sub>A</sub> = -25°C                                                          | 4.1                                           |                                   | 4.27 |                 |  |

|                                                         |             | Oeii Z                              | VDD - VM = 0.0 V                                                                                                       | T <sub>A</sub> = 85°C                                                           | 4.1                                           |                                   | 4.27 |                 |  |

|                                                         |             |                                     |                                                                                                                        | T <sub>A</sub> = 25°C                                                           | 4.2                                           | 4.25                              | 4.30 |                 |  |

|                                                         |             | V <sub>OC1</sub><br>Cell 1          | $V_{C2} = 4.05 \text{ V}$<br>$V_{DD} - V_{M} = 8.6 \text{ V}$                                                          | $T_A = -25^{\circ}C$                                                            | 4.15                                          |                                   | 4.32 |                 |  |

|                                                         | В           |                                     | I DD IM SIST                                                                                                           | T <sub>A</sub> = 85°C                                                           | 4.15                                          |                                   | 4.32 |                 |  |

|                                                         | Suffix      | .,                                  | V 405.V                                                                                                                | T <sub>A</sub> = 25°C                                                           | 4.2                                           | 4.25                              | 4.30 |                 |  |

|                                                         |             | V <sub>OC2</sub><br>Cell 2          | $V_{C1} = 4.05 \text{ V}$<br>$V_{DD} - V_{M} = 8.6 \text{ V}$                                                          | $T_A = -25^{\circ}C$                                                            | 4.15                                          |                                   | 4.32 |                 |  |

| Over-Charge                                             |             |                                     | DD W                                                                                                                   | $T_A = 85^{\circ}C$                                                             | 4.15                                          |                                   | 4.32 | V               |  |

| Detect Threshold (Rising)                               |             | W                                   | \/ 4.0E\/                                                                                                              | T <sub>A</sub> = 25°C                                                           | 4.18                                          | 4.22                              | 4.25 | ] '             |  |

|                                                         |             | V <sub>OC1</sub><br>Cell 1          | $V_{C2} = 4.05 \text{ V}$<br>$V_{DD} - V_{M} = 8.6 \text{ V}$                                                          | T <sub>A</sub> = -25°C                                                          | 4.12                                          |                                   | 4.30 |                 |  |

|                                                         | С           |                                     | "                                                                                                                      | T <sub>A</sub> = 85°C                                                           | 4.12                                          |                                   | 4.25 |                 |  |

|                                                         | Suffix      | V <sub>OC2</sub><br>Cell 2          | $V_{C1} = 4.05 \text{ V}$<br>$V_{DD} - V_{M} = 8.6 \text{ V}$                                                          | T <sub>A</sub> = 25°C                                                           | 4.18                                          | 4.22                              | 4.25 |                 |  |

|                                                         |             |                                     |                                                                                                                        | $T_A = -25^{\circ}C$                                                            | 4.12                                          |                                   | 4.30 |                 |  |

|                                                         |             |                                     |                                                                                                                        | T <sub>A</sub> = 85°C                                                           | 4.12                                          |                                   | 4.25 |                 |  |

|                                                         | D<br>Suffix | V <sub>OC1</sub><br>Cell 1          | $V_{C2} = 4.05 \text{ V}$<br>$V_{DD} - V_{M} = 8.6 \text{ V}$                                                          | T <sub>A</sub> = 25°C                                                           | 4.28                                          | 4.32                              | 4.35 |                 |  |

|                                                         |             |                                     |                                                                                                                        | T <sub>A</sub> = -25°C                                                          | 4.22                                          |                                   | 4.40 |                 |  |

|                                                         |             |                                     |                                                                                                                        | T <sub>A</sub> = 85°C                                                           | 4.22                                          | 4.00                              | 4.35 |                 |  |

|                                                         |             | V <sub>OC2</sub>                    | V <sub>C1</sub> = 4.05 V                                                                                               | T <sub>A</sub> = 25°C                                                           | 4.28                                          | 4.32                              | 4.35 |                 |  |

|                                                         |             | Cell 2                              | $V_{DD} - V_{M} = 8.6 \text{ V}$                                                                                       | $T_A = -25$ °C<br>$T_A = 85$ °C                                                 | 4.22<br>4.22                                  |                                   | 4.40 | 4               |  |

| Over-Charge Threshold Difference                        |             |                                     |                                                                                                                        | 1A = 65 C                                                                       | 4.22                                          |                                   | 20   | -               |  |

|                                                         | Cell 1      | V <sub>OC1</sub> - V <sub>OC2</sub> |                                                                                                                        | V <sub>C2</sub> = 4.05 V                                                        |                                               |                                   | 10   | m\              |  |

| Over-Charge Detect Threshold<br>Hysteresis <sup>c</sup> | Cell 2      | V <sub>OC_H1</sub>                  | $V_{DD} - V_{M} = 8.6 V$                                                                                               | V <sub>C2</sub> = 4.05 V<br>V <sub>C1</sub> = 4.05 V                            |                                               |                                   | 10   | 1111            |  |

|                                                         | Cell 1      | V <sub>OC_H2</sub>                  |                                                                                                                        | V <sub>C1</sub> = 4.05 V<br>V <sub>C2</sub> = 2.6 V                             | 2.1                                           | 2.2                               | 2.3  | ₩               |  |

| Over-Discharge<br>Detect Threshold (Falling)            | Cell 2      | V <sub>ODC2</sub>                   | •                                                                                                                      | V <sub>C1</sub> = 2.6 V                                                         | 2.1                                           | 2.2                               | 2.3  | _ v             |  |

|                                                         | Cell 1      | I <sub>BAL1</sub>                   | $V_M = V_{SS}$                                                                                                         | V <sub>C1</sub> = 4.4 V, V <sub>C2</sub> = 4.05 V                               | 9                                             | 15                                | 30   | $+\!\!-\!\!\!-$ |  |

| Cell Balancing Current                                  | Cell 2      | I <sub>BAL2</sub>                   |                                                                                                                        | V <sub>C2</sub> = 4.4 V, V <sub>C1</sub> = 4.05 V                               | 9                                             | 15                                | 30   | 4               |  |

| Timer Charge Current                                    |             | I <sub>TIMER(C)</sub>               | V <sub>C2</sub> = 3.3 V, V <sub>M</sub> = V <sub>SS</sub><br>V <sub>C</sub> = V <sub>SS</sub> , T <sub>A</sub> = 25°C  |                                                                                 |                                               | -0.5                              |      | μA              |  |

| Timer Discharge Current                                 |             | I <sub>TIMER(D)</sub>               | $V_{DD} - V_{C} =$                                                                                                     | = 3.3 V, V <sub>DD</sub> = V <sub>M</sub><br>= 6.1 V, T <sub>A</sub> = 25°C     |                                               | 1.0                               |      | m/              |  |

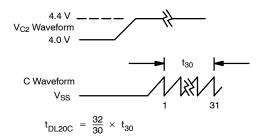

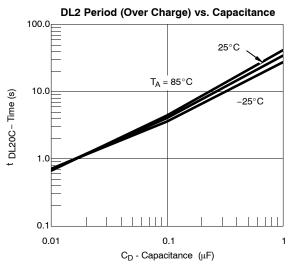

| DL2 Time (Over-Charge)                                  |             | t <sub>DL2OC</sub>                  | $C_D = 500 \text{ pF}, T_D$                                                                                            | V, V <sub>DD</sub> – V <sub>M</sub> = 10 V<br><sub>A</sub> = 25°C, See Figure 4 | 27                                            | 40                                | 60   | ms              |  |

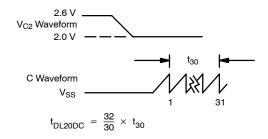

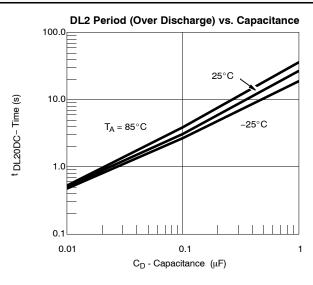

| DL2 Time (Over-Discharge)                               |             | t <sub>DL2ODC</sub>                 | $V_{C1} = 2.6 \text{ V}, V_{M} = V_{SS}, C_{D} = 500 \text{ pF}$<br>$T_{A} = 25^{\circ}\text{C}, \text{ See Figure 5}$ |                                                                                 | 27                                            | 40                                | 60   |                 |  |

| External Short Circuit Sense Current                    |             | I <sub>VMSHORT</sub>                |                                                                                                                        | = 4.4 V, V <sub>M</sub> = V <sub>DD</sub>                                       | 30                                            |                                   | 300  | μA              |  |

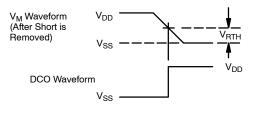

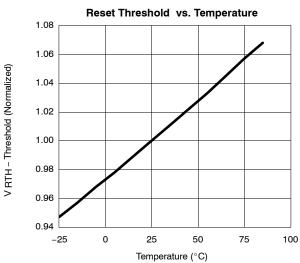

| Reset Threshold                                         |             | V <sub>RTH</sub>                    |                                                                                                                        | 4.05 V, See Figure 3                                                            | 42                                            | 60                                | 100  | m\              |  |

| Center Tap, Average Bias Currer                         | t           | I <sub>VC</sub>                     |                                                                                                                        | = 4.05 V, V <sub>M</sub> = V <sub>DD</sub>                                      | -2                                            |                                   | 2    | μA              |  |

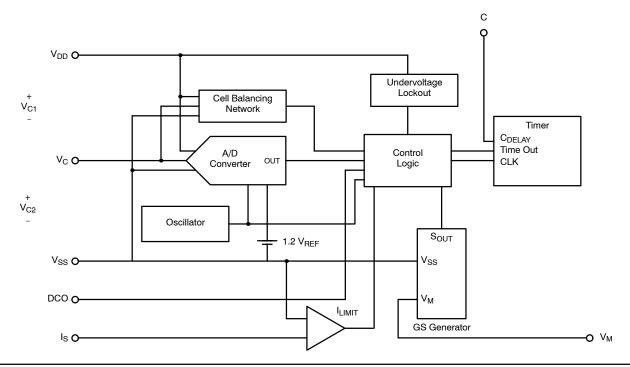

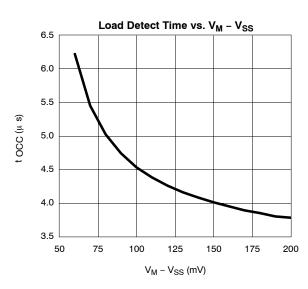

| Overcharge Load Detect                                  |             | tocc                                | $C_{L} = 500 \text{ pF, DC}$                                                                                           | 4.4 V, C <sub>D</sub> = 500 pF<br>O to V <sub>SS,</sub> See Figure 1            |                                               |                                   | 40   | με              |  |

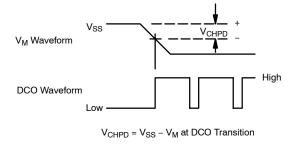

| Power-Down Charger Detect Thr                           | eshold      | V <sub>CHPD</sub>                   | V <sub>C1</sub> = 2 V, V <sub>C2</sub> = 2.4 V, See Figure 6                                                           |                                                                                 |                                               |                                   | 1.1  | V               |  |

| DCO Pulse Width                                         |             | t <sub>PW</sub>                     | $C_1 = 500 \text{ pF, DC}$                                                                                             | O to V <sub>SS</sub> , See Figure 7                                             |                                               | 520                               | ·    | με              |  |

- Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

c. Guaranteed by design, not subject to production test.

#### **TIMING DIAGRAMS**

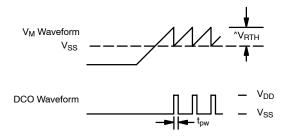

FIGURE 1. OC Load Detect

FIGURE 2. Current-Limit Comparator Response Time

FIGURE 3. Reset Threshold

$V_{RTH} = V_{M} - V_{SS}$  at DCO Transition

FIGURE 4. DL2 Time (Over-Charge)

FIGURE 5. DL2 Time (Over-Discharge)

FIGURE 6. Power-Down Charger Detect Threshold

FIGURE 7. Load Detection in Overcharge Mode

### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

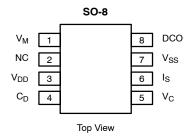

### **PIN CONFIGURATION**

| ORDERING INFORMATION        |                         |              |  |  |  |  |  |

|-----------------------------|-------------------------|--------------|--|--|--|--|--|

| Part Number                 | V <sub>OC1/2</sub> Typ. | Temp Range   |  |  |  |  |  |

| Si9730ABY-T1                | 4 20 V                  |              |  |  |  |  |  |

| Si9730ABY-T1—E3 (Lead Free) | 4.20 V                  |              |  |  |  |  |  |

| Si9730BBY-T1                | 4.25 V                  | –25° to 85°C |  |  |  |  |  |

| Si9730BBY-T1—E3 (Lead Free) | 4.25 V                  |              |  |  |  |  |  |

| Si9730CBY-T1                | 4.22 V                  | 20 10 00 0   |  |  |  |  |  |

| Si9730CBY-T1—E3 (Lead Free) | 4.22 V                  |              |  |  |  |  |  |

| Si9730DBY-T1                | 4.32 V                  |              |  |  |  |  |  |

| Si9730DBY-T1—E3 (Lead Free) | 4.52 V                  |              |  |  |  |  |  |

| PIN DESCRIPTION |                |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin<br>Number   | Symbol         | Description                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 1               | $V_{M}$        | Negative Battery Pack Terminal - connection for external negative terminal of the battery pack.                                                                                                                                                                       |  |  |  |  |  |

| 2               | NC             | No Connection, do not connect this pin.                                                                                                                                                                                                                               |  |  |  |  |  |

| 3               | $V_{DD}$       | Dual Cell Positive Terminal - connection for positive terminal of dual series connected Lil+ cells.                                                                                                                                                                   |  |  |  |  |  |

| 4               | C <sub>D</sub> | Delay Capacitor Connection - an external capactior connected across C <sub>D</sub> and Vss allows additional charge time (DL2, see Detailed Description) after a charge error has occured. Suggested capacitor values are shown in DL2 Period vs. Capacitance Curves. |  |  |  |  |  |

| 5               | V <sub>C</sub> | Dual Cell Center Tap Connection - monitors individual battery voltages for overcharge and overdischarge errors.                                                                                                                                                       |  |  |  |  |  |

| 6               | Is             | Current Sense Comparator Input - monitors load current for short circuit conditions . If V <sub>ILIMIT</sub> is exceeded, then DCO opens the low-side switch, disconnecting the cells.                                                                                |  |  |  |  |  |

| 7               | $V_{SS}$       | Dual Cell Negative Terminal - connection for negative terminal of dual series connected Lil+ cells.                                                                                                                                                                   |  |  |  |  |  |

| 8               | DCO            | Low-side Switch Gate Driver Output - drives the gate of two external source connected in-channel MOSFETs. DCO swings from V <sub>OL</sub> to V <sub>DD</sub> .                                                                                                        |  |  |  |  |  |

# VISHAY

## **Vishay Siliconix**

#### **DETAILED DESCRIPTION**

#### Overview

The purpose of the Si9730 is to safely and reliably control the charging and discharging of a two-cell lithium-ion battery (carbon or coke chemistry). It provides protection against all possible fault conditions, including:

- external short circuits

- · reversed charger

- overcharged cell or cells

- undervoltage

- battery open center-tap

#### **General Concepts**

The Si9730 operates by connecting or disconnecting the negative terminal of the battery to the negative side of the load and/or charger (see Figure 8); that is, it does ground side switching. It is important to bear the distinction between these two "grounds" in mind in order to understand the operation of the Si9730. The switching is accomplished by controlling two "back-to-back" MOSFETs: having the two MOSFETs in this arrangement is mandatory to ensure that current cannot flow in either direction when the MOSFETs are off. To turn the switch on, the Si9730 applies a gate-source voltage to both MOSFETs (from the DCO pin) that is high with respect to the sources. The Si9730 DCO signal is referenced to the V<sub>M</sub> pin while the battery is being charged, and to the Vss pin while the battery is being discharged. The Si9730 causes the DCO to be referenced to the lower of the two voltages. This prevents the switch from turning on or off unintentionally.

The Si9730 is designed to operate only with a current-limited lithium-ion battery charger. Specifically, the battery charger must have an open-circuit voltage that does not exceed the absolute maximum IC voltage, and it must have a limited short-circuit current that does not exceed the allowed charging current of the battery.

The following descriptions cover all the common operational scenarios; additional information on unusual battery conditions can be found in the state transition table.

#### **Normal Charging**

The cells are in normal charging conditions if a) both cells are above the Over-Discharge Detect Threshold ( $V_{ODC} \sim 2.2 \text{ V}$ ); b) both cells are under the Over-Charge Detect Threshold

( $V_{OC} \sim$  4.2 V); and c) the center tap is connected to the  $V_C$  pin. When a charger is present in these conditions, the switch will be on, charging the cells at the current limit of the charger.

#### **Normal Discharging**

The cells are in normal discharging conditions if a, b, and c above are satisfied, and if in addition d) the load current is less than the discharge current limit. With no charger present, the switch will be on, discharging the cells and powering the load.

#### Overcharged Cell(s) Charging

The most destructive condition that a LiI+ cell can experience is overcharging. If the cell becomes overcharged beyond its recommended limits, it can become permanently disabled.

If one or both cells rise above the over-charge detect threshold ( $V_{\rm OC1}$  and  $V_{\rm OC2}$ ), and a charger is present, the Si9730 will open the switch (to prevent further charging) and begin bleeding off charge (15- $\mu$ A typical) from the overcharged cell or cells.

The details of this operation depend on the fact that the voltage level of lithium-ion batteries drops for a short time after charging ceases (due to momentary changes in battery chemistry, ESR, etc.). Because of this recovery, the Si9730 allows the battery to continue charging for a short time (the overcharge time,  $t_{DL2OC}$ ). This additional charge time only occurs if the overcharge condition persists for more than 8 msec (two periods of an internal 4msec oscillator).  $T_{DL2OC}$  is determined by the capacitor attached to the  $C_D$  pin, see Figure 8.

Once the overcharge time has ended, the switch is opened, preventing the battery from further overcharging. Now, the Si9730 begins bleeding current off the overcharged cell or cells ( $I_{BAL1}$  and  $I_{BAL2}$ ), as long as a charger is present. Eventually, the cell(s) will return into their normal range, and charging will begin, starting the whole cycle over again.

#### Overcharged Cell(s) Discharging

If one or more cells is overcharged, and a load is connected, the switch is turned on, permitting the battery to power the load.

#### Over-Discharged Cell(s) Discharging

Repeated over-discharging of Lil+ cells can cause irreversible reactions in the cells which lead to decreased cycle life.

To avoid this, if one or both cells becomes over-discharged ( $V_{CELL} < V_{ODC}$ ) and no charger is present, the Si9730 opens the switch to prevent further discharging, and goes into a shutdown mode in which it draws minute power from the battery ( $I_{DD\ UVL} < 1\ \mu A$ ).

#### Over-Discharged Cell(s) Charging

If one or both cells is over-discharged, and a charger is present, charging can begin, and so the Si9730 closes the switch. However, removal of the charger in this condition could potentially damage the battery if the removal is not recognized and the cells are discharged. Since the voltage drop across the switch is small, the Si9730 actually cycles the switch at a 7/8 duty cycle; during the 1/8 time when the switch is open, the IC checks that the charger is still present.

Once both cells are back into the normal operating range, normal charging resumes.

#### **Undervoltage Charging**

If for some reason the battery drops below about 3.7 V ( $V_{UVL}$ ), there is insufficient voltage for the Si9730 to properly monitor fault conditions. Of course, the switch is already open, since  $V_{UVL} < V_{ODC} \times 2$ . However, when a charger is detected, the Si9730 recovers and goes into an undervoltage mode. (A charger is detected if the  $V_S$  pin is higher than the  $V_M$  pin by at least  $V_{CHPD} = 1.1$  V, see Figure 6). In this undervoltage mode, the switch is on at a 1/8 duty cycle, to limit the power dissipation across the switch, and, again, to detect the continuing presence of the charger.

Once the battery voltage is above  $V_{\text{UVL}}$ , the charging continues in the over-discharged state.

#### **Output Short**

If too much current is drawn from the battery due to a load short, the switch must be opened quickly to prevent damage to the battery. The Si9730 monitors the load current by looking at the voltage across an external sense resistor (see Figure 8). If the voltage across the sense resistor exceeds  $V_{\rm ILIMIT}\sim28$  mV, the switch is opened. The Si9730 leaves the switch open until the load is *completely* removed.

Of course, the IC must have some way of detecting that the load has been removed. For this purpose, a small current ( $I_{VMSHORT}$ ) passes through the Si9730, from pin  $V_M$  to pin  $V_{SS}$  once the short is detected and the switch is turned off. The

$I_{VMSHORT}$  current causes the voltage on the  $V_M$  pin to equal the voltage on the  $V_{DD}$  pin while the short is present, or the voltage on the  $V_M$  pin to equal the voltage on the  $V_{SS}$  pin if the short is removed. If the short is not removed,  $I_{VMSHORT}$  current will continue to flow until the battery voltage becomes overdischarged. Once the short is removed, the IC is allowed to turn the switch back on.

The current limit threshold has a temperature coefficient of 0.18%/°C. This can partially compensate for a copper circuit board trace being used as the sense resistor.

#### **Open Center Tap**

An open center tap is a mechanical failure of the battery pack such that the Si9730's  $V_{\rm C}$  pin is disconnected from the center point of the two-cell battery. If this connection is open, the IC opens the switch, as it cannot measure the cell voltages in this condition. The switch is left open until connection is re-established. If the battery is under-voltaged and the charger is present in this case, the battery is allowed to charge even with the center tap open. In this state, batteries are almost impossible to damage by 1/8 duty cycle charging. Once the battery voltage reaches the over-discharged voltage, the switch is turned off.

#### **State Transition Table**

The number of different states of the Si9730 can seem overwhelming at first. This state transition table will help to organize thinking about the different operational conditions of the IC, by listing each possible transition from one condition to another.

Reading the table is straightforward. There are two cells constituting the battery, one with its positive terminal connected to  $V_{DD}$  and its negative terminal connected to  $V_{C}$ , referred to as the high cell (see Figure 8); and one cell with its positive terminal connected to  $V_{C}$  and its negative terminal connected to  $V_{SS}$ , referred to as the low cell. Each cell can be in one of three voltages:

- Over-discharge (ODC), where V<sub>CELL</sub> < V<sub>ODC</sub>;

- Normal Operation (NO), where V<sub>ODC</sub> < V<sub>CELL</sub> < V<sub>OC</sub>;

or

• Overcharge (OC), where V<sub>OC</sub> < V<sub>CELL</sub>.

Additionally, the battery as a whole can be undervoltage (UV), where  $V_{BATTERY} < V_{UVL}$ . Note that this final condition is not necessarily (though normally) mutually exclusive with the other cell conditions: if one cell were at 0V, the other cell could be in NO, and the battery could still be in UV.

The charger can be either present (ON) or not present (OFF); the "X" in the table means the condition is true regardless of the

state of the charger. The load current can be either 0, normal (0 <  $I_{LOAD}$  <  $I_{ILIMIT}$ ) or a short ( $I_{ILIMIT}$  <  $I_{LOAD}$ ) where  $I_{ILIMIT}$  is set by  $V_{ILIMIT}/R_{SENSE}$ ; the "X" in the table refers to a load current that can be either 0 or normal. Finally, the switch can be either ON, OFF, or cycling at either 1/8 or 7/8 duty cycle, where the duty cycle refers to the portion of the period when the switch is on; the notation On–>On simply means that the switch does not change state, it remains on; the notation –>Off means that the switch turns off regardless of its previous state.

| High-Cell Voltage | Low-Cell Voltage | Charger On/Off | Load Current     | Switch State                   |

|-------------------|------------------|----------------|------------------|--------------------------------|

| NO                | NO               | Off>On         | Х                | On->On                         |

| NO->OC            | NO               | Off            | 0                | On->Off                        |

| NO                | NO->OC           | Off            | 0                | On->Off                        |

| NO->OC            | NO               | Off            | Normal           | Cycles at very high duty cycle |

| NO                | NO->OC           | Off            | Normal           | Cycles at very high duty cycle |

| OC                | NO               | Off->On        | X                | Off->Off                       |

| NO                | OC               | Off->On        | X                | Off->Off                       |

| OC                | OC               | Off->On        | Х                | Off->Off                       |

| NO                | NO               | Off            | Normal->Short    | On->Off                        |

| OC                | NO               | Off            | Normal->Short    | On->Off                        |

| NO                | OC               | Off            | Normal->Short    | On->Off                        |

| NO->ODC           | NO               | Off            | 0                | On->Off                        |

| NO                | NO->ODC          | Off            | 0                | On->Off                        |

| NO->ODC           | NO               | Off            | Normal           | On->Off                        |

| NO                | NO->ODC          | Off            | Normal           | On->Off                        |

| ODC               | NO               | Off->On        | X                | Off->Cycle at 7/8 duty cycle   |

| NO                | ODC              | Off->On        | X                | Off->Cycle at 7/8 duty cycle   |

| ODC               | ODC              | Off->On        | X                | Off->Cycle at 7/8 duty cycle   |

| U                 | İV               | Off->On        | X                | Off->Cycle at 1/8 duty cycle   |

| NO->ODC           | OC               | Off            | 0                | Cycle->Off                     |

| OC                | NO->OC           | Off            | 0                | Off                            |

| NO                | NO               | V<0            | X                | Off                            |

| U                 | ÏV               | On             | Center Tap->Open | Cycle at 1/8 duty cycle        |

| ODC               | ODC              | Х              | Center Tap->Open | >Off                           |

| NO                | ODC              | X              | Center Tap->Open | >Off                           |

| ODC               | NO               | X              | Center Tap->Open | >Off                           |

| NO                | NO               | X              | Center Tap->Open | >Off                           |

| OC                | OC               | X              | Center Tap->Open | −.>Off                         |

#### **APPLICATION CIRCUIT**

FIGURE 8. Typical 2 -Cell Circuit

#### **General Considerations**

Figure 8 shows a typical application of the Si9730, controlling a 2-cell lithium-ion battery (carbon or coke chemistry). Specifics of the selection of MOSFETs, current sensing resistor, and output capacitor are detailed below. In addition, there are several typical features of this circuit to be observed.

First, each connection from a cell to the IC has a 100- $\Omega$  resistor in series with it. The purpose of the resistor is to ensure that in the unlikely event of the IC shorting, the cells themselves will not see a short. The maximum size of this resistance is set by the current drain of the IC; for example, the  $V_{DD}$  pin draws a maximum of 60  $\mu$ A, which will drop V = 60  $\mu$ A \* 100  $\Omega$  = 6 mV

across the resistor. This drop constitutes an error in the measured cell voltage, and so the resistor must be small enough that the error voltage is acceptable.

A second typical feature demonstrated in Figure 8 is the current sense filter formed by RIS and C2. This provides a noise filter, to prevent the Si9730 from opening the connection to the battery if there is noise on its current sense pin. It also causes a delay in the response of the IC to a genuine overcurrent, the amount of the delay being inversely proportional to the amount of overcurrent, since the Is pin senses a voltage. Increasing this filter's time constant could be used to allow short-time surges of current out of the battery without compromising its ability to protect the battery.

#### **Output Capacitor**

Depending on the MOSFET selected, the Si9730 can open the switch quite rapidly, in a matter of a few microseconds. However, the various monitoring operations take 10-100 times longer than this, and the basic period of the Si9730's oscillator is 4 msec. In order to prevent false readings by the Si9730, it is necessary to attach a capacitor across the output of the battery charger/load (this is *not* in parallel with the battery, because of the switch). A  $10\mbox{-}\mu\text{F}$  capacitor is recommended for this purpose; see Figure 8.

#### **Selecting a Current Sense Resistor**

The current sense resistor should be selected based on the maximum current the battery can source or charge at; above this current, the Si9730 will open the switch, disconnecting the battery from its load or charger.

$$R_{sense} = V_{ILIMIT}/I_{ILIMIT} \approx 28 \text{ mV/}I_{ILIMIT}$$

Of course, the resistor must be rated to take the power dissipated in it as well:

$$P_{RSENSE} = I_{ILIMIT} V_{ILIMIT} \approx 28 \text{ mV} * I_{ILIMIT}$$

For example, suppose that the maximum current the battery will see is 1.8 A. Then,  $I_{LIMIT}$  might be chosen to be 2 A. We would then select a resistor of

$$R_{SENSE} = 28 \text{ mV/2 A} = 14 \text{ m}\Omega.$$

The power dissipation in this resistor is

and so a 100mW surface mount resistor would be suitable.

Another possibility is to use a thin copper trace as the sense resistor. The copper has a temperature coefficient of 0.39%/°C, but this is partially compensated for by the temperature coefficient of the current limit comparator in the Si9730, which is 0.18%/°C. A simple formula for selecting a trace to act as a current sensor is:

$$R = 0.5 \text{ m}\Omega \times \frac{\text{length}}{\text{width}} (1 \text{ oz. Copper})$$

For example, to get a  $14\text{-m}\Omega$ . resistor, we need length/width = 28; with a trace width of 0.01", the length of the trace should be 0.28".

#### **MOSFET Selection**

Two MOSFETs in series, with their sources and gates connected together, are used as the switch. This prevents current from flowing in either direction when the gate is low; if only one MOSFET were used, the body diode could conduct current in the opposing direction.

LITTLE FOOT MOSFETs are recommended for this application, because of their size, performance and cost benefits. SO-8 and TSSOP-8 MOSFETs allow for space efficient designs with performance equal to or better than their DPAK and TO-220 predecessors. Further, their availability from multiple sources permits a cost effective solution.

There are two important parameters to consider in MOSFET selection: gate threshold voltage; and on-resistance, which determines power dissipation.

Even when the DCO pin of the Si9730 is low, the specification allows its value to be as high as 0.4 V. If this voltage were close to the gate threshold voltage, leakage current through the MOSFETs could be hundreds of microamps, which would result in the battery quickly becoming discharged. To ensure that leakage is minimized, n-channel MOSFETs with a minimum gate threshold voltage of 0.8 V should be chosen.

On resistance of the MOSFETs needs to be selected to limit power dissipation into the MOSFETs' package. For example, a dual MOSFET SO-8 package is rated at 2 W, and a dual MOSFET TSSOP-8 package is rated at 1 W (both at 25°C; if the ambient temperature is higher, the allowable power dissipation in these packages is less). For example, if the maximum current is 2 A, and a dual MOSFET SO-8 package is being used, the maximum on-resistance of the two MOSFETs in series must not exceed

$$1 W = (2 A)^2 * R_{ON}$$

or  $R_{ON}$  = 0.25  $\Omega$ ; each MOSFET can be allotted half of this,  $R_{ON}$  = 125  $m\Omega.$  Account must also be taken of the fact that MOSFETs' on-resistance is a function of temperature; a conservative approach would give a discount of 1/3,  $R_{ON}$  = 125  $m\Omega$  \* (2/3) = 80  $m\Omega$  per MOSFET.

A list of recommended MOSFETs, which Vishay Silicoix supplies, follows.

| N-CHANNEL MOSFET SELECTION GUIDE |                                                      |                                                      |                    |                         |         |         |                                                  |  |

|----------------------------------|------------------------------------------------------|------------------------------------------------------|--------------------|-------------------------|---------|---------|--------------------------------------------------|--|

| Part<br>Number                   | r <sub>DS (on)</sub> (Ω) @<br>V <sub>GS</sub> = 10 V | r <sub>DS(on)</sub> (Ω) @<br>V <sub>GS</sub> = 4.5 V | I <sub>D</sub> (A) | V <sub>GS(th)</sub> (V) | Config. | Package | Recommended<br>Application Current<br>(A) @ 25°C |  |

| Si4410DY                         | 0.0135                                               | 0.020                                                | 10                 | 1.0                     | Single  | SO-8    | 9                                                |  |

| Si4412DY                         | 0.028                                                | 0.042                                                | 7                  | 1.0                     | Single  | SO-8    | 6.3                                              |  |

| Si6434DQ                         | 0.028                                                | 0.042                                                | 5.6                | 1.0                     | Single  | TSSOP-8 | 4.9                                              |  |

| Si4936DY                         | 0.037                                                | 0.055                                                | 5.8                | 1.0                     | Dual    | SO-8    | 3.5                                              |  |

| Si9936DY                         | 0.050                                                | 0.080                                                | 5                  | 1.0                     | Dual    | SO-8    | 2.9                                              |  |

| Si6954DQ                         | 0.065                                                | 0.095                                                | 3.9                | 1.0                     | Dual    | TSSOP-8 | 1.9                                              |  |

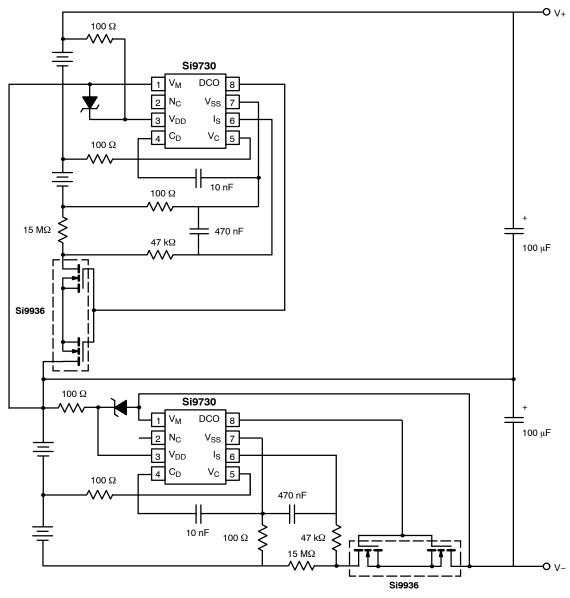

FIGURE 9. 4-Cell Battery Circuit

#### Four Cell Application

Figure 9 shows a method for using the Si9730 in a 4-cell application. Basically, this is two complete 2-cell circuits stacked in series. Each half of the complete circuit monitors its own 2-cell portion of the battery, and opens its own MOSFET switch under any of the appropriate conditions. Observe that the total percent power loss in this circuit is identical to that in the 2-cell application; although there are now two sets of MOSFETs in series, there is also double the battery voltage, and so total efficiency is the same.

One novel feature of this 4-cell circuit is the increase in the size of the bypass capacitors. Each half of the circuit retains its own output cap, to reduce noise seen by the circuit. Since the two halves interact with each other (when one opens its switch, the other one is also opened), there can be additional noise, which must be rejected for proper operation. The capacitors have been increased to 100  $\mu F$  for this reason; remember that they must be rated to take the full maximum voltage rating of the charger, not half of it, since if one switch is closed and the other open, the charger (minus two cells' voltage drop, which might be zero) is applied across the other capacitor.

A second addition on this circuit is the (optional) two zeners, one each for each Si9730, placed from  $V_{DD}$  to  $V_{M}.$  These are necessary only if the charger voltage is higher than the 15-V absolute maximum of the IC plus two cells' voltage drop. Just as with the capacitor, if one switch is open and the other closed, the IC will see this charger voltage, and must be protected. The power rating of the zener can be inferred by observing that the current through it is limited by the  $100\mbox{-}\Omega$

resistor. A tradeoff can be made here between the power rating of the zener, which can be decreased by increasing the resistor value, and the accuracy of the voltage measurement by the Si9730, which can be increased by decreasing the resistor value.

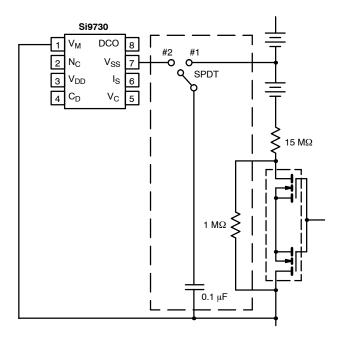

#### Reset from Shutdown

There are two specialized conditions that can place the Si9730 in shutdown mode. The first condition can occur when the circuit is first attached to a battery in the factory. When the IC comes up, it will be in the undervoltage shutdown mode. The Si9730 may also enter this mode when the ambient temperature drops and the battery is nearly in UV. When the temperature drops, the battery pack voltage will drop and the IC may enter the shutdown mode. In either case, the Si9730 must be reset by raising the  $V_{\rm SS}$  pin higher than the  $V_{\rm M}$  pin by  $V_{\rm CPHD}$ . Figure 10 shows a circuit that resets the circuit once it has entered the shutdown mode.

The circuit works by initially connecting the 0.1- $\mu$ F capacitor to the battery's center tap and placing the switch in position #1. Although the MOSFETs are open, the 1-m $\Omega$  resistor is sufficient to allow the capacitor to charge up in about 300-400 msec. Once the capacitor is charged, the switch is placed in position #2, momentarily making V<sub>SS</sub> higher than V<sub>M</sub>, thus placing the Si9730 in the normal operating mode. The entire circuit provides a leakage of only a few microamps, which is much lower than the self discharge current of the Lilon battery.

FIGURE 10. Factory Startup Circuit