# LMU18

## 16 x 16-bit Parallel Multiplier

#### **FEATURES**

- ☐ 35 ns Worst-Case Multiply Time

- ☐ Low Power CMOS Technology

- ☐ Full 32-bit Output Port No Multiplexing Required

- ☐ Two's Complement, Unsigned, or Mixed Operands

- ☐ Three-State Outputs

- 84-pin PLCC, J-Lead

### **DESCRIPTION**

The **LMU18** is a high-speed, low power 16-bit parallel multiplier. The LMU18 is an 84-pin device which provides simultaneous access to all outputs.

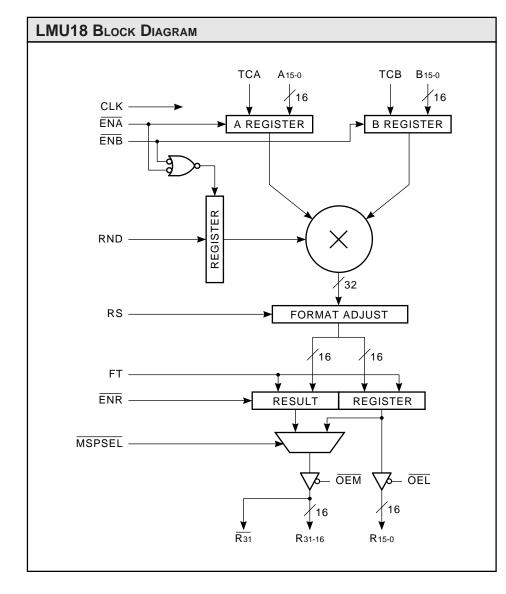

The LMU18 produces the 32-bit product of two 16-bit numbers. Data present at the A inputs, along with the TCA control bit, is loaded into the A register on the rising edge of CLK. B data and the TCB control bit are similarly loaded. Loading of the A and B registers is controlled

1

by the  $\overline{\text{ENA}}$  and  $\overline{\text{ENB}}$  controls. When HIGH, these controls prevent application of the clock to the respective register. The TCA and TCB controls specify the operands as two's complement when HIGH, or unsigned magnitude when LOW.

RND is loaded on the rising edge of CLK, providing either ENA or ENB are LOW. RND, when HIGH, adds '1' to the most significant bit position of the least significant half of the product. Subsequent truncation of the 16 least significant bits produces a result correctly rounded to 16-bit precision.

At the output, the Right Shift control (RS) selects either of two output formats. RS LOW produces a 31-bit product with a copy of the sign bit inserted in the MSB postion of the least significant half. RS HIGH gives a full 32-bit product. Two 16-bit output registers are provided to hold the most and least significant halves of the result (MSP and LSP) as defined by RS. These registers are loaded on the rising edge of CLK, subject to the ENR control. When ENR is HIGH, clocking of the result registers is prevented.

For asynchronous output these registers may be made transparent by setting the feed through control (FT) HIGH and ENR LOW.

The two halves of the product may be routed to a single 16-bit three-state output port (MSP) via a multiplexer. MSPSEL LOW causes the MSP outputs to be driven by the most significant half of the result. MSPSEL HIGH routes the least significant half of the result to the MSP pins. The MSB of the result is available in both true and complemented form to aid implementation of higher precision multipliers.

### 16 x 16-bit Parallel Multiplier

### FIGURE 1A. INPUT FORMATS

AIN

BIN

Fractional Two's Complement (TCA, TCB = 1)

Integer Two's Complement (TCA, TCB = 1) -

Unsigned Fractional (TCA, TCB = 0)

Unsigned Integer (TCA, TCB = 0) −

### FIGURE 1B. OUTPUT FORMATS

**MSP**

LSP

Fractional Two's Complement (RS = 0) -

15 14 13

$$\rightleftharpoons$$

2 1 0

-2<sup>0</sup> 2<sup>-16</sup> 2<sup>-17</sup> 2<sup>-28</sup> 2<sup>-29</sup> 2<sup>-30</sup>

(Sign)

- Fractional Two's Complement (RS = 1) -

Integer Two's Complement (RS = 1) —

| 15              | 14              | 13              | #   | 2                     | 1              | 0                     |

|-----------------|-----------------|-----------------|-----|-----------------------|----------------|-----------------------|

| 2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> | _,_ | <b>2</b> <sup>2</sup> | 2 <sup>1</sup> | <b>2</b> <sup>0</sup> |

─ Unsigned Fractional (RS = 1) ——

Unsigned Integer (RS = 1)

## 16 x 16-bit Parallel Multiplier

| MAXIMUM RATINGS Above which useful life may be impaired (Notes 1, 2, 3, 8) |                  |  |  |  |  |  |  |

|----------------------------------------------------------------------------|------------------|--|--|--|--|--|--|

| Storage temperature                                                        | 65°C to 1150°C   |  |  |  |  |  |  |

| Storage temperature                                                        |                  |  |  |  |  |  |  |

| Operating ambient temperature                                              | –55°C to +125°C  |  |  |  |  |  |  |

| VCC supply voltage with respect to ground                                  | 0.5 V to +7.0 V  |  |  |  |  |  |  |

| Input signal with respect to ground                                        | 3.0 V to +7.0 V  |  |  |  |  |  |  |

| Signal applied to high impedance output                                    | -3.0 V to +7.0 V |  |  |  |  |  |  |

| Output current into low outputs                                            | 25 mA            |  |  |  |  |  |  |

| Latchup current                                                            | > 400 mA         |  |  |  |  |  |  |

|                                                                            |                  |  |  |  |  |  |  |

| <b>OPERATING CONDITIONS</b> To m | eet specified electrical and switching characteristics |

|----------------------------------|--------------------------------------------------------|

|----------------------------------|--------------------------------------------------------|

ModeTemperature Range (Ambient)Supply VoltageActive Operation, Commercial $0^{\circ}$ C to  $+70^{\circ}$ C $4.75 \text{ V} \leq \text{V} \text{CC} \leq 5.25 \text{ V}$ Active Operation, Military $-55^{\circ}$ C to  $+125^{\circ}$ C $4.50 \text{ V} \leq \text{V} \text{CC} \leq 5.50 \text{ V}$

| ELECTRICAL CHARACTERISTICS Over Operating Conditions (Note 4) |                        |                                               |     |     |     |      |  |  |  |

|---------------------------------------------------------------|------------------------|-----------------------------------------------|-----|-----|-----|------|--|--|--|

| Symbol                                                        | Parameter              | Test Condition                                | Min | Тур | Max | Unit |  |  |  |

| <b>V</b> OH                                                   | Output High Voltage    | <b>V</b> CC = Min., <b>I</b> OH = -2.0 mA     | 2.4 |     |     | V    |  |  |  |

| <b>V</b> OL                                                   | Output Low Voltage     | VCC = Min., IOL = 8.0 mA                      |     |     | 0.5 | V    |  |  |  |

| <b>V</b> IH                                                   | Input High Voltage     |                                               | 2.0 |     | Vcc | V    |  |  |  |

| <b>V</b> IL                                                   | Input Low Voltage      | (Note 3)                                      | 0.0 |     | 0.8 | V    |  |  |  |

| lıx                                                           | Input Current          | Ground ≤ VIN ≤ VCC (Note 12)                  |     |     | ±20 | μΑ   |  |  |  |

| loz                                                           | Output Leakage Current | Ground ≤ <b>V</b> OUT ≤ <b>V</b> CC (Note 12) |     |     | ±20 | μΑ   |  |  |  |

| ICC1                                                          | Vcc Current, Dynamic   | (Notes 5, 6)                                  |     | 25  | 45  | mA   |  |  |  |

| ICC2                                                          | Vcc Current, Quiescent | (Note 7)                                      |     |     | 1.5 | mA   |  |  |  |

## 16 x 16-bit Parallel Multiplier

### **SWITCHING CHARACTERISTICS**

| COMMERCIAL OPERATING RANGE (0°C to +70°C) Notes 9, 10 (ns) |                                            |     |             |     |     |     |     |        |    |  |  |

|------------------------------------------------------------|--------------------------------------------|-----|-------------|-----|-----|-----|-----|--------|----|--|--|

|                                                            |                                            |     | LMU18-      |     |     |     |     |        |    |  |  |

|                                                            |                                            | 6   | ///// 4//// |     |     |     | 35  | 20*    |    |  |  |

| Symbol                                                     | Parameter                                  | Min | Max         | Min | Max | Min | Max | ax Min |    |  |  |

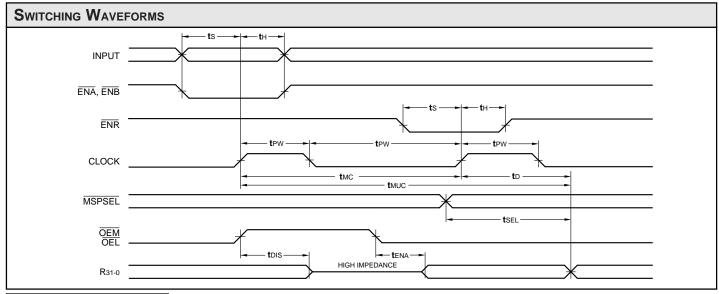

| tMC                                                        | Clocked Multiply Time                      |     | 65          |     | 45  |     | 35  |        | 20 |  |  |

| <b>t</b> MUC                                               | Unclocked Multiply Time                    |     | 85          |     | 65  |     | 55  |        | 30 |  |  |

| <b>t</b> PW                                                | Clock Pulse Width                          | 15  |             | 15  |     | 15  |     | 9      |    |  |  |

| ts                                                         | Input Setup Time                           | 15  |             | 15  |     | 12  |     | 11     |    |  |  |

| tH                                                         | Input Hold Time                            | 5   |             | 5   |     | 5   |     | 1      |    |  |  |

| <b>t</b> D                                                 | Output Delay                               |     | 30          |     | 30  |     | 28  |        | 18 |  |  |

| <b>t</b> SEL                                               | Output Select Delay                        |     | 25          |     | 25  |     | 25  |        | 18 |  |  |

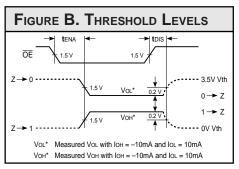

| <b>t</b> ENA                                               | Three-State Output Enable Delay (Note 11)  |     | 25          |     | 20  |     | 20  |        | 18 |  |  |

| <b>t</b> DIS                                               | Three-State Output Disable Delay (Note 11) |     | 24          |     | 20  |     | 20  |        | 18 |  |  |

| MILITARY OPERATING RANGE (-55°C to +125°C) Notes 9, 10 (ns) |                                            |      |          |    |       |    |       |       |        |  |  |

|-------------------------------------------------------------|--------------------------------------------|------|----------|----|-------|----|-------|-------|--------|--|--|

|                                                             |                                            |      | LMU18-   |    |       |    |       |       |        |  |  |

|                                                             |                                            | ///7 | 5*///    | 5  | 5*/// | 4  | 5*/// | ///2  | 5*///  |  |  |

| Symbol                                                      | Parameter                                  | Min  |          |    |       |    |       |       |        |  |  |

| tMC                                                         | Clocked Multiply Time                      |      | 75       |    | 55    |    | 45    |       | 25     |  |  |

| <b>t</b> MUC                                                | Unclocked Multiply Time                    |      | 95       |    | 85    |    | 65    |       | 38     |  |  |

| <b>t</b> PW                                                 | Clock Pulse Width                          | 20   |          | 15 |       | 15 |       | 10    |        |  |  |

| ts                                                          | Input Setup Time                           | 15   |          | 15 |       | 12 |       | 12    |        |  |  |

| tн                                                          | Input Hold Time                            | 5    |          | 5  |       | 5  |       | 2     |        |  |  |

| <b>t</b> D                                                  | Output Delay                               |      | 35       |    | 35    |    | 33    |       | 20     |  |  |

| <b>t</b> SEL                                                | Output Select Delay                        |      | 30       |    | 30    |    | 30    |       | 20     |  |  |

| <b>t</b> ENA                                                | Three-State Output Enable Delay (Note 11)  |      | 25       |    | 20    |    | 20    |       | 20     |  |  |

| tDIS                                                        | Three-State Output Disable Delay (Note 11) |      | 24       |    | 20    |    | 20    |       | 20     |  |  |

|                                                             |                                            |      | //////// |    |       |    |       | ///// | ////// |  |  |

\*DISCONTINUED SPEED GRADE

### 16 x 16-bit Parallel Multiplier

#### **NOTES**

- 1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.

- 2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

- 3. This device provides hard clamping of transient undershoot and overshoot. Input levels below ground or above **V**CC will be clamped beginning at -0.6 V and **V**CC + 0.6 V. The device can withstand indefinite operation with inputs in the range of -0.5 V to +7.0 V. Device operation will not be adversely affected, however, input current levels will be well in excess of 100 mA.

- 4. Actual test conditions may vary from those designated but operation is guaranteed as specified.

- 5. Supply current for a given application can be accurately approximated by:

$\frac{NCV^2F}{4}$

where

N = total number of device outputs

C = capacitive load per output

V = supply voltage

F = clock frequency

- 6. Tested with all outputs changing every cycle and no load, at a 5 MHz clock rate.

- 7. Tested with all inputs within 0.1 V of **V**CC or Ground, no load.

- 8. These parameters are guaranteed but not 100% tested.

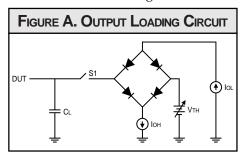

9. AC specifications are tested with input transition times less than 3 ns, output reference levels of 1.5 V (except tDIS test), and input levels of nominally 0 to 3.0 V. Output loading may be a resistive divider which provides for specified IOH and IOL at an output voltage of VOH min and VOL max respectively. Alternatively, a diode bridge with upper and lower current sources of IOH and IOL respectively, and a balancing voltage of 1.5 V may be used. Parasitic capacitance is 30 pF minimum, and may be distributed.

This device has high-speed outputs capable of large instantaneous current pulses and fast turn-on/turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

- a. A  $0.1~\mu F$  ceramic capacitor should be installed between VCC and Ground leads as close to the Device Under Test (DUT) as possible. Similar capacitors should be installed between device VCC and the tester common, and device ground and tester common.

- b. Ground and VCC supply planes must be brought directly to the DUT socket or contactor fingers.

- c. Input voltages should be adjusted to compensate for inductive ground and **V**CC noise to maintain required DUT input levels relative to the DUT ground pin.

- 10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

- 11. For the tena test, the transition is measured to the 1.5 V crossing point with datasheet loads. For the tDIS test, the transition is measured to the  $\pm 200 \,\mathrm{mV}$  level from the measured steady-state output voltage with  $\pm 10 \,\mathrm{mA}$  loads. The balancing voltage, VTH, is set at 3.5 V for Z-to-0 and 0-to-Z tests, and set at 0 V for Z-to-1 and 1-to-Z tests.

- 12. These parameters are only tested at the high temperature extreme, which is the worst case for leakage current.

### 16 x 16-bit Parallel Multiplier

6

# 16 x 16-bit Parallel Multiplier

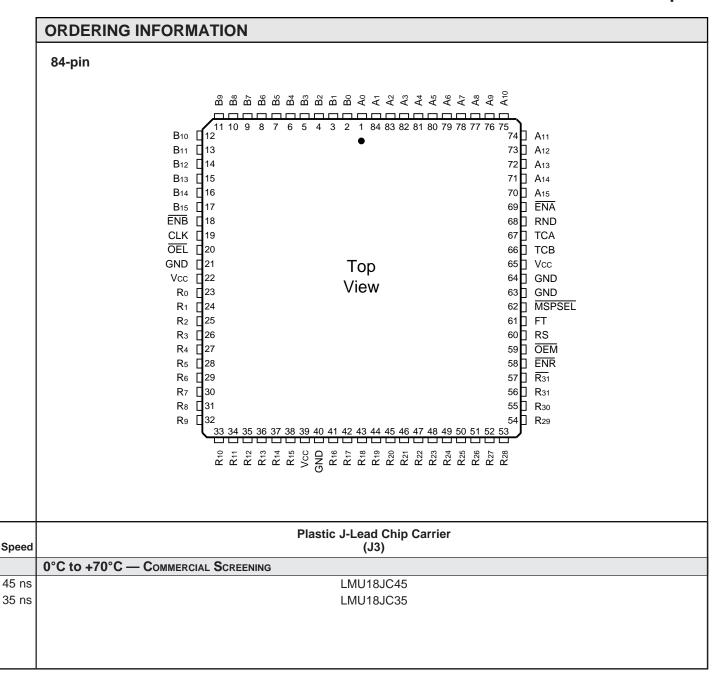

|     | ORDERING INFORMA          | TION            |                       |                           |                       |                      |              |                                             |           |                 |                 |               | ,,,,,        |      |             |       |

|-----|---------------------------|-----------------|-----------------------|---------------------------|-----------------------|----------------------|--------------|---------------------------------------------|-----------|-----------------|-----------------|---------------|--------------|------|-------------|-------|

|     | 84-pin                    |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     |                           | 1               | 2                     | 3                         | 4                     | 5                    | 6            | 7                                           | 8         | 9               | 10              | 11            |              |      |             |       |

|     |                           |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     | A                         | B <sub>9</sub>  | B <sub>7</sub>        | () B6 () B8               | )<br>B4<br>)<br>B5    | ()<br>B1<br>()<br>B2 | B3           | A2                                          | A5<br>A6  | A7<br>A9        | A8 () A10       | A11           |              |      |             |       |

|     | B<br>C                    | B12             | B <sub>10</sub>       | B8                        | B <sub>5</sub>        | B <sub>2</sub>       |              | $\bigcap_{A^2} \bigcap_{A^3} \bigcap_{A^4}$ | A6        | A9              | A10             | A13           |              |      |             |       |

|     | D                         | B <sub>13</sub> | ()<br>B <sub>11</sub> |                           |                       | Bo                   | Ao           | A4                                          |           |                 | A12             | A14           |              |      |             |       |

|     | E                         | B15             | B14                   | 0                         |                       |                      |              |                                             |           | (7)             | A15             | ENA           |              |      |             |       |

|     | F                         |                 | CLK ONB               | GND                       |                       |                      | Top Vie      |                                             |           | Vcc<br>()       | C TCA CND       | TCB           |              |      |             |       |

|     | G                         | R0              | ENB                   | $\bigcirc \circ \bigcirc$ | (i.                   | e., Com              | ponent S     | ide Pind                                    | out)      | GND<br>C)<br>RS | GND             | RND<br>MSPSEL |              |      |             |       |

|     | H                         | R <sub>1</sub>  | R <sub>2</sub>        | R3                        |                       |                      |              |                                             |           | RS              | FT<br>O         | MSPSEL<br>OEM |              |      |             |       |

|     | J                         |                 | ○ R2 ○ R5 ○ R8 ○ R10  |                           |                       | 0                    | ()<br>R18    | Q                                           |           |                 |                 | OEM<br>R31    |              |      |             |       |

|     | К                         | R6<br>C)<br>R7  | R8                    | ()<br>R11                 | ()<br>R14             | R <sub>17</sub>      | VCC          | R22<br>R21                                  | ()<br>R24 | ()<br>R27       | R30<br>C<br>R29 | R31<br>R31    |              |      |             |       |

|     | Ĺ                         | C<br>R9         | R10<br>R12            | R13                       | ()<br>R <sub>15</sub> | ()<br>R16            | ()<br>R19    | C)<br>R20                                   | R23       | R25             | R26             | C)<br>R28     |              |      |             |       |

|     |                           |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     |                           |                 |                       |                           | Disco                 | ntinu                | ed P         | ackaç                                       | je        |                 |                 |               |              |      |             |       |

| ed  |                           | (/////          | ////                  | (////                     | Ceran                 |                      | n Gri<br>33) | d Arra                                      | ay        |                 | <u>////</u>     | /////         | <br><u> </u> | //// | <u>////</u> | ///// |

| u   | 0°C to +70°C — COMMERCIAL | SCREEN          | NING                  |                           |                       | ,,                   | 33)          |                                             |           |                 |                 |               |              |      |             |       |

|     |                           |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     |                           |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     |                           |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     | -55°C to +125°C — Commer  | CIAL <b>S</b> C | REENII                | NG                        |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     |                           |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     |                           |                 |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

| - 1 |                           |                 | •                     |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     | _55°C to ±125°C MII -ST   | D-883 (         |                       |                           |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     | -55°C to +125°C — MIL-ST  | D-883 (         | COMPI                 | LIANI                     |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     | –55°C to +125°C — MIL-ST  | D-883 (         | COMP                  | LIANI                     |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

|     | –55°C to +125°C — MIL-ST  | D-883 (         | COMP                  | LIANI                     |                       |                      |              |                                             |           |                 |                 |               |              |      |             |       |

7