TOSHIBA TCD2557D

TOSHIBA CCD LINEAR IMAGE SENSOR CCD (Charge Coupled Device)

# TCD2557D

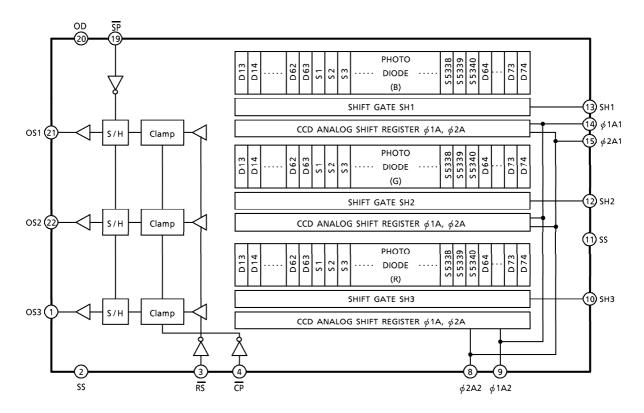

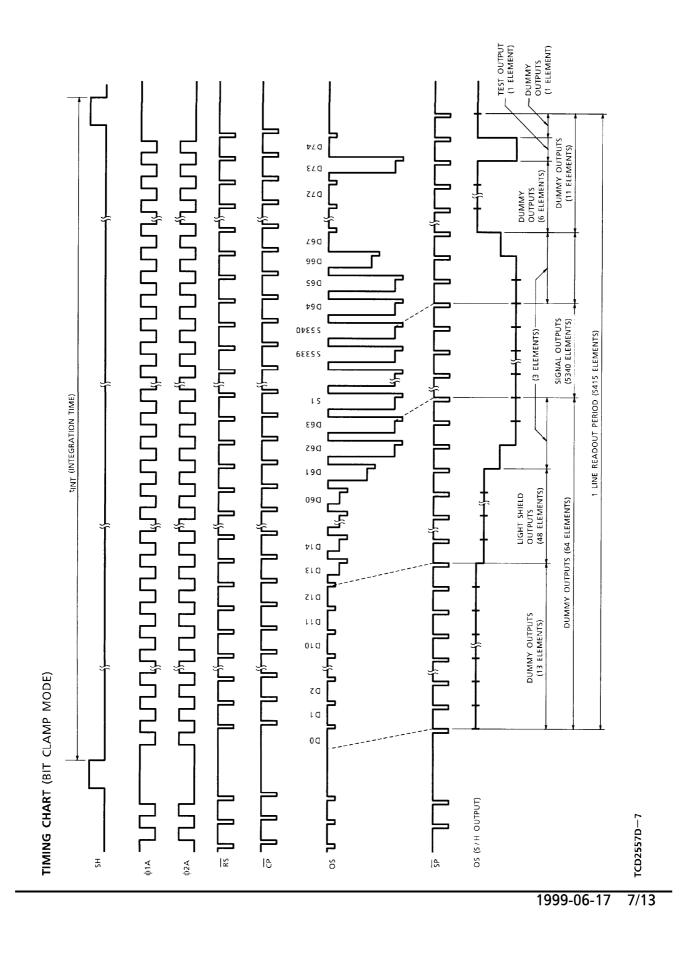

The TCD2557D is a high sensitive and low dark current 5340 elements x 3 line CCD color image sensor which includes CCD drive circuit, clamp circuit and sample and hold circuit

The sensor can be used for image scanner. The device contains a row of  $5340 \times 3$  photodioeds, which provide a 24 lines/mm (600DPI) across a A4 size paper. The divice is operated by 5 V (Pulse), and 12 V power supply.

#### **FEATURES**

Number of Image Sensing Elements

: 5340 elements x 3 line

• Image Sensing Element Size : 7  $\mu$ m by 7  $\mu$ m on 7  $\mu$ m centers

Photo Sensing Region : High sensitive and low dark

current PN photodiode

• Distance Between Photodiode Array : 28  $\mu$ m, 4 line

Clock : 2 phase (5 V)

Power Supply : 12 V Power supply voltage

Internal Circuit : Sample and Hold Circuit, Clamp Circuit

• Package : 22 pin CERDIP package

• Color Filter : Red, Green, Blue

### **MAXIMUM RATINGS** (Note 1)

|                         |                  |                | 1    |

|-------------------------|------------------|----------------|------|

| CHARACTERISTIC          | SYMBOL           | RATING         | UNIT |

| Clock Pulse Voltage     | Vφ               |                |      |

| Shift Pulse Voltage     | V <sub>SH</sub>  |                |      |

| Reset Pulse Voltage     | VRS              | -0.3~8         | V    |

| Clamp Pulse Voltage     | VCP              |                |      |

| Sample and Hold Voltage | VSP              |                |      |

| Power Supply            | V <sub>OD</sub>  | -0.3~15        | V    |

| Operating Temperature   | Topr             | 0~60           | °C   |

| Storage Temperature     | T <sub>stg</sub> | <b>- 25∼85</b> | °C   |

(Note 1) : All voltage are with respect to SS terminals (Ground).

Weight: 5.2 g (Typ.)

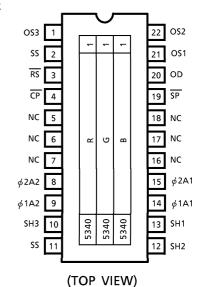

#### **PIN CONNECTIONS**

980910EBA1

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

TOSHIBA TCD2557D

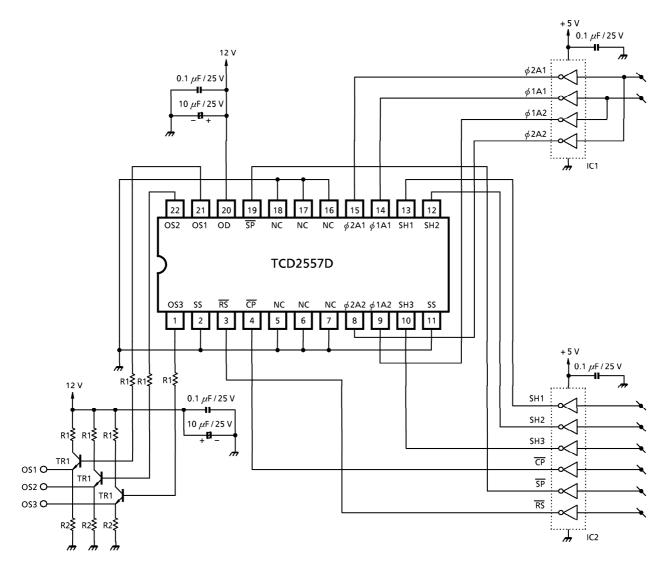

### **CIRCUIT DIAGRAM**

## **PIN NAMES**

| PIN No. | SYMBOL        | NAME                  | PIN No. | SYMBOL        | NAME                    |

|---------|---------------|-----------------------|---------|---------------|-------------------------|

| 1       | OS3           | Signal Output 3 (Red) | 12      | SH2           | Shift Gate 2            |

| 2       | SS            | Ground                | 13      | SH1           | Shift Gate 1            |

| 3       | RS            | Reset Gate            | 14      | φ1A1          | Clock 1 (Phase 1)       |

| 4       | CP            | Clamp Gate            | 15      | φ <b>2A</b> 1 | Clock 1 (Phase 2)       |

| 5       | NC            | Non Connection        | 16      | NC            | Non Connection          |

| 6       | NC            | Non Connection        | 17      | NC            | Non Connection          |

| 7       | NC            | Non Connection        | 18      | NC            | Non Connection          |

| 8       | φ2 <b>A</b> 2 | Clock 2 (Phase 2)     | 19      | SP            | Sample and Hold Gate    |

| 9       | φ1A2          | Clock 2 (Phase 1)     | 20      | OD            | Power                   |

| 10      | SH3           | Shift Gate 3          | 21      | OS1           | Signal Output 1 (Blue)  |

| 11      | SS            | Ground                | 22      | OS2           | Signal Output 2 (Green) |

### **OPTICAL / ELECTRICAL CHARACTERISTICS**

(Ta = 25°C,  $V_{OD}$  = 12 V,  $V_{\phi}$  =  $V_{\overline{SH}}$  =  $V_{\overline{RS}}$  =  $V_{\overline{CP}}$  = 5 V (PULSE),  $f_{\phi}$  = 1 MHz,  $f_{\overline{RS}}$  = 1 MHz,  $t_{INT}$  = 10 ms, LIGHT SOURCE = A LIGHT SOURCE + CM500S FILTER (t = 1 mm), LOAD RESISTANCE = 100 k $\Omega$ )

| CHARACTERISTIC                | SYMBOL           | MIN. | TYP. | MAX. | UNIT       | NOTE      |

|-------------------------------|------------------|------|------|------|------------|-----------|

|                               | R <sub>R</sub>   | 6.5  | 9.3  | 12.1 |            |           |

| Sensitivity                   | R <sub>G</sub>   | 6.9  | 9.9  | 12.9 | V / (lx·s) | (Note 2)  |

|                               | R <sub>B</sub>   | 3.8  | 5.4  | 7.0  |            |           |

| Photo Posnonso Non Uniformity | PRNU (1)         | _    | 10   | 20   | %          | (Note 3)  |

| Photo Response Non Uniformity | PRNU (3)         | _    | 3    | 12   | mV         | (Note 4)  |

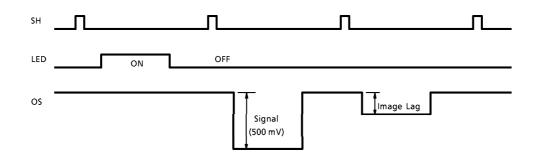

| Image Lag                     | IL               | _    | 1    | _    | %          | (Note 5)  |

| Saturation Output Voltage     | V <sub>SAT</sub> | 2.0  | 2.5  | _    | ٧          | (Note 6)  |

| Saturation Exposure           | SE               | _    | 0.23 | _    | lx∙s       | (Note 7)  |

| Dark Signal Voltage           | V <sub>DRK</sub> | _    | 0.5  | 2.0  | mV         | (Note 8)  |

| Dark Signal Non Uniformity    | DSNU             | _    | 2.0  | 5.0  | mV         | (Note 8)  |

| DC Power Dissipation          | PD               | _    | 300  | 400  | mW         |           |

| Total Transfer Efficiency     | TTE              | 92   | _    | _    | %          |           |

| Output Impedance              | ZO               | _    | 0.5  | 1.0  | kΩ         |           |

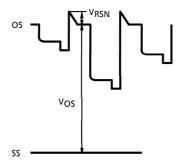

| DC Signal Output Voltage      | Vos              | 3.5  | 5.0  | 7.5  | V          | (Note 9)  |

| Random Noise                  | $N_{D}\sigma$    | _    | 0.8  | _    | mV         | (Note 10) |

| Reset Noise                   | V <sub>RSN</sub> | _    | 0.5  | 1.0  | V          | (Note 9)  |

- (Note 2) : Responsivity is defined for each color of signal outputs average when the photosensitive surface is applied with the light of uniform illumination and uniform color temperature.

- (Note 3) : PRNU (1) is defined for each color on a single chip by the expressions below when the photosensitive surface is applied with the light of uniform illumination and uniform color temperature.

PRNU (1) =

$$\frac{\Delta \chi}{\overline{\chi}}$$

× 100 (%)

When  $\overline{\chi}$  is average of total signal output and  $\Delta \chi$  is the maximum deviation from  $\overline{\chi}$ . The amount of incident light is shown below.

Red =

$$1/2 \cdot SE$$

Green =  $1/2 \cdot SE$

Bule =  $1/4 \cdot SE$

(Note 4) : PRNU (3) is defined as maximum voltage with next pixel, where measured 5% of SE (Typ.).

(Note 5) : Image Lag is defined as follows.

(Note 7) : Definition of SE

$$SE = \frac{V_{SAT}}{R_{G}} (Ix \cdot s)$$

(Note 8) : V<sub>DRK</sub> is defined as average dark signal voltage of all effective pixels.

DSNU is defined as different voltage between V<sub>DRK</sub> and V<sub>MDK</sub> when V<sub>MDK</sub> is maximum dark signal voltage.

(Note 9) : DC signal output voltage is defined as follows. Reset Noise Voltage is defined as follows.

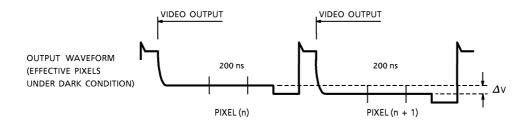

(Note 10): Random noise is defined as the standard deviation (sigma) of the output level difference between two adjacent effective pixels under no illumination (i.e. dark conditions) calculated by the following procedure.

- 1) Two adjacent pixels (pixel n and n + 1) in one reading are fixed as measurement points.

- 2) Each of the output level at video output periods averaged over 200ns period to get V (n) and V (n + 1).

- 3) V(n + 1) is subtracted from V(n) to get  $\Delta V$ .

$$\Delta V = V(n) - V(n + 1)$$

4) The standard deviation of  $\Delta V$  is calculated after procedure 2) and 3) are repeated 30 times (30 readings).

$$\overline{\Delta V} = \frac{1}{30} \sum_{\substack{i = 1 \ |\Delta Vi|}}^{30} |\Delta Vi| \quad \sigma = \sqrt{\frac{1}{30}} \sum_{\substack{i = 1 \ |\Delta Vi|}}^{30} (|\Delta Vi| - \overline{\Delta V})^2 \sigma$$

- 5) Procedure 2), 3) and 4) are repeated 10 times to get sigma value.

- 6) 10 sigma values are averaged.

$$\overline{\sigma} = \frac{1}{10} \sum_{i=1}^{10} \sigma_{i}$$

7)  $\overline{\sigma}$  value calculated using the above procedure is observed  $\sqrt{2}$  times larger than that measured relative to the ground level. So we specify random noise as follows.

ND

$$\sigma = \frac{1}{\sqrt{2}} \overline{\sigma}$$

## **OPERATING CONDITION**

| CHARACTERIST          | IC        | SYMBOL           | MIN.         | TYP.            | MAX.            | UNIT                                  | NOTE      |

|-----------------------|-----------|------------------|--------------|-----------------|-----------------|---------------------------------------|-----------|

| Clock Pulse Voltage   | "H" Level | \/ / A           | 4.5          | 5.0             | 5.5             | V                                     |           |

| Clock Pulse Voltage   | "L" Level | VφA              | 0.0          | _               | 0.3             | ]                                     |           |

| Chiff Dules Valtage   | "H" Level | \/               | VφA"H" - 0.5 | Vφ <b>Α"</b> H" | Vφ <b>Α</b> "H" | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | /Noto 11) |

| Shift Pulse Voltage   | "L" Level | VsH              | 0.0          | _               | 0.5             | V                                     | (Note 11) |

| Poset Bulse Veltage   | "H" Level | \/= <del>-</del> | 4.5          | 5.0             | 5.5             | V                                     |           |

| Reset Pulse Voltage   | "L" Level | VRS              | 0.0          | _               | 0.5             | <b>v</b>                              |           |

| Sample and Hold Pulse | "H" Level | \/ <del></del>   | 4.5          | 5.0             | 5.5             | V                                     | /Nata 12\ |

| Voltage               | "L" Level | VSP              | 0.0          | _               | 0.5             | ] V                                   | (Note 12) |

| Claman Dulas Valtage  | "H" Level | \/==             | 4.5          | 5.0             | 5.5             | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |           |

| Clamp Pulse Voltage   | "L" Level | VCP              | 0.0          | _               | 0.5             | V                                     |           |

| Power Supply Voltage  |           | V <sub>OD</sub>  | 11.4         | 12.0            | 13.0            | V                                     |           |

(Note 11) :  $V\phi A''H''$  means the high level voltage of  $V\phi A$  when SH pulse is high level. (Note 12) : Supply "L" Level to  $\overline{SP}$  terminal when sample and hold circuitry is not used.

## **CLOCK CHARACTERISTICS** (Ta = 25°C)

| CHARACTERISTIC                          | SYMBOL          | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------|-----------------|------|------|------|------|

| Clock Pulse Frequency                   | $f\phi$         | 0.3  | 1.0  | 6.0  | MHz  |

| Reset Pulse Frequency                   | fRS             | 0.3  | 1.0  | 6.0  | MHz  |

| Clamp Pulse Frequency (Bit clamp mode)  | fՇP             | 0.3  | 1.0  | 6.0  | MHz  |

| Clamp Pulse Frequency (Line clamp mode) | f <del>CP</del> | 10   | 100  | _    | Hz   |

| Sample and Hold Pulse Frequency         | f <u>⊽P</u>     | 0.3  | 1.0  | 6.0  | MHz  |

| Clock 1 Capacitance                     | C ∮ 1           | _    | 250  | 400  | pF   |

| Clock 2 Capacitance                     | C∳2             | _    | 230  | 400  | pF   |

| Shift Gate Capacitance                  | CSH             | _    | 20   | 100  | pF   |

| Reset Gate Capacitance                  | CRS             | _    | 10   | 30   | pF   |

| Sample and Hold Gate Capacitance        | CSP             | _    | 10   | 30   | pF   |

| Clamp Gate Capacitance                  | ССР             | _    | 10   | 30   | pF   |

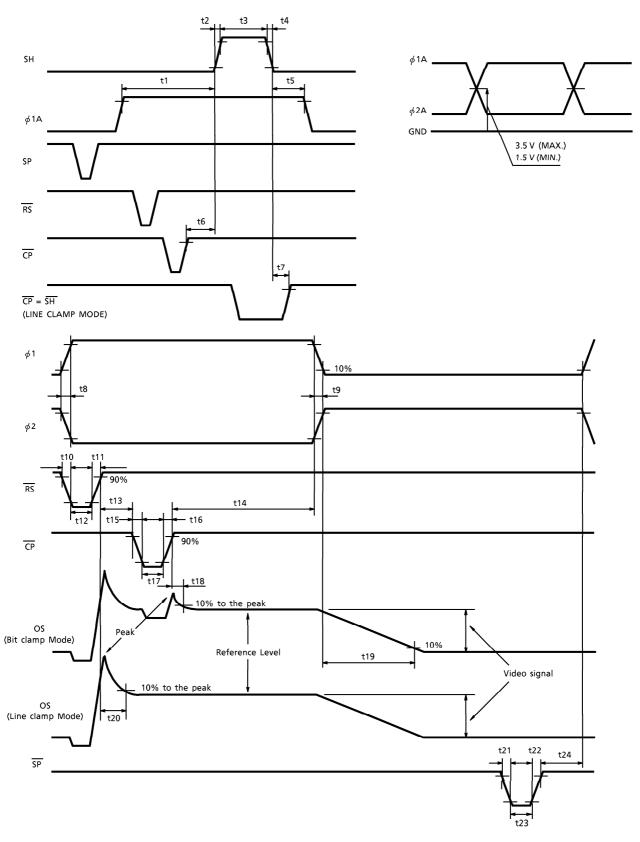

## TIMING REQUIREMENTS

## **TIMING REQUIREMENTS**

| CHARACTERISTIC                                               | SYMBOL   | MIN.      | TYP.<br>(Note 13) | MAX.         | UNIT |  |

|--------------------------------------------------------------|----------|-----------|-------------------|--------------|------|--|

| Pulse Timing of SH and $\phi$ 1                              | t1       | 120       | 1000              | _            | ns   |  |

|                                                              | t5       | 800       | 1000              | _            |      |  |

| SH Pulse Rise Time, Fall Time                                | t2, t4   | 0         | 50                | _            | ns   |  |

| SH Pulse Width                                               | t3       | 3000      | 5000              | _            | ns   |  |

| Pulse Timing of SH and CP                                    | t6       | 200       | 500               | _            | ns   |  |

| Pulse Timing of SH and $\overline{\sf CP}$ (Line clamp mode) | t7       | 10        | 100               | _            | ns   |  |

| $\phi$ 1, $\phi$ 2 Pulse Rise Time, Fall Time                | t8, t9   | 0         | 50                | _            | ns   |  |

| RS Pulse Rise Time, Fall Time                                | t10, t11 | 0         | 20                | _            | ns   |  |

| RS Pulse Width                                               | t12      | 30        | 80                | _            | ns   |  |

| Pulse Timing of RS and CP                                    | t13      | 10        | 20                | _            | ns   |  |

| Pulse Timing of $\phi$ 1A, $\phi$ 2A and $\overline{\sf CP}$ | t14      | 0         | 20                |              | ns   |  |

| CP Pulse Rise Time, Fall Time                                | t15, t16 | 0         | 20                | _            | ns   |  |

| CP Pulse Width (Note 14)                                     | t17      | 40 (3000) | 80 (5000)         | _            | ns   |  |

| Reference Level Settle Time (Bit clamp mode)                 | t18      | _         | 35                | 45 (Note 17) | ns   |  |

| Video Data Delay Time (Note 15)                              | t19      | _         | 40                | 60 (Note 16) | ns   |  |

| Reference Level Settle Time (Line clamp mode)                | t20      | _         | 60                | 70 (Note 17) | ns   |  |

| SP Pulse Rise Time, Fall Time                                | t21, t22 | 0         | 20                | _            | ns   |  |

| SP Pulse Width                                               | t23      | 45        | 100               | _            | ns   |  |

| Pulse Timing of $\phi A$ and $\overline{\sf SP}$             | t24      | 0         | 20                | _            | ns   |  |

(Note 13): TYP. is the case of  $f_{\overline{RS}} = 1.0 \text{ MHz}$ (Note 14): Line clamp Mode inside ( ). (Note 15): Load resistance is 100 kO

$\begin{array}{lll} \text{(Note 14)} & \text{Einc claims inside (7)} \\ \text{(Note 15)} & \text{Load resistance is } 100 \, \mathrm{k}\Omega \\ \text{(Note 16)} & \text{Typical settle time to about } 1\% \text{ of final value} \\ \text{(Note 17)} & \text{Typical settle time to about } 1\% \text{ of the peak} \\ \end{array}$

# APPLICATION NOTE MODE SELECT

| Sample and Hold | ON<br>CD Divisor | OFF                             |  |

|-----------------|------------------|---------------------------------|--|

| -               | SP Pulse         | SP = Low                        |  |

| Clamp Mode      | Bit Clamp        | Line Clamp                      |  |

| Clamp Mode      | CP Pulse         | $\overline{CP} = \overline{SH}$ |  |

## **TYPICAL DRIVE CIRCUIT**

$\begin{array}{lll} \text{IC1} & : \text{TC74AC04AP} \\ \text{IC2} & : \text{TC74HC04AP} \\ \text{TR1} & : \text{2SC1815-Y} \\ \text{R1} & : \text{150}\ \Omega \\ \text{R2} & : \text{1500}\ \Omega \\ \end{array}$

#### **CAUTION**

#### 1. Window Glass

The dust and stain on the glass window of the package degrade optical performance of CCD sensor.

Keep the glass window clean by saturating a cotton swab in alcohol and lightly wiping the surface, and allow the glass to dry, by blowing with filtered dry N<sub>2</sub>.

Care should be taken to avoid mechanical or thermal shock because the glass window is easily to damage.

#### 2. Electrostatic Breakdown

Store in shorting clip or in conductive foam to avoid electrostatic breakdown.

This device has some weakly terminals for static electricity. Therefor, please pay attention to treat this device.

CCD Image Sensor is protected against static electricity, but inferior puncture mode device due to static electricity is sometimes detected. In handing the device, it is necessary to execute the following static electricity preventive measures, in order to prevent the trouble rate increase of the manufacturing system due to static electricity.

- a. Prevent the generation of static electricity due to friction by making the work with bare hands or by putting on cotton gloves and non-charging working clothes.

- b. Discharge the static electricity by providing earth plate or earth wire on the floor, door or stand of the work room.

- c. Ground the tools such as soldering iron, radio cutting pliers of or pincer.

It is not necessarily required to execute all precaution items for static electricity.

It is all right to mitigate the precautions by confirming that the trouble rate within the prescribed range.

#### 3. Incident Light

CCD sensor is sensitive to infrared light.

Note that infrared light component degrades resolution and PRNU of CCD sensor.

#### 4. Lead Frame Forming

Since this package is not strong against mechanical stress, you should not reform the lead frame.

We recommend to use a IC-inserter when you assemble to PCB.

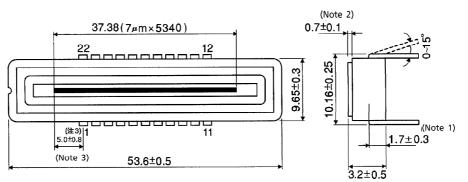

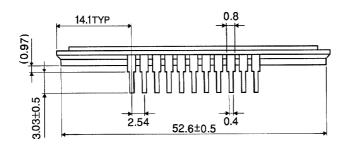

Unit: mm

## **OUTLINE DRAWING**

WDIP22-G-400-2.54D (A)

(Note 1): TOP OF CHIP TO BOTTOM OF PACKAGE.

(Note 2): GLASS THICKNESS (n = 1.5)

(Note 3): No.1 SENSOR ELEMENT (S1) TO EDGE OF No.1 PIN.

Weight: 5.2 g (Typ.)