# **MOTOROLA** ■ SEMICONDUCTOR ■ **TECHNICAL DATA**

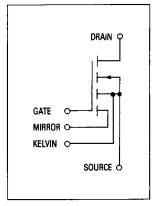

# **Power Field Effect Transistor N-Channel Enhancement-Mode** Silicon Gate with Current Sensing Capability

This TMOS Power FET with current sensing capability is designed for all power control applications where it is desirable to sense current such as in power supplies and motor controls. This device allows current sensing with a minimum of power loss.

- "Lossless" Current Sensing for Maximum Efficiency

- Sense Current is Reduced by a Factor of 900

- Ideal for Short Circuit/Overload Protection

- Simplifies Many Circuits When Used With Current Mode Integrated Circuits Such as the MC34129

- Kelvin Source Contact to Maximize Accuracy

- Rugged SOA is Power Dissipation Limited

- Low R<sub>DS(on)</sub> 0.065 Ohms Maximum

### NOTES:

- 1 Handling precautions to protect against electrostatic

- discharge is mandatory.

2. Do not use the mirror FET independent of the power FET

- 3. It is recommended that the mirror terminal (M) be shorted to the Kelvin Terminal (K) when current sensing is not

# MTP30N08M

TMOS SENSEFET DEVICE 30 AMPERES R<sub>DS(on)</sub> = 0.065 OHM 80 VOLTS

# MAXIMUM RATINGS (T<sub>C</sub> = 25°C unless otherwise noted)

| Rating                                                                           | Symbol               | Value        | Unit          |

|----------------------------------------------------------------------------------|----------------------|--------------|---------------|

| Drain-to-Source Voltage                                                          | V <sub>DSS</sub>     | 80           | Vdc           |

| Drain-to-Gate Voltage (RGS = 1 M $\Omega$ )                                      | VDGR                 | 80           | Vdc           |

| Gate-to-Source Voltage — Continuous<br>— Non-Repetitive (t <sub>p</sub> ≤ 50 μs) | V <sub>GS</sub>      | ± 20<br>± 40 | Vdc           |

| Drain-to-Mirror Voltage                                                          | VDMS                 | 80           | Vdc           |

| Gate-to-Mirror Voltage — Continuous<br>— Non-Repetitive (t <sub>p</sub> ≤ 50 μs) | V <sub>GM</sub>      | ± 20<br>± 40 | Vdc           |

| Drain Current — Continuous<br>— Pulsed                                           | I <sub>D</sub>       | 30<br>90     | Amps          |

| Sense Current — Continuous<br>— Pulsed                                           | I <sub>M</sub>       | 33<br>100    | mA            |

| Total Power Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C             | PD                   | 125<br>1     | Watts<br>W/°C |

| Operating and Storage Temperature Range                                          | Tن, T <sub>stg</sub> | -55 to 150   | °C            |

# THERMAL CHARACTERISTICS

| Thermal Resistance,                                                           |                                        |           | °C/W |

|-------------------------------------------------------------------------------|----------------------------------------|-----------|------|

| Junction-to-Case<br>Junction-to-Ambient                                       | R <sub>θ</sub> JC<br>R <sub>θ</sub> JA | 1<br>62.5 |      |

| Maximum Lead Temperature for Soldering Purposes, 1/8" from case for 5 seconds | TL                                     | 260       | °C   |

| Chara                                                                                                                               | cteristics                                                              | Symbol              | Min      | Тур          | Max          | Unit         |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|----------|--------------|--------------|--------------|

| OFF CHARACTERISTICS                                                                                                                 |                                                                         |                     |          |              | <u></u>      | <del>!</del> |

| Drain-to-Source Breakdown Voltage<br>(VGS = 0, I <sub>D</sub> = 0.25 mA)                                                            |                                                                         | V(BR)DSS            | 80       | _            | _            | Vdc          |

| Zero Gate Voltage Drain Current<br>{VDS = 80 V, VGS = 0}<br>{VDS = 80 V, VGS = 0, TJ = 125°C}                                       |                                                                         | IDSS                | <u>-</u> | _            | 10<br>100    | μAdc         |

| Gate-Body Leakage Current — Forward (VGSF = 20 Vdc, VDS = 0)                                                                        |                                                                         | IGSSF               | _        | _            | 100          | nAdc         |

| Gate-Body Leakage Current — Reverse<br>(VGSR = 20 Vdc, VDS = 0)                                                                     |                                                                         | IGSSR               | _        | _            | 100          | nAdc         |

| ON CHARACTERISTICS*                                                                                                                 |                                                                         |                     |          |              |              |              |

| Gate Threshold Voltage  (VDS = VGS, ID = 1 mAdc)  (TJ = 125°C)                                                                      |                                                                         | VGS(th)             | 2<br>1.5 | 2.5<br>—     | 4<br>3.5     | Vdc          |

| Static Drain-to-Source On-Resistance (VGS = 10 Vdc, ID = 15 Adc)                                                                    |                                                                         | R <sub>DS(on)</sub> |          | 0.05         | 0.065        | Ohms         |

| Drain-to-Source On-Voltage (V <sub>GS</sub> = 10 Vdc)<br>(I <sub>D</sub> = 30 A)<br>(I <sub>D</sub> = 15 A, T <sub>J</sub> = 125°C) |                                                                         | VDS(on)             | 1        | 1.5          | 1.95<br>1.95 | Vdc          |

| Forward Transconductance<br>(VDS = 15 Vdc, ID = 15 Adc)                                                                             |                                                                         | 9fs                 | 10       | _            | _            | mhos         |

| CURRENT SENSING CHARACT                                                                                                             | ERISTICS                                                                |                     |          |              |              |              |

| Current Mirror Ratio (Cell Ratio)<br>(RSENSE = 0, ID = 15 A, VGS = 10 V)                                                            |                                                                         | n                   | 900      | _            | 960          | _            |

| Mirror Compliance Ratio<br>(VGS = 10 Vdc, ID = 15 Adc)                                                                              |                                                                         | K <sub>mc</sub>     | _        | 0.65         |              | _            |

| Source Active Resistance<br>(VGS = 10 Vdc, I <sub>D</sub> = 15 Adc, R <sub>S</sub> = 10 megohm)                                     |                                                                         | ra(on)              |          | 26           | _            | mΩ           |

| Mirror Active Resistance<br>(VGS = 10 Vdc, ID = 15 Adc)                                                                             |                                                                         | rm(on)              | 1        | 24           | _            | Ohms         |

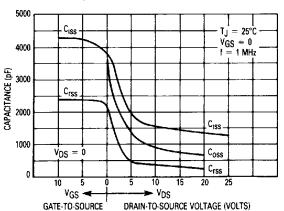

| DYNAMIC CHARACTERISTICS                                                                                                             |                                                                         | •                   |          |              |              |              |

| Input Capacitance                                                                                                                   |                                                                         | Ciss                | _        | _            | 1800         | pF           |

| Output Capacitance                                                                                                                  | V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0<br>f = 1 MHz                | Coss                | -        | _            | 900          |              |

| Transfer Capacitance                                                                                                                |                                                                         | C <sub>rss</sub>    | _        |              | 400          |              |

| WITCHING CHARACTERISTIC                                                                                                             | S*                                                                      |                     |          |              |              |              |

| Turn-On Delay Time                                                                                                                  |                                                                         | <sup>†</sup> d(on)  | _        | 25           | 60           | ns           |

| Rise Time                                                                                                                           | V <sub>DD</sub> = 30 V, I <sub>D</sub> = 15 A                           | tr                  | -        | 110          | 200          |              |

| Turn-Off Delay Time                                                                                                                 | R <sub>gen</sub> = 50 Ohms                                              | <sup>t</sup> d(off) |          | 120          | 200          |              |

| Fall Time                                                                                                                           |                                                                         | tf                  | _        | 65           | 150          |              |

| Total Gate Charge                                                                                                                   |                                                                         | Qg                  |          | 62           | 75           | nC           |

| Gate-Source Charge                                                                                                                  | V <sub>DS</sub> = 64 V, I <sub>D</sub> = 30 A<br>V <sub>GS</sub> = 10 V | Q <sub>gs</sub>     |          | 8            |              | ]            |

| Gate-Drain Charge                                                                                                                   | 30                                                                      | Q <sub>gd</sub>     | _        | 35           |              |              |

| SOURCE-DRAIN DIODE CHARA                                                                                                            | ACTERISTICS*                                                            |                     |          |              |              |              |

| Forward On-Voltage                                                                                                                  |                                                                         | V <sub>SD</sub>     | _        | 1.6          | 2            | Vdc          |

| Forward Turn-On Time                                                                                                                | IS = 30 A                                                               | ton                 | Limited  | by stray ind | uctance      | ns           |

| Reverse Recovery Time                                                                                                               | }                                                                       | t <sub>rr</sub>     | _        | 200          | _            | ]            |

<sup>\*</sup>Indicates Pulse Test Pulse Width = 300  $\mu$ s max, Duty Cycle = 2%.

3

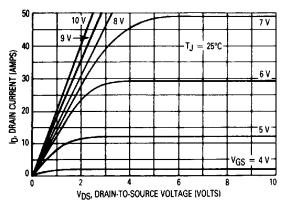

Figure 1. On-Region Characteristics

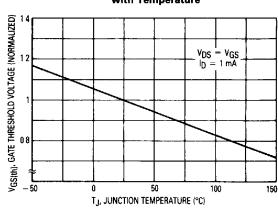

Figure 2. Gate Threshold Voltage Variation with Temperature

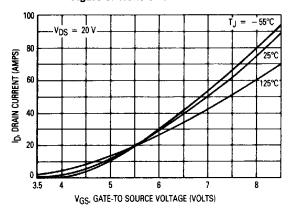

Figure 3. Transfer Characteristics

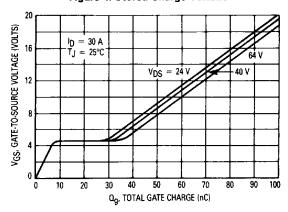

Figure 4. Stored Charge Variation

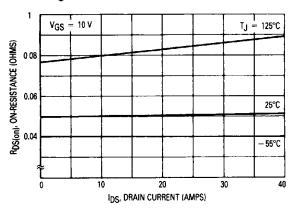

Figure 5. On-Resistance versus Drain Current

Figure 6. Capacitance Variation

# TYPICAL CHARACTERISTICS

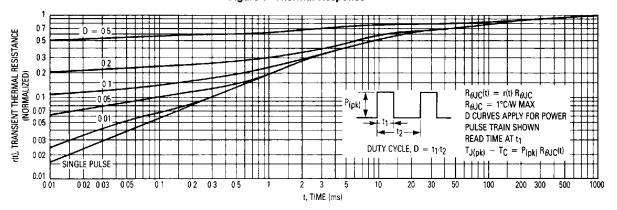

Figure 7. Thermal Response

# SAFE OPERATING AREA INFORMATION

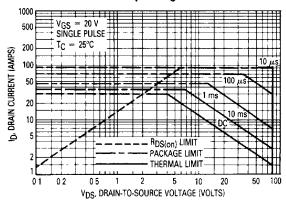

Figure 8. Maximum Rated Forward Biased Safe Operating Area

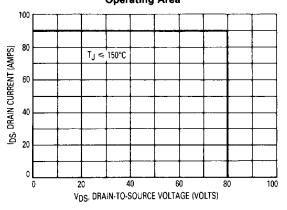

Figure 9. Maximum Rated Switching Safe **Operating Area**

#### FORWARD BIASED SAFE OPERATING AREA

The FBSOA curves define the maximum drain-tosource voltage and drain current that a device can safely handle when it is forward biased, or when it is on, or being turned on. Because these curves include the limitations of simultaneous high voltage and high current, up to the rating of the device, they are especially useful to designers of linear systems. The curves are based on a case temperature of 25°C and a maximum junction temperature of 150°C. Limitations for repetitive pulses at various case temperatures can be determined by using the thermal response curves. Motorola Application Note, AN569, "Transient Thermal Resistance-General Data and Its Use" provides detailed instructions.

# **SWITCHING SAFE OPERATING AREA**

The switching safe operating area (SOA) of Figure 9 is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current, IDM and the breakdown voltage, V(BR)DSS. The switching SOA shown in Figure 9 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

The power averaged over a complete switching cycle must be less than:

$$\frac{\mathsf{T}_{\mathsf{J}(\mathsf{max})} - \mathsf{T}_{\mathsf{C}}}{\mathsf{R}_{\theta}\mathsf{J}\mathsf{C}}$$

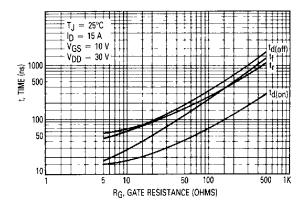

Figure 10. Resistive Switching Time Variation with Gate Resistance

3

# SAFE OPERATING AREA INFORMATION

P8E D MTP30N08M

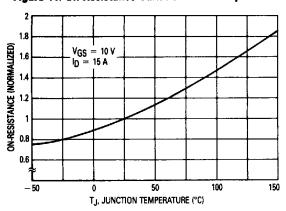

Figure 11. On-Resistance Variation with Temperature

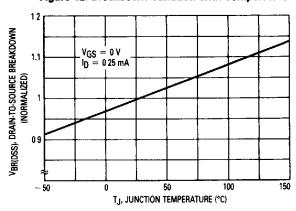

Figure 12. Breakdown Variation with Temperature

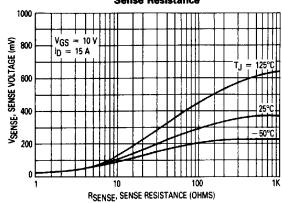

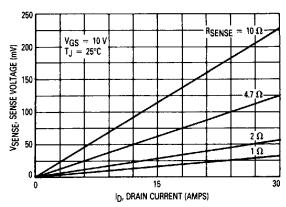

Figure 13. Sense Voltage Variation with Sense Resistance

Figure 14. Sense Voltage Variation with Drain Current

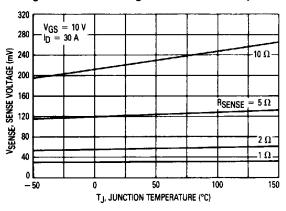

Figure 15. Sense Voltage Variation with Temperature

Figure 16. Sense Voltage Variation with Gate-to-Source Voltage

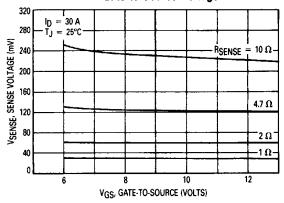

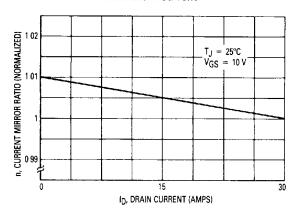

Figure 17. Current Mirror Ratio Variation with Drain Current

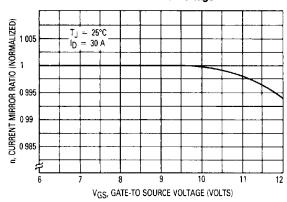

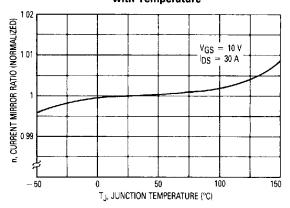

Figure 18. Current Mirror Ratio Variation with Gate-to-Source Voltage

Figure 19. Current Mirror Ratio Variation with Temperature

## LOSSLESS CURRENT SENSING

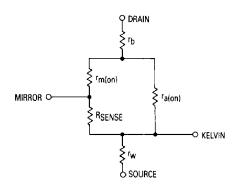

Assuming a fully switched on SENSEFET device, current sensing can be modeled with the simple resistor divider network shown in Figure 20. In this model, rb is the bulk drain resistance,  $r_{m(on)}$  is the active mirror onresistance, ra(on) is the power section's active onresistance and rw is the source wire bond resistance. Using values for  $r_{a(on)}$  and  $r_{m(on)}$  from the electrical characteristics table; VSENSE, RSENSE, and drain current may be calculated from the following sensing equations.

# SENSING EQUATIONS:

- 1. VSENSE = ID ra(on) RSENSE/[RSENSE + rm(on)]

- 2. RSENSE = VSENSE rm(on)/[ID ra(on) VSENSE]

3. ID = VSENSE (RSENSE + rm(on))/ra(on) RSENSE

4. n = ID/ISENSE; where RSENSE = 0

- 5.  $r_{a(on)} = r_{m(on)}/n$

When using these equations there are several factors to keep in mind.

They are described as follows:

- Maximum Sense Voltage: The maximum sense voltage that can appear at the mirror terminal is (ra(on)/ ra(on) + rb) x VDS(on). This ratio is called the mirror compliance ratio, KMC, and defines the upper boundary for sense voltage.

- Accuracy: Accurate current sensing is based upon the inherent matching of rm(on) with the power section's active on-resistance,  $r_{a(on)}$ . When RSENSE = 0, matching and current sensing accuracy are within ±3%. As RSENSE is increased, sensing accuracy is reduced since mirror current becomes dependent on the ratio of internal on-resistance to an external RSENSE. From a practical point of view, relatively good sensing accuracy (±10%) is maintained up to RSENSE = r<sub>m(on)</sub>/2. As R<sub>SENSE</sub> is increased beyond r<sub>m(on)</sub>, sensing accuracy decreases rapidly.

Figure 20. SENSEFET Model

- MTP30N08M

- Ground Loop Errors: Lossless current sensing is a technique that looks for 100 mV signals in a loop that may carry tens or even hundreds of amps. The potential for ground loop errors in this kind of an application is a first order design consideration. Internal wire bond resistance, contact resistance, and external wiring resistance are all significant. Therefore, it is important to reference sense voltage measurement circuitry to the Kelvin pin rather than power ground. In addition, referencing gate drive to the Kelvin pin rather than power ground will provide faster switching speeds.

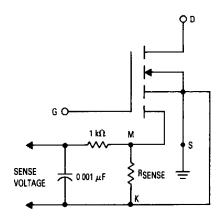

- Noise Suppression: Switching noise is also a first order design issue. Layout, therefore, is critical. In addition, a single pole RC filter between RSENSE and the current sensing circuitry's input terminals is often desirable. A 1  $\mu {

m sec}$  time constant is generally long enough to provide adequate noise suppression and short enough to provide adequate protection during overloads. An illustration is provided in Figure 21.

- Double Pulse Suppression: In PWM circuits it is critically important to include double pulse suppression in the control circuit topology. If the current limit loop is

- allowed to oscillate at its natural frequency, failure of the SENSEFET device is likely due to excessive power dissipation. By syncing current limiting to the clock with a latch, double pulse suppression architectures solve this problem, and provide effective protection from overload stress.

- Parasitic Diode: In addition to the power section's usual source-drain diode, there is a mirror-drain diode in the sense cells. Like the source-drain diode, the mirror-drain diode conducts during the reverse-mode operation, however, current sense characteristics are defined only in the forward-mode operation.

- Reverse Recovery: In bridge circuits, when a SENSE-FET device's source-drain diode is commutated a voltage spike is produced at the mirror. This spike is short since it lasts only for the drain-source diode's reverse recovery time. However, its amplitude can be an order of magnitude larger than normal sense voltages and produce unwanted overcurrent trips. Blanking, filtering, or other suppression techniques may be required in some applications.

Figure 21. SENSEFET Device with Noise Suppression