### PRELIMINARY

### GENERAL DESCRIPTION

JRC

The NJU6436 is a 1/4 duty LCD driver for segment type LCD panel with key scanning, Ir receiving and LED driving function.

The LCD driver consists of 4-common and 60-segment drives up to 240 segments and LED driver drives 1 LED which can use like as power on indicator.

The key scan function scanning up to 30 keys of the 6 x 5 matrix and the Ir receiving function recover the input wave shape. The key scanning data and Ir receiving data are transferred to the MPU serially.

The NJU6436 incorporate all of the function required front panel, therefore it is easy to apply car mounted audio, general audio and other products which have a display and key input on the front panel.

NJU6436F

#### FEATURES

- 60-Segment Drivers

- Duty Ratio 1/4 Duty ( Up to 240 Segments )

- 30 Key Scan Function (6 x 5 Matrix)

- Serial Data Transmission (Shift Clock 2MHz max.)

- Power-On Initialization

- Display Off Function (INH Terminal)

- LED Drive Function

- Ir Receiving Function

- Operating Voltage --- 5V±10%

- Package Outline --- QFP 100

- C-MOS Technology

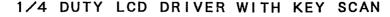

**BLOCK DIAGRAM**

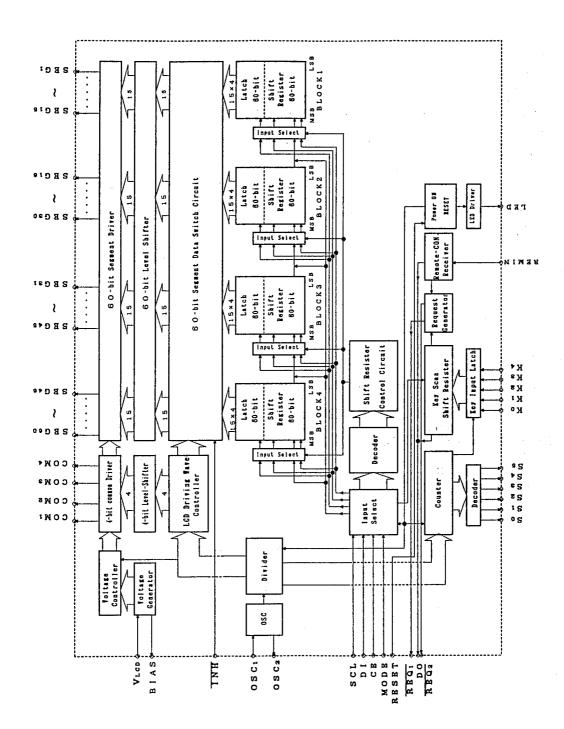

PIN CONFIGURATION

••

# TERMINAL DESCRIPTION

| NO.                | SYMBOL                | FUNCTION                                                                                                                                                                                     |

|--------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1~60               | $SEG_1 \sim SEG_{60}$ | LCD Segment Output Terminal                                                                                                                                                                  |

| 64~69              | $S_0 \sim S_5$        | Key Scanning Signal Output Terminal                                                                                                                                                          |

| 70~74              | K₀ ~ K₄               | Key Scanning Input Terminal (Built-in Pull-down Resistance)                                                                                                                                  |

| 77                 | REMIN                 | lr receiver input Terminal<br>Input the Ir receiver output.<br>This terminal must be "L" level when no use.                                                                                  |

| 78, 79             | $OSC_1$ , $OSC_2$     | CR Oscillating Terminal (External R Connecting)<br>For external clock operation, the clock should be input on<br>OSC1.                                                                       |

| 81                 | V <sub>DD</sub>       | Power Supply ( +5V )                                                                                                                                                                         |

| 91                 | Vss                   | Power Supply ( OV )                                                                                                                                                                          |

| 82                 | TNH                   | Display-Off Control Terminal<br>Display is turned off: Display data is retained in the<br>shift-register.                                                                                    |

|                    |                       | "H" : Display-On<br>"L" : Display-Off                                                                                                                                                        |

| 83                 | CE                    | Chip Enable Terminal<br>"H" : LCD display data Input , Mode setting code Input<br>"L" : Key data output mode<br>Fall Edge : LCD display data Latch , Mode setting code Latch                 |

| 84                 | SCL                   | Serial Data Transmission Clock Terminal<br>Shift clock used for transferring display data and mode set-<br>ting code to internal shift register, and used as Key data<br>output shift clock. |

| 85                 | DI                    | Serial Data Input Terminal<br>Data input timing : Rise edge of SCL clock                                                                                                                     |

| 86                 | DO                    | Serial Data Output Terminal<br>Key data and Ir input-data output.<br>Data output timing : Rise edge of SCL clock                                                                             |

| 87                 | MODE.                 | Select the Display Data or Mode Setting code Terminal<br>"H" : Mode setting code input<br>"L" : LCD Display data input                                                                       |

| 88                 | REQ1                  | Request Signal Output Terminal ( Key Data Read Request )                                                                                                                                     |

| 89                 | REQ2                  | Request Signal Output Terminal<br>( Ir Receiver Data Read Request )                                                                                                                          |

| 90                 | RESET                 | Reset Terminal (Built-in Pull-down Resistance)<br>"H" : Reset operation<br>(Shift-register all clear, key scan circuit initialize)<br>"L" or OPEN : Normal operation                         |

| 92                 | LED                   | LED Direct driving Terminal<br>Turns on during the NJU6436 is turned on except reset period<br>LED On : "L" output<br>LED Off : Hi-impedance                                                 |

| 93                 | VLCD                  | Power Supply for LCD Driving                                                                                                                                                                 |

| 94                 | BIAS                  | Adjusting Terminal for output current of Voltage Follower                                                                                                                                    |

| 97~100             | $COM_4 \sim COM_1$    | LCD Common Output Terminal                                                                                                                                                                   |

| 61~63,<br>75,76,80 | NC                    | Non Connection ( Normally open )                                                                                                                                                             |

-New Japan Radio Co.,Ltd.

### FUNCTIONAL DESCRIPTION

- (1) Operation of each block

- (1-1) Oscillation Circuit

Oscillation by connecting external resistance.

This circuits supply the basical clock signal to other circuits like as common and segment driver and key scan circuits.

(1-2) Divider Circuit

This circuit divide the oscillator frequency and generate the common and segment output timing signals.

- (1-3) Input Control Circuit This circuit select the LCD display data and mode setting code according to the condition of MODE terminal.

- (1-4) Shift-Register Circuit(60-bit) and Latch Circuit(60-bit)

When the CE terminal is "H" (Enable mode), the display data is transferred to the shift-register synchronized by the shift clock on the SCL terminal. The CE terminal signal latches the display data at the falling edge.

- (1-5) Segment Data switch Circuit and Segment Driver Set the segment display data according to the common timing and output through level shifter and output buffer.

- (1-6) Level Shifter Circuit Logic driving voltage is converted to LCD driving voltage.

- (1-7) LCD Common Driver Output the common driving signal for LCD.

- (1-8) LCD Bias Level Generator This circuit generate the LCD bias voltage.

- (1-9) Key Scan Counter This circuits generate key scanning timing. When the key input, the data in the counter is transferd to the key scan shift register.

- (1-10) Key Scan Decoder Decoding the counter output and generate the key scanning signal.

- (1-11) Key Input Latch Latch the key input data. This circuit detect two times same key input for a chatter free operation.

- (1-12) Key Scan Shift Register Output the data sent from counter and key input latch data to the MPU serially through the DO terminal.

- (1-13) Request Signal Generator Circuit

When detect some key input by the key scanning, this circuits output the "L" level signal to the controller as a "read out request signal"(REQ1).

The "L" level output of REQ1 is released when the key scan control code send the "End of read out".

When the data input from the REMIN, the "read out request signal" REQ2 is output "L" level as a "read out request signal" by synchronizing the rise edge of the input data.

It is also released when the mode setting code send the "End of read out".

- (1-14) LED Driving Circuit The LED connected between LED terminal and VDD terminal is turned on during the power turns on of the NJU6436 except reset period.

5

New Japan Radio Co.,Ltd.

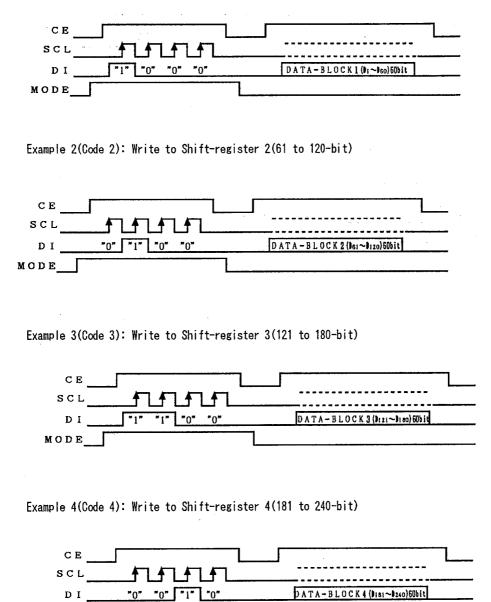

(2) Data Input Format

Two kind of data is input to the NJU6436.

① Mode Setting Data

② LCD Display Data

Normally, the shift register control code of mode setting and the display data are pare always. First, setting the transferred register by the shift register control code. Second, input the display data. Start the key scan, Stop the key scan and key data output are controlled by the key scan control code.

All of display data and mode setting data are input synchronized by the rise edge of the clock signal.

• Two kind of data is output from the NJU6436.

③ Key Data

④ Output signal of Ir Receiver

Key data outputs the key matrix scan data.

Key scan is stopped when power is supplied, reset signal is input to the reset terminal and software reset operation is executed. The key scan starts when the key input status change or "key scan start mode" of the key scan control code is input.

Key scan operation is stoped by either of the "key scan stop mode" of key scan control code, and reset signal inputs to the reset terminal.

After the key scan operation, the NJU6436 output the data read out request signal  $(\overline{REQ_1})$  to the controller.

Then the "key data output mode" of key scan control code is input to the NJU6436, the input key data is transferred to the transfer register and output to the data output terminal "DO" by synchronizing with rise edge of shift clock. (key data is 8 bit format.)

Key data read out signal( $\overline{REQ_1}$ ) is released by the "End of read out" of key scan control code input to the NJU6436.

Ir receiver output data input from the Ir receiver input terminal "REMIN" output to the data output terminal "DO" through internal buffer.

The NJU6436 output the read out request signal ( $\overline{REQ_2}$ ="L") by synchronize with the rise edge of the data. The read out request signal of ( $\overline{REQ_2}$ ) is released by the "End of read out" mode input same as key data read out.

(2-1)Input Data Correspond to Segment Status

| Data Dxxx | Segment Status |

|-----------|----------------|

| "H"       | ON             |

| "L"       | OFF            |

New Japan Radio Co., Ltd.

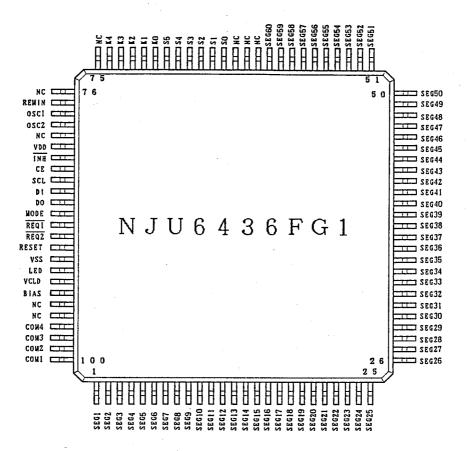

(2-2)Write to Shift-register Example

MODE [

Example 1(Code 1): Write to Shift-register 1(1 to 60-bit)

-New Japan Radio Co.,Ltd.

JRC

MODE\_\_\_\_

### (2-3)Mode Set Up

Data transferred shift register selection, key scan control and software reset are performed by writing the 4 bit data to the NJU6436 in CE="H" and MODE="H" state.

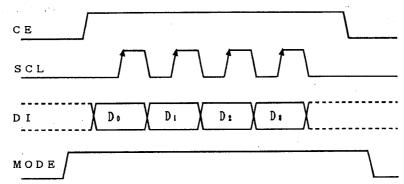

< Input Timing Chart >

< Mode Setting Table >

| CE    | MODE                                      | Mode sett | ing code        |                                                                                                                                                                    |

|-------|-------------------------------------------|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Term. | Term.                                     |           | D3~D0           | Mode Set Up                                                                                                                                                        |

|       |                                           |           | 0000 (0)        | End of Read out<br>( Key data and Ir receiver output data )<br>Release the read out request and start the<br>key scan.                                             |

|       |                                           | Shift-    | 0001 (1)        | Select the shift-register BLOCK1                                                                                                                                   |

|       |                                           |           | 0010 (2)        | Select the shift-register BLOCK2                                                                                                                                   |

|       |                                           | register  | 0011 (3)        | Select the shift-register BLOCK3                                                                                                                                   |

|       |                                           | control   | 0100 (4)        | Select the shift-register BLOCK4                                                                                                                                   |

|       |                                           | code      | 0101 (5)        | Select the all shift-register (BLOCK1~4)                                                                                                                           |

|       |                                           |           | 0110 (6)        | NO OPERATION                                                                                                                                                       |

|       | "H" "H"<br>Key<br>scan<br>control<br>code |           | 0111 (7)        | NO OPERATION                                                                                                                                                       |

| "H"   |                                           | "Н"       | 1000 (8)        | Key data output<br>Key data set into the transfer register and<br>prepare the key data transmit.                                                                   |

|       |                                           |           | 1001 (9)        | Key scan start<br>Key scan start from the halt state.                                                                                                              |

|       |                                           | control   | 1010 (A)        | Key scan stop and key data output<br>Newly key input data set into the transfer<br>register and stop the key scan.<br>Note;Read out request signal is not released |

|       |                                           |           | 1011 (B)        | Key scan initialize<br>Stop the key scan and release the read out<br>request signal.                                                                               |

|       |                                           |           | 1100 (C)        | NO OPERATION                                                                                                                                                       |

|       |                                           |           | <u>1101 (D)</u> | NO OPERATION                                                                                                                                                       |

|       |                                           |           | 1110 (E)        | NO OPERATION                                                                                                                                                       |

|       |                                           | :<br>:    | 1111 (F)        | Software reset<br>• Shift-register all clear (data="0")<br>• Key scan initialize                                                                                   |

Note) The decoder is 4 bit format data through type. Though 8 bit data is also available to input at the mode setting, in that time front 4 bit is valid from the fall edge of CE signal.

-New Japan Radio Co.,Ltd.

- (2-4)Block Data and Whole Data transfer

- a. Block Data(60-bit) transfer

Each 60 bits data transfer to each shift register block 1 to 4 respectively. When the input data is over than 60 bit, front 60 bit from fall edge of "CE" signal is valid. In case of the input data is less than 60 bit, the previous data is remaining on the register. So that 60 or over than 60 bit data input must be required.

|                         | Data Block 1 : from SEG1, COM1 to SEG1s, COM4                                                                                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| CE                      |                                                                                                                                   |

| SCL                     |                                                                                                                                   |

| DI                      | D1 D2 D3 D4 D5 D8 D7 D8 D55 D56 D57 D58 D59 D80                                                                                   |

| MODE                    | "L" LEVEL                                                                                                                         |

|                         | Data Block 2 : from SEG16, COM1 to SEG30, COM4                                                                                    |

| CE                      |                                                                                                                                   |

| SCL                     |                                                                                                                                   |

| DI                      | Ds1 Ds2 Ds3 D64 D65 D66 D67 D68 D115 D116 D117 D118 D119 D120                                                                     |

| MODE                    | "L" LEVEL                                                                                                                         |

|                         |                                                                                                                                   |

|                         | Data Block 3 : from SEG₃, COM, to SEG₄₅, COM₄                                                                                     |

| CE                      | Data Block 3 : from SEG31, COM1 to SEG45, COM4                                                                                    |

| CE .<br>SCL .           |                                                                                                                                   |

|                         |                                                                                                                                   |

| SCL .<br>Di .           |                                                                                                                                   |

| SCL .<br>Di .           | D121 D122 D123 D124 D125 D126 D127 D128 D175 D176 D177 D178 D179 D180<br>"L" LEVEL                                                |

| SCL<br>Di<br>Mode       | D121 D122 D123 D124 D125 D126 D127 D126 D175 D176 D177 D176 D179 D160<br>"L" LEVEL Data Block 4 : from SEG46, COM1 to SEG60, COM4 |

| SCL .<br>Di .           | D121 D122 D123 D124 D125 D126 D127 D126 D175 D176 D177 D176 D179 D160<br>"L" LEVEL Data Block 4 : from SEG46, COM1 to SEG60, COM4 |

| SCL<br>Di<br>Mode       | D121 D122 D123 D124 D125 D126 D127 D126 D175 D176 D177 D176 D179 D160<br>"L" LEVEL Data Block 4 : from SEG46, COM1 to SEG60, COM4 |

| SCL<br>DI<br>Mode<br>Ce | D121 D122 D123 D124 D125 D126 D127 D126 D175 D176 D177 D176 D179 D160<br>"L" LEVEL Data Block 4 : from SEG46, COM1 to SEG60, COM4 |

b. Whole Data(240-bit) transfer

Whole 240 bits data transfer to the shift register block 1 to 4 once a time. When the input data is over than 240 bit, front 240 bit from fall edge of "CE" signal is valid. In case of the input data is less than 240 bit, the previous data is remaining on the register.

So that 240 or over than 240 bit data input must be required.

|       | from sł | nift-re | egister | • 1 to | shift- | regist | er 4 |    |            |        |      |      |        |      |      |    |

|-------|---------|---------|---------|--------|--------|--------|------|----|------------|--------|------|------|--------|------|------|----|

| CE    |         |         |         |        |        |        |      |    |            |        |      |      |        |      |      | ٦_ |

| SCL _ |         |         |         |        |        |        |      |    | ] <u>.</u> |        |      |      |        |      |      |    |

| DI _  | Dı      | D2      | D3      | D4     | D5     | De     | D7   | Da | I          | D2 3 5 | D236 | D237 | D2 3 8 | D239 | D240 |    |

| MODE  | "L" LE  | EVEL    |         |        |        |        |      |    |            |        |      |      |        |      |      |    |

(2-5) Display Data Correspond to Segment and Common Terminals

| Mode   | Data                                     | Segment | COM1 | COM2 | COM₃ | COM₄ | Data Block   |

|--------|------------------------------------------|---------|------|------|------|------|--------------|

| Mode 1 | D1<br>D2<br>D3<br>D4                     | SEG1    | 0    | 0    | 0    | 0    | Data Block 1 |

|        |                                          |         |      | •    |      |      |              |

|        | D 5 7<br>D 5 8<br>D 5 9<br>D 6 0         | SEG1 5  | 0    | 0    | 0    | 0    |              |

| Mode 2 | D 6 1<br>D 6 2<br>D 6 3<br>D 6 4         | SEG1 6  | 0    | 0    | 0    | 0    | Data Block 2 |

|        |                                          |         |      |      | :    |      |              |

|        | D117<br>D118<br>D119<br>D120             | SEG₃o   | 0    | 0    | 0    | 0    |              |

| Mode 3 | D121<br>D122<br>D123<br>D124             | SEG₃ı   | 0    | 0    | ο    | 0    | Data Block 3 |

|        | :                                        |         | •    |      | :    |      |              |

|        | D177<br>D178<br>D179<br>D180             | SEG4 5  | 0    | 0    | 0    | 0    |              |

| Mode 4 | D 1 8 1<br>D 1 8 2<br>D 1 8 3<br>D 1 8 4 | SEG4 8  | 0    | 0    | 0    | 0    | Data Block 4 |

|        | :                                        | :       |      | :    |      | :    |              |

|        | D 2 3 7<br>D 2 3 8<br>D 2 3 9<br>D 2 4 0 | SEGeo   | 0    | 0    | 0    | 0    |              |

# -New Japan Radio Co.,Ltd.

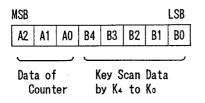

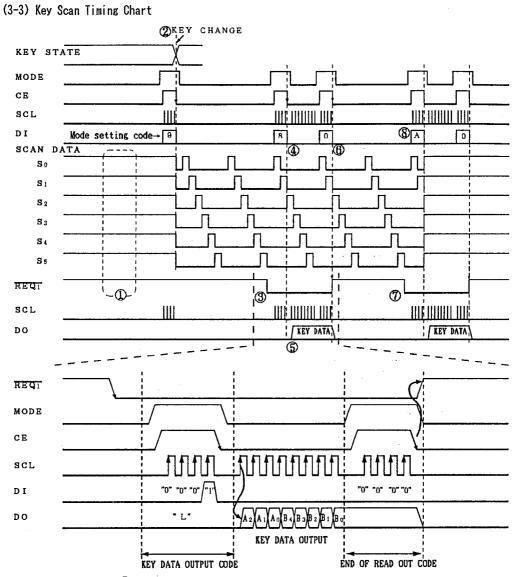

- (3) Key Input Data Output Format

- (3-1) Data Format

**※** B4∼B0 = K₄∼K₀ Terminals

Key Scan Signal Correspond to Counter Data is as follows:

| т.,                   |            |               | v 0   |          | 0:            | - 1       |        |   | C                | ounter Da   | ta          |

|-----------------------|------------|---------------|-------|----------|---------------|-----------|--------|---|------------------|-------------|-------------|

| Terminal              |            |               | Key S | can      | Sign          | aı        |        | • | A2               | A1          | AO          |

| S٥                    |            |               |       |          |               | $\square$ |        |   | 0                | 0           | 0           |

| Sı                    |            |               |       |          |               | -         |        |   | 0                | 0           | 1           |

| S₂                    |            |               |       |          |               |           |        |   | 0                | 1           | 0           |

| S3                    |            |               | _     |          |               |           |        |   | 0                | 1           | 1           |

| S₄                    |            |               |       |          |               | _         |        |   | 1                | 0           | 0           |

| S₅                    |            |               |       | <u> </u> |               |           |        |   | 1                | 0           | 1           |

|                       |            |               |       |          |               |           |        |   | Divide           | Cycle       | Frequency   |

| Search<br>Pulse Width | _ <b>→</b> | +1            | 024/f | osc      | <b>≒</b> 7.8  | 8mSe      | C      |   | 1<br>1024        | 7.88mS      |             |

| Key Scan<br>One cycle |            | 6144/<br>≒47. |       |          |               |           |        |   | <u>1</u><br>6144 | 47.26<br>mS | 21.15<br>Hz |

| Key Read<br>MIN. Time | <b>~</b>   | 1             | 2288/ | fos      | c <b>≒</b> 94 | .52n      | 1Sec · | ; | 1<br>12288       | 94.52<br>mS | 10.58<br>Hz |

(fosc=130kHz)

Less than 47.26mSec key input is neglected due to the two times key input for the chatter free operation.

The 5 bit data of B4 to B0 correspond to the key input terminal K4 to K0, when some key is pressed the data "1" correspond to the key input line, input to the register. The data of A2 to A0 and B4 to B0 indicate the key data input.

5

# -New Japan Radio Co.,Ltd.=

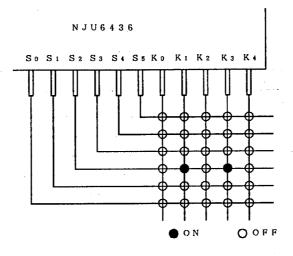

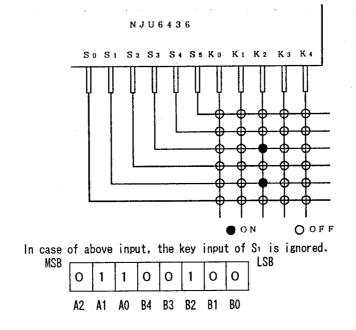

### (3-2) Key Roll Over Input.

•When the roll over input occur, following data are input. < Roll over on same Sx line >

When two key connected K1 and K3 pressed at once the data "1" input to the B3 and B1.

| NOB | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | LJ |

|-----|----|----|----|----|----|----|----|----|----|

|     | A2 | A1 | AO | B4 | B3 | B2 | B1 | BO |    |

• Permit the following roll over.

< Roll over on same Kx line >

In this case, there are following priority.

S5>S4>S3>S2>S1>S0

If this kind of roll over occur, the low priority input is ignore.

-New Japan Radio Co., Ltd.

[ Operation Explanation ]

- ① Before key scanning, all of Sx terminal output the "H" to detect the some key input.

- ② Key scan operation start when recognize the key input or setting the key scan. Note) The key input is detected by Kx input level, so the change of key input of same Kx line roll over can not recognize.

- roll over can not recognize.

When key input, the NJU6436 output the read out request signal to the controller (REQ1="L"). In this time, the "DO" output change to the key data output terminal.

- ④ When key data output is setting by the mode selection, the input key data transferred to the transfer register.

- (5) Key data of 8 bit output by synchronize with the rise edge of clock signal after the mode setting.

- 6~7 Select the end of read out by the mode setting, the key scan register reset then start the key scan again.

- Wey scan stop and key data output" or "key scan initialize" key scan stop is selected by the key scan control code input. In this time, the key scan is stopped and all of S₀ to S₅ put on "H".

5

-New Japan Radio Co.,Ltd.

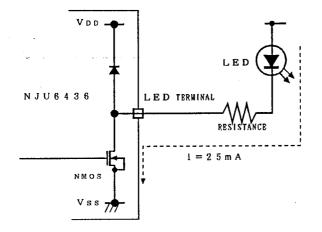

(4) LED Driving Circuit

Connecting the LED between LED terminal and Vop terminal, the LED turns on during the power of NJU6436 turns on except reset period.

Operating voltage current can adjust by insert the protection resistor between LED and LED terminal.

- Note) Protection resistor must be connect to the LED to avoid over than the maximum ratings of voltage and current between Anode and Cathode of the LED. No protection resistor may occur the damage of LED output buffer and LED.

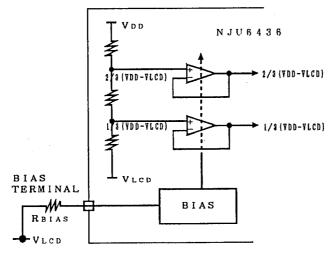

- (5) LCD Driving Voltage / Bias current Adjustment Terminal

Power block is consist of 3 blocks of bias, bleeder and buffer amplifire as show above.

The output current of buffer amplifire can adjust by changing the current flow on bias circuit which controlled by external resistance connected to the BIAS terminal.

New Japan Radio Co., Ltd.

NJU6436

## MABSOLUTE MAXIMUM RATINGS

(Vss=0V,Ta=25℃)

-

| PARAMETER             | SYMBOL  | RATINGS                        | UNIT |

|-----------------------|---------|--------------------------------|------|

| Operating Voltage (1) | Vdd     | - 0.3 ~ + 7.0                  | V    |

| Operating Voltage (2) | VLCD    | $V_{DD}$ -13.5 ~ $V_{DD}$ +0.3 | ٧    |

| Input Voltage         | VIN (1) | $-0.3 \sim V_{DD}+0.3$         | ٧    |

| Operating Temperature | Topr    | - 30 ~ + 85                    | Ĵ    |

| Storage Temperature   | Tstg    | - 40 ~ + 125                   | Ĵ    |

-New Japan Radio Co.,Ltd.-

Note 1) All Input Terminals

### ELECTRICAL CHARACTERISTICS DC Characteristics

$(Ta=25^{\circ}C, V_{DD}=5.0V, V_{ss}=0V, V_{DD}\sim V_{LCD}=13.5V)$

| • DC Characteristics            |                 |                                                                                       |                                                 | C,VDD=0.0                    |                                                 |                                         |      |

|---------------------------------|-----------------|---------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------|-------------------------------------------------|-----------------------------------------|------|

| PARAMETER                       | SYMBOL          | CONDI                                                                                 | TIONS                                           | MIN                          | TYP                                             | MAX                                     | UNIT |

| Operating Voltage               | VDD             | V <sub>DD</sub> Terminal                                                              |                                                 | 4.5                          | 5.0                                             | 5.5                                     | V    |

| LCD driving Voltage             | VLCD            | VLCD Terminal                                                                         |                                                 | VDD-13.5                     |                                                 | Vss                                     | V    |

| "H" Input Voltage               | VIH             | RESET,SCL,DI,<br>TNH,K₀~K₄,MO                                                         | DE Terminals                                    | 0.8Vpd                       |                                                 | VDD                                     | ٧    |

| "L" Input Voltage               | VIL             | RESET, SCL, D1, 1<br>INH, Ko~K4, MO                                                   |                                                 | Vss                          | .75                                             | 0.2V <sub>DD</sub>                      | V    |

| "H".Input Current               | Ін              | SCL,D1,CE,REM                                                                         | Terminals                                       |                              |                                                 | 5                                       | μA   |

| "L" Input Current               | 111             | RESET,SCL,DI,<br>INH,Ko∼K₄,MO<br>VI=V⊴s                                               | -                                               |                              |                                                 | 5                                       | μA   |

| "H" Output Voltage (1)          | Vон (1)         | I <sub>он</sub> =−10µА<br>SEG1~SEGбо Т                                                | erminals                                        | VDD-1.0                      |                                                 |                                         | ۷    |

| "H" Output Voltage (2)          | <b>V</b> он (2) | l <sub>он</sub> =-100µА<br><u>COM₁~COM₄ Te</u>                                        | rminals                                         | VDD-0.6                      |                                                 |                                         | ۷    |

| "H" Output Voltage (3)          | <b>V</b> он (з) | $I_{OH} = -40 \mu A$<br>$S_0 \sim S_5, DO, \overline{R}$                              | EQ <sub>1</sub> , REQ <sub>2</sub><br>Terminals | VDD-0.8                      |                                                 |                                         | V    |

| "L" Output Voltage (1)          | Vol (1)         | Iol=10µA<br>SEG1∼SEG60 T                                                              | erminals                                        |                              |                                                 | V <sub>LCD</sub> +1.0                   | ۷    |

| "L" Output Voltage (2)          | Vol (2)         | lo⊥=100µA<br>COM₁~COM₄ Te                                                             | rminals                                         |                              |                                                 | V <sub>LCD</sub> +0.6                   | ۷    |

| "L" Output Voltage (3)          | <b>V</b> ol (3) | $   I_{ol}=400 \mu \text{A} \\   S_{o}\sim S_{5}, DO, \overline{R} $                  | EQ <sub>1</sub> , <u>REQ</u> 2<br>Terminals     |                              |                                                 | 0.8                                     | ۷    |

| "L" Output Voltage (4)          | Vol (4)         | lo⊥=25mA<br>LED Terminal                                                              |                                                 |                              |                                                 | 1.5                                     | ۷    |

| COM 1/3 Level Voltage           | VMC1/3          | l₀=±5µA<br>COMı~COM₄ Te                                                               | rminals                                         | 1 · (Vpp-<br>Vbcp)73<br>-0.6 | 1.(VDD<br>-VLCD)<br>/3                          | 1. (Vpp-<br>Vbcp)73<br>+0.6             | ۷    |

| COM 2/3 Level Voltage           | VMC2/3          | l₀=±5µA<br>COMı~COM₄ Te                                                               | rminals                                         | ₹.(V<br>5.6)73               | 2.(V <sub>DD</sub><br>7)<br>73                  | 2. (Vp. 9-5<br>Vbc.B) 73<br>+0.6        | ۷    |

| SEG 1/3 Level Voltage           | <b>V</b> мs 1/3 | lo=±5µA<br>SEG1~SEG60 T                                                               | erminals                                        | 1.(Vpp-<br>Vpcp)73<br>-1.0   | 1.(V <sub>DD</sub><br>-V <sub>LCD</sub> )<br>/3 | 1·(Vpp-<br>V <sub>t</sub> cp)73<br>+1.0 | ۷    |

| SEG 2/3 Level Voltage           | VM52/3          | I₀=±5µA<br>SEG1~SEG60 T                                                               | erminals                                        | 2. (Vp 73<br>V cp 73         | 2.(VDD<br>-VLCD)<br>/3                          | 2. (Vp 73<br>V cp)73<br>+1.0            | ۷    |

| Oscillation Frequency           | forc            | OSC1,OSC2                                                                             | R=1MΩ                                           | 15                           | 20                                              | 25                                      | kHz  |

|                                 |                 | Terminals                                                                             | R=140KΩ                                         | 110                          | 130                                             | 150                                     | kHZ  |

|                                 |                 |                                                                                       | R=51KΩ                                          | 200                          | 300                                             | 400                                     | kHz  |

| Operating Current (1)           | <b> </b> 55     | Vss Terminal<br>Except LCD ou<br>fosc=130kHz,<br>RESET,LED,Kor<br>Te<br>Key-Scan No-0 | tput<br>CL=50PF<br>~K4<br>rminals Open          |                              | 50                                              | 100                                     | μA   |

| Operating Current (2)           | LCD             | V <sub>LCD</sub> Terminal<br>LCD output no<br>fosc=130kHz<br>RESET,LED,BIA            | -load                                           |                              | 50                                              | 100                                     | μA   |

| Pull-Down Resistance<br>Current | P               | Ko~K₄,RESET<br>Vın=Vdd                                                                | Terminals                                       |                              | 10                                              | 20                                      | μA   |

-New Japan Radio Co.,Ltd.

NJU6436

| J | R | C |

|---|---|---|

|   | 1 |   |

| AC Characteristics                                        |                     | (Ta=25°C                                                                                                | C,Voo=5.0V, | Vss=OV |     | 5 <b>=13.5V</b> ) |

|-----------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|-------------|--------|-----|-------------------|

| PARAMETER                                                 | SYMBOL              | CONDITIONS                                                                                              | MIN         | TYP    | MAX | UNIT              |

| "L" Clock Pulse Width                                     | twell               | SCL Terminal                                                                                            | 200         |        |     | ns                |

| "H" Clock Pulse Width                                     | twclh               | SCL Terminal                                                                                            | 200         |        |     | กร                |

| Data Set-up Time                                          | tos                 | SCL,DI Terminals                                                                                        | 200         |        |     | ns                |

| Data Hold Time                                            | t <sub>DB</sub>     | SCL,DI Terminals                                                                                        | 200         |        |     | ns                |

| CE→SCL Set-up Time                                        | taci                | SCL,CE Terminals                                                                                        | 200         |        |     | ns                |

| SCL→CE Hold Time                                          | thCLE               | SCL,CE Terminals                                                                                        | 200         |        |     | ns                |

| MODE→CE Set-up Time                                       | t <sub>aMD</sub>    | CE, MODE Terminals                                                                                      | 200         |        |     | ns                |

| CE→MODE Hold Time                                         | thmd                | CE, MODE Terminals                                                                                      | 200         |        |     | ns                |

| CE "L" Pulse Width                                        | twcel               | CE Terminal                                                                                             | 200         |        |     | ns                |

| REQ₁→CE Set-up Time                                       | t <sub>ace</sub>    | REQ1,CE Terminals                                                                                       | 200         |        |     | ns                |

| CE→SCL Set-up Time                                        | t#SF                | CE,SCL Terminals                                                                                        | 200         |        |     | ns                |

| Data Output Delay Time<br>(1)                             | takd                | SCL,DO Terminals<br>DO Load = 50PF                                                                      |             |        | 120 | ns                |

| CE <del>→REQ<sub>1</sub>,REQ<sub>2</sub></del> Delay Time | tadrq               | $\frac{CE, \overline{REQ_1}, \overline{REQ_2}}{\overline{REQ_1}, \overline{REQ_2}} \text{ Load = 50PF}$ |             |        | 120 | ns                |

| REMIN "L" Pulse Width                                     | t <sub>wR EML</sub> | REMIN Terminal                                                                                          | 200         |        |     | ns                |

| REMIN "H" Pulse Width                                     | t <sub>wR EMH</sub> | REMIN Terminal                                                                                          | 200         |        |     | ns                |

| Data Output Delay Time<br>(2)                             | t <sub>dREM</sub>   | REMIN,DO Terminals<br>DO Load = 50PF                                                                    |             |        | 120 | ns                |

| REMIN→REQ₂ Delay Time                                     | tarmrq              | REMIN, REQ2 Terminals<br>DO Load = 50PF                                                                 |             |        | 120 | ns                |

AC Characteristics

$(T_a=25^{\circ}C, V_{DD}=5.0V, V_{SS}=0V, V_{DD}\sim V_{LCD}=13.5V)$

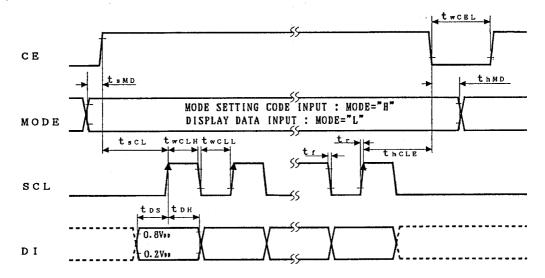

• Display Data Input / Mode Setting code input Timing Characteristics

# -New Japan Radio Co., Ltd.<sup>-</sup>

- 1

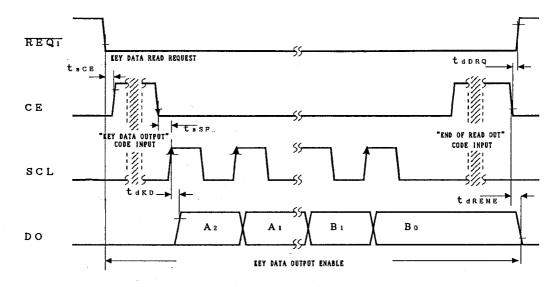

• Key Data Output Timing Characteristics

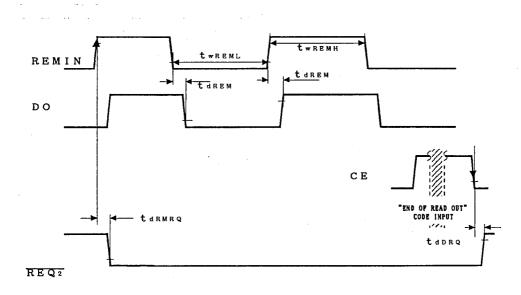

• REMIN Input Data and DO Output Data Timing Characteristics

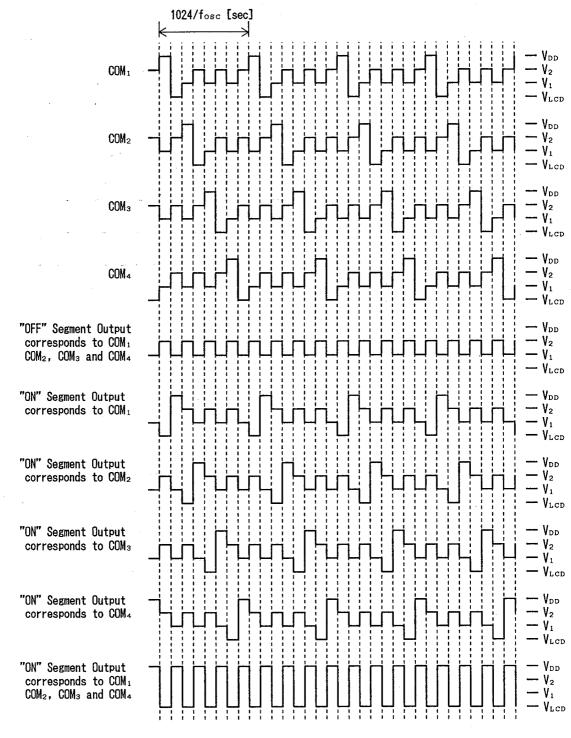

■ LCD Driving Waveform (1/4DUTY • 1/3BIAS)

New Japan Radio Co., Ltd.

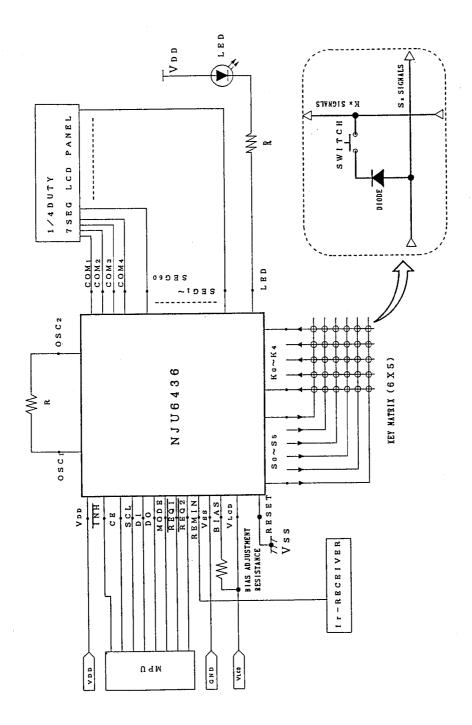

### APPLICATION CIRCUITS

**MEMO**

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.