#### CMOS 4-BIT MICROCONTROLLER

## TMP47C800N TMP47C800F

The 47C800 is a high speed and high performance 4-bit single chip microcomputer, integrating ROM, RAM, input/output ports, timer/counters, a serial interface, and two clock generators on a chip.

The 47C800 is the standard type device in the TLCS-470 series, and provides high current output capability for LED direct drive.

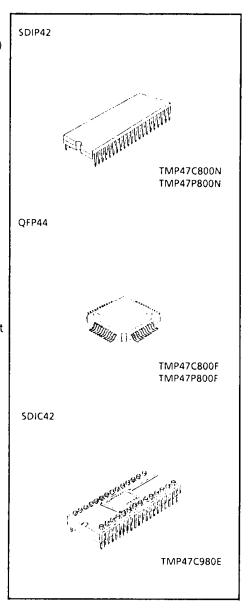

| PART No.   | ROM          | RAM         | PACKAGE | ОТР        | PIGGYBACK  |

|------------|--------------|-------------|---------|------------|------------|

| TMP47C800N | 8192 × 8-bit | E12 v 4 bis | SDIP42  | TMP47P800N | TMP47C980E |

| TMP47C800F | 0134 X 0-DIE | 512 × 4-bit | QFP44   | TMP47P800F |            |

#### **FEATURES**

- ◆ 4-bit single chip microcomputer

- ♦Instruction execution time: 1.3µs (at 6MHz), 244µs (at 32.8kHz)

- ♦92 basic instructions

- ◆Table look-up instructions

- ◆5-bit to 8-bit data conversion instruction

- ◆ Subroutine nesting: 15 levels max.

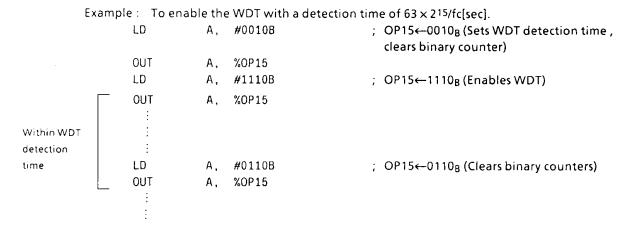

- ◆6 interrupt sources (External: 2, Internal: 4)

All sources have independent latches each, and multiple interrupt control is available.

- ◆1/O port (36 pins)

- Input 2 ports 5 pins

Output 2 ports 8 pins

I/O 6 ports 23 pins

- ♦Interval Timer

- ◆Two 12-bit Timer/Counters

Timer, event counter, and pulse width measurement mode

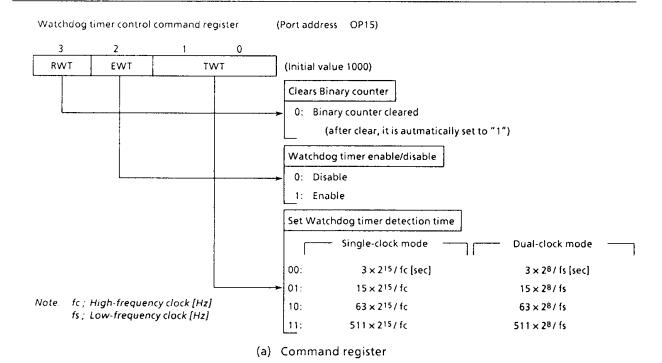

- ◆Watchdog Timer

- ◆ Serial Interface with an 8-bit buffer External/internal clock, leading/trailing edge shift, and 4/8-bit mode

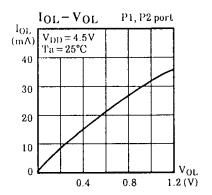

- ◆ High current outputs

LED direct drive capability (typ. 20 mA × 8 bits).

- ◆ Dual-clock operation High-speed/Low-power-consumption operating mode

- ◆ Hold function

Battery/Capacitor back-up

◆Real Time Emulator: BM47C800A

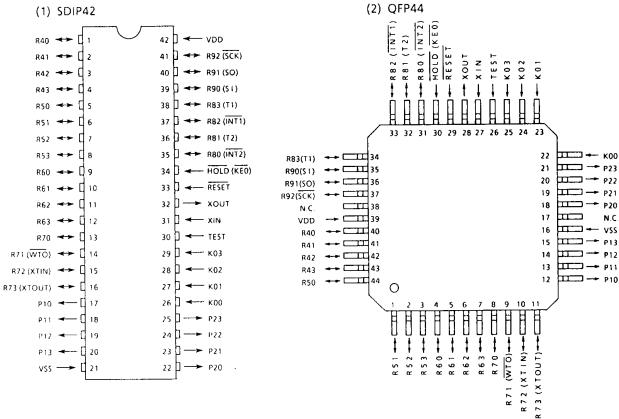

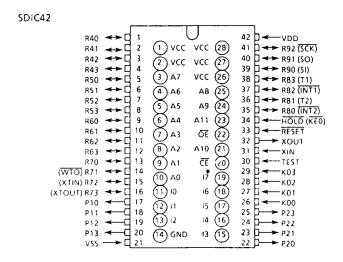

## PIN ASSIGNMENTS (TOP VIEW)

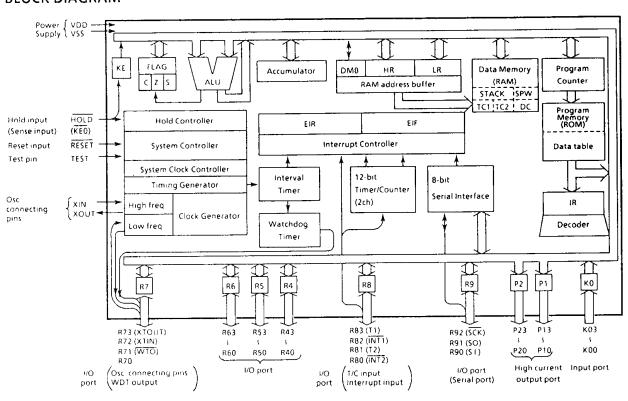

## **BLOCK DIAGRAM**

## PIN FUNCTION

| PIN NAME    | Input/Output  | FUNCTION                                                                       |                                   |  |  |

|-------------|---------------|--------------------------------------------------------------------------------|-----------------------------------|--|--|

| K03 - K00   | Input         | 4-bit input port                                                               |                                   |  |  |

| P13 - P10   | 0             | 4-bit output port with latch.                                                  |                                   |  |  |

| P23 - P20   | - Output      | 8-bit data are output by the 5-bit to 8-bit data co                            | onversion instruction [OUTB @HL]. |  |  |

| R43 - R40   |               | 4-bit I/O port with latch.                                                     |                                   |  |  |

| R53 - R50   | 1/0           | When used as the input port, the latch must be s                               | et to "1".                        |  |  |

| R63 - R60   |               |                                                                                |                                   |  |  |

| R73 (XTOUT) | I/O (Output)  |                                                                                | Resonator connecting pins         |  |  |

| R72 (XTIN)  | I/O (Input)   | 4-bit I/O port with latch.  When used as the input port or watchdog            | (Low-frequency)                   |  |  |

| R71 (ŴŤÕ)   | I/O (Output)  | timer output pin, the latch must be set to "1".                                | Watchdog timer output             |  |  |

| R70         | 1/0           |                                                                                |                                   |  |  |

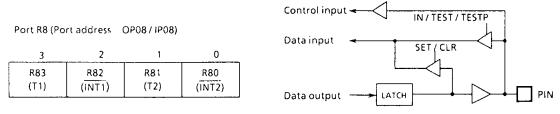

| R83 (T1)    |               |                                                                                | Timer/Counter 1 external input    |  |  |

| R82 (INTI)  | I/O (Input)   | 4-bit I/O port with latch.  When used as the input port, external              | External interrupt 1 input        |  |  |

| R81 (T2)    | //O (input)   | interrupt input pin, or timer/counter input pin, the latch must be set to "1". | Timer/Counter 2 external input    |  |  |

| R80 (ĪNT2)  |               | pin, the laten must be set to                                                  | External interrupt 2 input        |  |  |

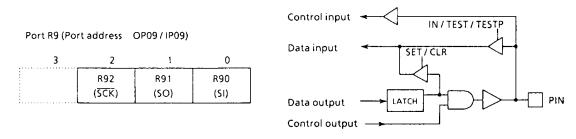

| R92 (SCK)   | 1/0 (1/0)     | 3-bit I/O port with latch.                                                     | Serial clock I/O                  |  |  |

| R91 (SO)    | I/O (Output)  | When used as the input port or serial port, the                                | Serial data output                |  |  |

| R90 (S1)    | I/O (Input)   | latch must be set to "1".                                                      | Serial data input                 |  |  |

| XIN         | Input         | Resonator connecting pins (High-frequency).                                    |                                   |  |  |

| XOUT        | Output        | For inputting external clock, XIN is used and XO                               | UT is opened.                     |  |  |

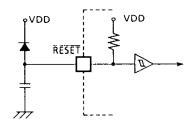

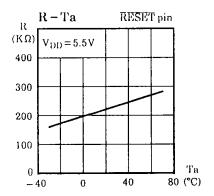

| RESET       | Input         | Reset signal input                                                             |                                   |  |  |

| HOLD (KEO)  | Input (Input) | HOLD reques Urelease signal input                                              | Sense input                       |  |  |

| TEST        | Input         | Test pin for shipping. Be fixed to low level.                                  |                                   |  |  |

| VDD         | Power Supply  | + 5V                                                                           |                                   |  |  |

| VSS         | 1             | OV(GND)                                                                        |                                   |  |  |

#### **OPERATIONAL DESCRIPTION**

#### 1. SYSTEM CONFIGURATION

- (1) 1Program Counter (PC)

- (2) Program Memory (ROM)

- (3) H Register, L Register, and Data Memory Bank Selector (DMB)

- (4) Data Memory (RAM)

- a. Stack

- b. Stack Pointer Word (SPW)

- c. Data Counter (DC)

- (5) ALU, Accumulator

- (6) Flags

- (7) Clock Generator, Timing Generator

- (8) System Clock Controller

- (9) Input/Output Ports

- (10) Interval Timer

- (11) Timer/Counters (TC1, TC2)

- (12) Serial Interface

- (13) Watchdog Timer

- (14) Interrupt Controller

- (15) Hold Controller

- (16) Reset Circuit

Concerning the above component parts, the hardware configuration and functions are described.

#### 2. INTERNAL CPU FUNCTION

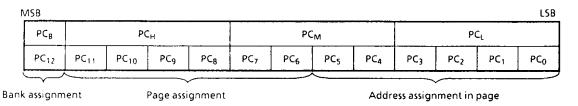

## 2.1 Program Counter (PC)

The program counter is a 13-bit binary counter which indicates the address of the program memory storing the next instruction to be executed. Normally, the PC is incremented by the number of bytes of the instruction every time it is fetched. When a branch instruction or a subroutine instruction has been executed or an interrupt has been accepted, the specified values listed in Table 2-1 are set to the PC. The PC is initialized to "0" during reset.

Figure 2-1. Configuration of Program Counter

The PC can directly address an 8192-byte address space. However, with the short/middle branch and subroutine call instructions, the following points must be considered:

- (1) Short branch instruction [BSS a]

- In [BSS a] instruction execution, when the branch condition is satisfied the status flag is "1", the value specified in the instruction is set to the lower 6 bits of the PC. That is, [BSS a] becomes the inpage branch instruction. When [BSS a] is stored at the last address of the page, the upper 7 bits of the PC point the next page, so that branch is made to the next page.

- (2) Middle branch instruction [BS a]

In [BS a] instruction execution, when the branch condition is satisfied, the value specified in the instruction is set to the lower 12 bits of the PC. That is, [BS a] becomes the in-bank branch instruction.

|      | Instructio   | on     |          | Condition                                                              | Program Counter (PC)                   |                                             |      |       |             |                     |                     |                   |          |                  |                     |          |       |

|------|--------------|--------|----------|------------------------------------------------------------------------|----------------------------------------|---------------------------------------------|------|-------|-------------|---------------------|---------------------|-------------------|----------|------------------|---------------------|----------|-------|

|      | Operatio     | n      |          | Condition                                                              | PC <sub>12</sub>                       | PC <sub>1</sub>                             | 1 PC | 10 PC | 9 P         | C <sub>8</sub> PC   | C <sub>7</sub> PC   | 6 P               | С5 Р     | C4 P             | 3 PC                | 2 PC     | PC0   |

|      | BSL          | a      | SF = 1   | (Branch condition is satisfied)                                        |                                        | Immediata data specified by the instruction |      |       |             |                     |                     |                   |          |                  |                     |          |       |

|      | 050          | ŭ      | SF = 0   | (Branch condition is not satisfied)                                    |                                        |                                             |      |       |             |                     | + 3                 |                   |          |                  |                     |          |       |

|      |              |        |          | Lower 12-bit address ≠ FFE, FFF <sub>H</sub>                           | Hold                                   |                                             |      |       | imme        | diata d             | ata spe             | cified            | by the   | instruc          | tion                |          | ·     |

| c    | BS           | a      | SF = 1   | Lower 12-bit address = FFE, FFF <sub>H</sub><br>(Last address in bank) | + 1                                    |                                             |      |       | immed       | diata d             | ata spe             | cified            | by the   | instruc          | tion                |          |       |

| -    |              |        | SF = 0   |                                                                        |                                        |                                             |      |       |             |                     | + 2                 |                   |          |                  |                     |          |       |

| ٥    |              | SF = 1 |          | Lower 6-bit address # 3F <sub>H</sub>                                  |                                        |                                             |      | Hole  | <del></del> |                     |                     |                   | imme     |                  | ata spe<br>structio | cified b | y the |

| -    | BSS          |        | ) Sr = 1 | Lower 6-bit address = 3F <sub>H</sub><br>(Last address in page)        | + 1                                    |                                             |      | Imme  |             | ata spe<br>structio | cified b            | y the             |          |                  |                     |          |       |

| -    |              |        |          | SF = 0                                                                 |                                        | + 1                                         |      |       |             |                     |                     |                   |          |                  |                     |          |       |

| -    | CALL         | a      |          |                                                                        | 0                                      | 0                                           |      |       | lm          | imedia              | la data             | specil            | fied by  | the ins          | tructio             | n        |       |

|      | CALLS        | a      |          |                                                                        | 0                                      | 0                                           | 0    | 0     | 0           | The va              | lue ger<br>pecifier | nerate<br>d by th | d by the | ne imm<br>uction | ediate              | 1        | 1 0   |

|      | RET          |        |          |                                                                        | The return address restored from stack |                                             |      |       |             |                     |                     |                   |          |                  |                     |          |       |

|      | RETI         |        |          |                                                                        |                                        |                                             |      | Ti    | ne reti     | urn add             | dress re            | stored            | from     | stack            |                     |          |       |

|      | Others       |        |          |                                                                        |                                        |                                             | Inc  | remen | ted by      | the nu              | nuper               | of byte           | es in th | ie instri        | iction              |          |       |

| Inti | errupt accep | otance |          |                                                                        | 0                                      | 0                                           | 0    | 0     | 0           | 0                   | 0                   | 0                 | 0        | Int              | errupt              | vector   | 0     |

|      | Reset        |        |          |                                                                        | 0                                      | 0                                           | 0    | 0     | 0           | 0                   | 0                   | 0                 | 0        | 0                | 0                   | 0        | 0     |

Table 2-1. Status Change of Program Counter

When first byte or second byte of this instruction is stored at the last address of the bank, the most significant bit of the PC point the next bank, so that branch is made to the next bank.

## (3) Subroutine call instruction [CALL a]

In [CALL a] instruction execution, the contents of the PC are saved to the stack then the value specified by the instruction is set to the PC. The address which can be specified by the instruction consists of 11 bits and the upper 2 bits of the PC is always "0". Therefore, the entry address of the subroutine should be within an address range of 0000H through 07FFH.

## 2.2 Program Memory (ROM)

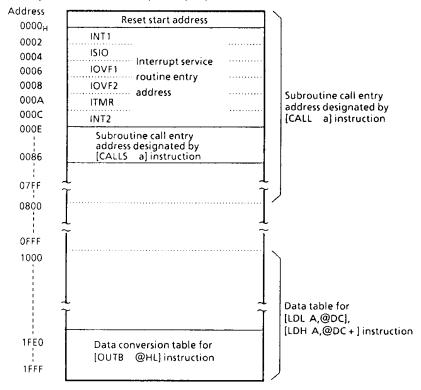

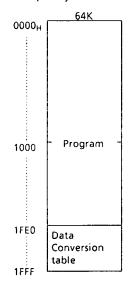

The 47C800 has  $8192 \times 8$  bits (addresses  $0000_H$  through 1FFF<sub>H</sub>) of program memory (mask ROM).

Programs and fixed data are stored in the program memory. The instruction to be executed next is read from the address indicated by the contents of the PC. The fixed data can be read by using the table look-up instructions or 5-bit to 8-bit data conversion instruction.

Figure 2-1. Configuration of Program Memory

- (1) Table look-up instructions [LDL A,@DC], [LDH A,@DC+]

- The table look-up instructions read the lower and upper 4 bits of the fixed data stored at the address specified in the data counter (DC) to place them into the accumulator. [LDL A,@DC] instruction reads the lower 4 bits of fixed data and [LDH A,@DC+] instruction reads the upper 4 bits. The DC is a 12-bit register, and it can specify an address within the range of 1000<sub>H</sub> through 1FFF<sub>H</sub> of the program memory.

- (2) 5-bit to 8-bit data conversion instruction [OUTB @HL]

The 5-bit to 8-bit data conversion instruction reads the fixed data (8 bits) from the data conversion table in the program memory to output the upper 4 bits to port P2 and the lower 4 bits to port P1. The table is located in the last 32-byte space (addresses 1FEO<sub>H</sub> through 1FFF<sub>H</sub>) in the program memory with the lower address consisting of the 5 bits obtained by linking the data memory contents specified by the HL register pair and the content of the carry flag.

This instruction is suitable for such applications as converting BCD data into an output code to the 7-segment display elements.

Example: The following shows that the BCD data at address 2F<sub>H</sub> in data memory is converted into the 7-segment code (e.g., anode common LED) to be output to ports P2 and P1.

## 2.2.1 Program Memory Map

Figure 2-3 shows the program memory map. Address  $0000_{\rm H}$  through  $0086_{\rm H}$  and  $1FE0_{\rm H}$  through  $1FFF_{\rm H}$  of the program memory are also used for special purposes.

Figure 2-3. Program Memory Map

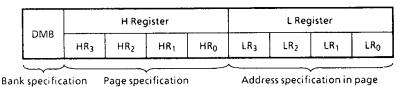

#### H Register, L Register, and Data Memory Bank Selector (DMB) 2.3

The H register and the L register are 4-bit general registers. They are also used as a register pair (HL) for the data memory (RAM) addressing pointer. The data memory consists of pages, each page being 16 words long (1word = 4bits). The H register specifies a page and the L register specifies an address in the page. The data memory consists of two banks (bank0 and bank1). The data memory bank selector (DMB) is a 1-bit register to specify a data memory bank. During reset, the DMB is initialized to "0". The DMB is set or cleared by the [CLR DMB] or [SET DMB] instructions. The currently selected data memory bank can be known by executing the [TEST DMB] or [TESTP DMB] instruction.

The L register has the automatic post-increment/decrement capability, implementing the execution of composite instructions. For example, [ST A,@HL + ] instruction automatically increments the contents of the L register after data transfer. During the execution [SET @L], [CLR @L], or [TEST @L] instruction, the L register is also used to specify the bits corresponding to I/O port pins R73 through R40 (the indirect addressing of port bits by the L register).

Example 1: To write immediate values "5" and "FH" to data memory (bank 0) addresses 10H and 11H.

CLR DMB ; DMB ← 0 LD HL,#10H ; HL ← 10<sub>H</sub> RAM [10<sub>H</sub>]  $\leftarrow$  5,  $\leftarrow$  LR + 1 ST #5,@HL+ ST #0FH,@HL+ ; RAM  $\{11_H\} \leftarrow F_H$ , LR  $\leftarrow$  LR + 1

Example 2: The output latch of R71 pin is set to "1" by the L register indirect addrressing bit manipulation instruction.

> LD L,#1101B; Sets R71 pin address to L register SET ; R71 ← 1

Figure 2-4. Configuration of H, L registers and DMB

#### 2.4 Data Memory (RAM)

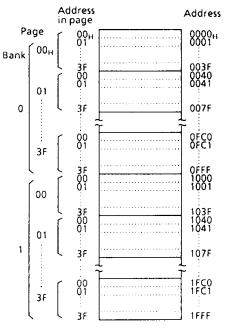

The 47C800 has a total of  $512 \times 4$  bits of data memory (RAM), 256 x 4 bits (addresses 00H through FFH) on each of banks (bank0 and bank1).

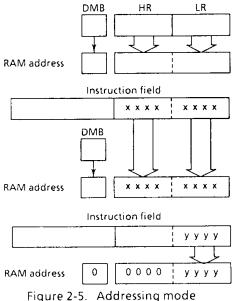

The data memory is addressed in one of three ways (addressing modes):

(1) Register-indirect addressing mode In this mode, a bank is specified by the DMB, a page by the H register and an address in the page by the L register.

Example: LD A,@HL Acc ← RAM[HL]

(2) Direct addressing mode

An address in the bank is directly specified by the 8 bits of the second byte (operand) in the instruction field. The bank is specified by the DMB.

Example: LD A,2CH Acc ← RAM[2CH]

(3) Zero-page addressing mode

An address in zero-page of bank 0 (addresses 00H through OFH) by the lower 4 bits of the second byte (operand) in the instruction field.

Example: ST #3,05H RAM[05<sub>H</sub>] ← 3

When power-on is performed, the contents of the RAM become unpredictable, so that they must be initialized by the initialization routine.

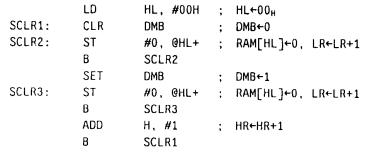

Example: To clear RAM

## 2.4.1 Data Memory Map

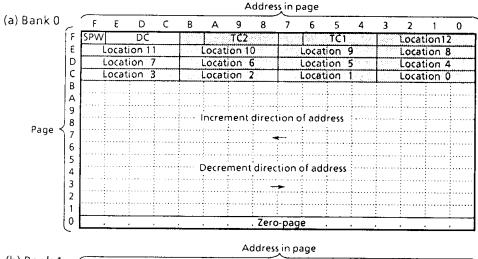

Figure 2-6 shows the data memory map. The data memory is also used for the following special purposes: Note that this special function area is provided only on bank 0.

① Stack

- Count registers of the timer/counters (TC1, TC2)

- ② Stack pointer word (SPW)

- ⑤ Zero-page

- 3 Data counter (DC)

Figure 2-6. Data Memory Map

TOSHIBA TMP47C800/980

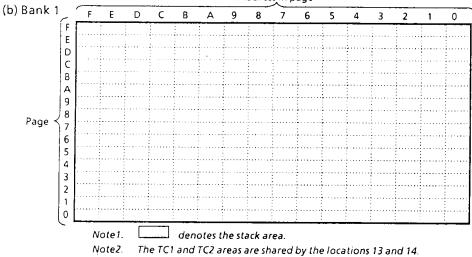

#### (1) Stack

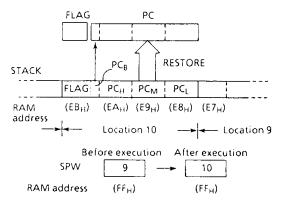

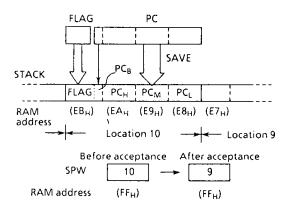

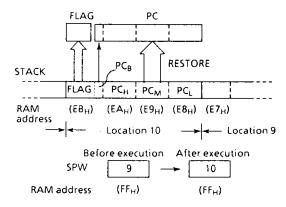

The stack provides the area in which the return address is saved before a jump is performed to the processing routine at the execution of a subroutine call instruction or the acceptance of an interrupt. When a subroutine call instruction is executed, the contents (the return address) of the program counter are saved; when an interrupt is accepted, the contents of the program counter and flags are saved.

When returning from the processing routine, executing the subroutine return instruction [RET] restores the contents of the program counter from the stack; executing the interrupt return instruction [RETI] restores the contents of the program counter and flags.

The stack consists of up to 15 levels (locations 0 through 14) which are provided in the bank 0 of data memory (addresses CO<sub>H</sub> through FB<sub>H</sub>). Each location consists of 4-word data memory. Locations 13 and 14 are shared by the count registers of the timer/counters (TC1, TC2) to be described later.

The save/restore locations in the stack are determined by the stack pointer word (SPW). The SPW is automatically decremented after save and incremented before restore. That is, the value of the stack pointer word indicates the stack location number for the next save.

## (2) Stack Pointer Word (SPW)

Address FF<sub>H</sub> in the data memory (bank 0) is called the stack pointer word, which identifies the location in the stack to be accessed (save or restore).

Generally, location number 0 to 12 can be set to the SPW, providing up to 13 levels of stack nesting. Locations 13 and 14 are shared by the count registers of the timer/counters to be described later; therefore, when the timer/counters are not used, the stack area of up to 15 levels is available. Address FF<sub>H</sub> is assigned with the SPW, so that the contents of the SPW cannot be set "15" in any case. The SPW is automatically updated when a subroutine call is executed or an interrupt is accepted. However, if it is used in excess of the stack area permitted by the data memory allocating configuration, the user-processed data may be lost. (For example, when the user-processed data area is in an address range 00<sub>H</sub> through CF<sub>H</sub>, up to location 4 of the stack are usable. If an interrupt is accepted with location 4 already used, the user-processed data stored in addresses CC<sub>H</sub> through CF<sub>H</sub> corresponding to the location 3 area is lost.)

The SPW is not initialized by hardware, requiring to write the initial value (the location with which the use of the stack starts) by using the initialization routine. Normally, the initial value of "12" is set to the SPW.

Example: To initialize the SPW (when the stack is used from location 12)

LD A,#12; SPW  $\leftarrow$  12

CLR DMB ST A,OFFH

(a) At execution of a subroutine call instruction

(c) At execution of a subroutine return instruction

(b) At acceptance of an interrupt

(d) At execution of an interrupt return instruction

Figure 2-7. Accessing Stack (Save/Restore)

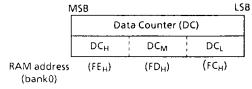

#### (3) Data counter (DC)

The data counter is a 12-bit counter to specify the address of the data table to be referenced in the program memory (ROM). Data table reference is performed by the table look-up instructions [LDL A,@DC] and [LDH A,@DC +]. The data tables are set in the program memory area between addresses 1000H and

Figure 2-8. Data Counter

1FFF<sub>H</sub>. The DC is assigned with a RAM address in unit of 4 bits.

Therefore, the RAM manipulation instruction is used to set the initial value or read the contents of the DC.

Example: To set the DC to 780<sub>H</sub>

CLR DMB ; DMB+0

LD HL, #0FCH ; Sets RAM address of DC<sub>L</sub> to HL register pair.

ST #0H, @HL+ ; DC←780<sub>H</sub>

ST #8H, @HL+

ST #7H, @HL+

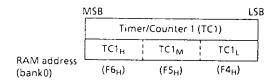

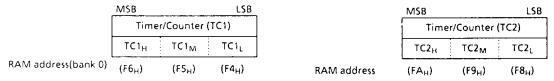

## (4) Count registers of the timer/counter (TC1, TC2)

The 47C800 has two 12-bit timer/counters. The count register of the timer/counter is assigned with RAM addresses in unit of 4 bits, so that the initial value setting or contents reading is performed by using RAM manipulation instruction.

The count registers are shared by the stack area (locations 13 and 14) described earlier, so that the stack is usable from location 13 when the timer/counter 1 is not used. When none of timer/counter 1 and timer/counter 2 are used, the stack is usable from location 14.

When both timer/counter 1 and timer/counter 2 are used, the data memory (bank 0) locations at addresses  $F7_H$  and  $FB_H$  can be used to store the user-processed data.

Figure 2-9. Count Registers of Timer/Counters (TC1,TC2)

### (5) Zero - page

The 16 words (at addresses  $00_H$  through  $0F_H$ ) of the page zero of the data memory (bank 0) can be used as the user flag or pointer by using zero-page addressing mode instructions (comparison, addition, transfer, and bit manipulation), providing enhanced efficiency in programming.

Example: To write "8" to address 09H if bit 2 at address 04H in the data memory (bank 0) is "1".

TEST 04H, 2; Skips if bit 2 at address 04<sub>H</sub> in the is "0".

B SKIP

ST #8, 09H; Writes "8" to address 09<sub>H</sub> in the RAM.

## 2.5 ALU and Accumulator

## 2.5.1 Arithmetic / Logic Unit (ALU)

SKIP:

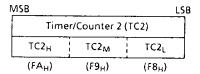

The ALU performs the arithmetic and logic operations specified by instructions on 4-bit binary data and outputs the result of the operation, the carry information (C), and the zero detect information (Z).

#### (1) Carry information (C)

The carry information indicatets a carry-out from the most significant bit in an addtion. A subtraction is performed as addition of two's complement, so that, with a subtraction, the carry information indicates that there is no borrow to the most significant bit. With a rotate instruction, the information indicates the data to be shifted out from the accumulator.

#### (2) Zero detect information (Z)

This information is "1" when the operation result or the data to be transferred to the accumulator/data memory is " $0000_R$ ".

Example: The carry information (C) and zero detect information (Z) for 4-bit additions and subtractions.

| Operation | Result                   | C | Z |

|-----------|--------------------------|---|---|

| 4 + 2 =   | 6                        | 0 | 0 |

| 7 + 9 =   | 0                        | 1 | 1 |

| 8 - 1 =   | 7                        | 1 | 0 |

| 2 - 2 =   | 0                        | 1 | 1 |

| 5 - 8 = - | - 3 (1101 <sub>B</sub> ) | 0 | 0 |

Note. Cin indicates the carry input specified by instruction.

Figure 2-10. ALU

## 2.5.2 Accumulator (Acc)

The accumulator is a 4-bit register used to hold source data or results of the operations and data manipulations.

# MSB LSB 3 2 1 0

Figure 2-11. Accumulator

| 3  | 2  | 1  | 0 |

|----|----|----|---|

| CF | ZF | SF |   |

Figure 2-12. Flag

## 2.6 Flags

There are a carry flag (CF), a status flag (SF), and zero flag (ZF), each consisting of 1 bit. These flags are set or cleared according to the condition specified by an instruction. When an interrupt is accepted, the flags are saved on the stack along with the program counter. When the [RETI] instruction is executed, the flags are restored from the stack to the states set before interrupt acceptance.

## (1) Carry flag (CF)

The carry flag holds the carry information received from the ALU at the execution of an addition/subtraction with carry instruction, a compare instruction, or a rotate instruction. With a carry flag test instruction, the CF holds the value specified by it.

- (1) Addition/subtraction with carry instructions [ADDC A,@HL], [SUBRC A,@HL] The CF becomes the input (Cin) to the ALU to hold the carry information.

- ② Compare instructions [CMPR A,@HL], [CMPR A,#k] The CF holds the carry information (non-borrow).

- (3) Rotate instructions [ROLC A], [RORC A]

The CF is shifted into the accumulator to hold the carry information (the data shifted out from the accumulator).

- (4) Carry flag test instructions [TESTP CF], [TEST CF] With [TESTP CF] instruction, the content of the CF is transferred to the SF then the CF is set to "1".

With [TEST CF] instruction, the value obtained by inverting the content of the CF is transferred to the SF then the CF is cleared to "0".

### (2) Zero flag (ZF)

The zero flag holds the zero detect information (Z) received from the ALU at the execution of an operational instruction, a rotate instruction, an input instruction, or a transfer-to-accumulator instruction.

## (3) Status flag (SF)

The SF provides the branch condition for a branch instruction. Branch is performed when the SF is set to "1". Normally the SF is set to "1", so that any branch instruction can be regarded as an unconditional branch instruction. When a branch instruction is executed upon set or clear of the SF according to the condition specified by instruction, this instruction becomes a conditional branch instruction. During reset, the SF is initialized to "1", other flags are not affected.

Example: When the following instructions are executed with the accumulator, H register, L register, data memory address 07<sub>H</sub>, and carry flag are "C<sub>H</sub>", "0<sub>H</sub>", "7<sub>H</sub>", "5<sub>H</sub>", and "1" respectively, the contents of the accumulator and flags become as follows:

|       |        |      | Acc after       | Flag af | Flag after execution |    |  |  |

|-------|--------|------|-----------------|---------|----------------------|----|--|--|

| Inst  | tructi | on . | execution       | CF      | ZF                   | SF |  |  |

| ADDC  | Α,     | @HL  | 2 <sub>H</sub>  | 1       | 0                    | 0  |  |  |

| SUBRC | Α,     | @нг  | 9 <sub>H</sub>  | 0       | 0                    | 0  |  |  |

| CMPR  | Α,     | @HL  | C <sub>11</sub> | 0       | 0                    | 1  |  |  |

| AND   | Α,     | @нг  | 4 <sub>H</sub>  | 1       | 0                    | 1  |  |  |

| LD    | Α,     | @HL  | 5 <sub>H</sub>  | 1       | 0                    | 1  |  |  |

|      |          | Acc after       | Flag af | Flag after execution |    |  |  |

|------|----------|-----------------|---------|----------------------|----|--|--|

| Ins  | truction | execution       | CF      | ZF                   | SF |  |  |

| LD   | A, #0    | 0н              | 1       | 1                    | 1  |  |  |

| ADD  | A, #4    | 0н              | 1       | 1                    | 0  |  |  |

| DEC  | Α        | Вн              | 1       | 0                    | 1  |  |  |

| ROLC | А        | 9 <sub>H</sub>  | 1       | 0                    | 0  |  |  |

| RORC | Α        | E <sub>F4</sub> | 0       | 0                    | 1  |  |  |

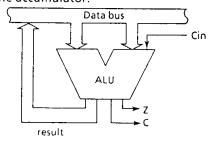

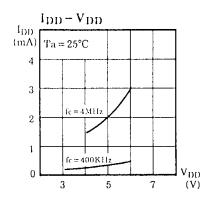

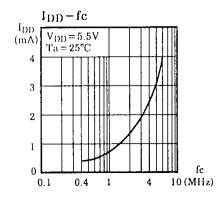

# 2.7 Clock Generator, Timing Generator, and System Clock Controller

Figure 2-13. Clock Generator, Timing Generator and System Clock Controller

## 2.7.1 Clock Generator

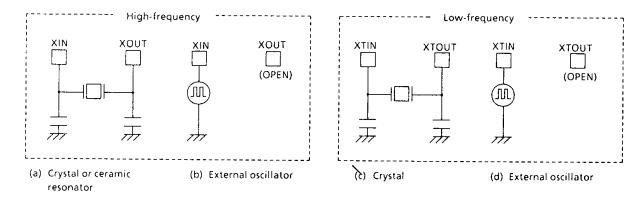

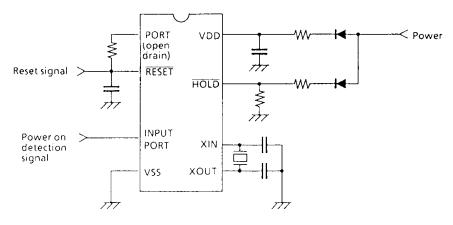

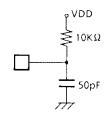

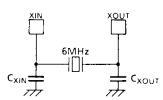

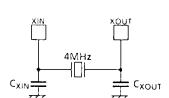

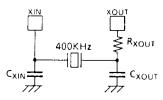

The clock generator produces the basic clock pulses which provide the system clock to be supplied to the CPU and peripheral hardware. It contains two oscillators: a high-frequency clock oscillator and a low-frequency clock oscillator. Power consumption can be reduced by switching to the low power operation based on the low-frequency clock by the system clock controller. The high-frequency clock and the low-frequency clock can be easily obtained by attaching a resonator between the XIN and XOUT pins and the XTIN and XTOUT pins, respectively. The system clock can also be obtained from the external oscillator.

Figure 2-14. Examples of Resonator Connection

Note. Accurate adjustment of the oscillation frequency

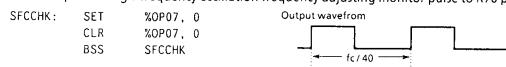

Although no hardware to externally and directly monitor the clock pulse is not provided, the oscillation frequency can be adjusted by making the program to output the pulse with a fixed frequency to the port with the all interrupts disabled and timer/counters stopped and monitoring this pulse. With a system requiring the oscillation frequency adjustment, the adjusting program must be created beforehand.

Example: To output the high-frequency oscillation frequency adjusting monitor pulse to R70 pin.

## 2.7.2 Timing Generator

The timing generator produces the system clocks from clock pulse which are supplied to the CPU and peripheral hardweare.

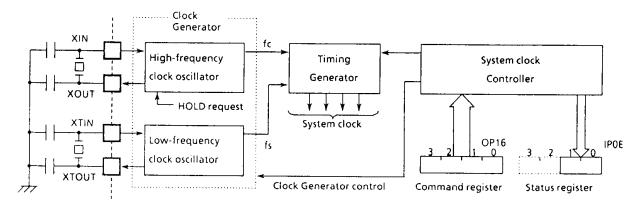

## 2.7.3 System Clock Controller

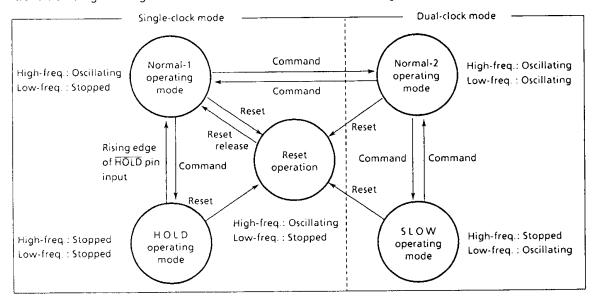

The system clock controller starts or stops the high-frequency and low-frequency clock oscillator and switches between the basic clocks. The operating mode is generally divided into the single-clock mode and the dual-clock mode, which are controlled by command. Figure 2-15 shows the operating mode transition diagram. Figure 2-16 shows the command and status registers.

Figure 2-15. Operating Mode Transition Diagram

## a. Single-clock mode

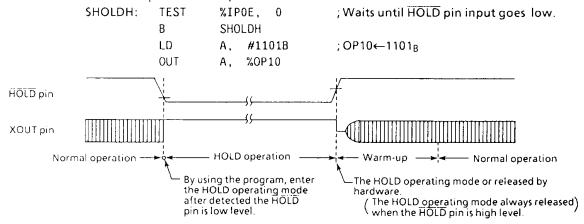

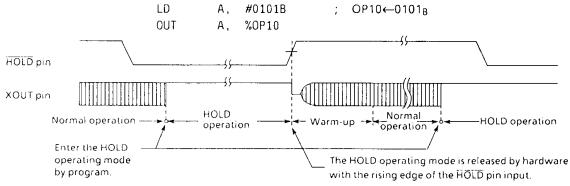

- (f) Normal-1 operating mode In this mode, the CPU and the peripheral hardware are operated on the high-frequency clock. At reset release, this mode is set.

- (2) HOLD operating mode In this mode, the system operations are all stopped, holding the internal states valid immediately before the stop at the low power consumption.

#### b. Dual-clock mode

- (1) Normal-2 operating mode In this mode, the CPU is operated on the high-frequency clock but many peripheral hardware operate on the low-frequency clock.

- 2 SLOW operating mode

In this mode, the high-frequency clock oscillation is stopped to operate the CPU and the peripheral hardware on the low-frequency clock, thereby reducing power consumption.

#### Notes

- 1. In the HOLD and SLOW operating modes, the power consumed by the oscillator and the internal hardware is reduced. However, the power for the pin interface (depending on the external circuitry and program) is not directly associated with the low-power consumption operation. This must be considered in system design as well as interface circuit design.

- 2. Normal-1 and Normal-2 operating modes are sometimes referred to as the Normal operating mode collectively.

System clock control is performed by the command register (OP16). During reset, this register is initialized to "0" and the single-clock mode is selected.

Each state at operating mode switching can be read from the status register (IPOE).

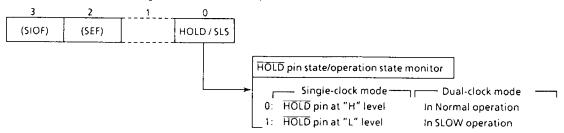

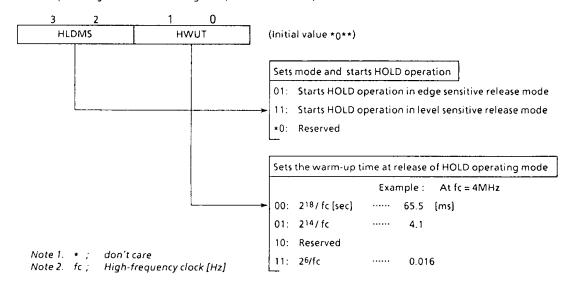

System clock control command register (Port address OP16)

System clock control status register (Port address IPOE)

Figure 2-16. System Clock Control Command Register/Status Register

## (1) Single-clock mode

In this mode, only the high-frequency clock oscillator is used. Pins R72 (XTIN) and R73 (XTOUT) become the ordinary I/O port. The HOLD operating mode is available for reducing power consumption. It is controlled by the command register (OP10). In this mode, therefore, the system clock control command register (OP16) need not be manipulated. For the details of the HOLD operation, refer to Subsection "5.1 HOLD Operating Mode".

## (2) Dual-clock mode

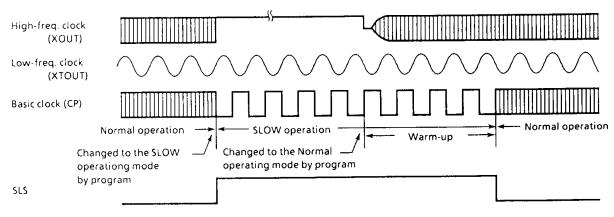

In this mode, the Normal-2 operation is generally performed by generating the system clock from the high-frequency clock (fc). As required, the SLOW operation can be performed by generating the system clock from the low-frequency clock (fs). In the SLOW operation, the high-frequency clock oscillation automatically stops, enabling the low-power voltage operation or the low-power consumption operation. Instruction execution does not stop when the operation speed switching is performed. However, some peripheral hardware capabilities may be affected. For details, refer to the description of the relevant operation.

## (3) System clock switching control

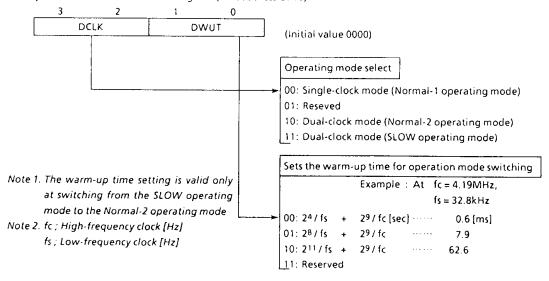

The following describes the switching between the Normal-2 and SLOW operations in the dual clock mode. During reset, the command register is initialized to the single-clock mode. It must be set to the Normal-2 operation of the dual-clock mode.

- a. Switching from Normal-2 operation to SLOW operation

Setting bit 2 of command register (OP16) to "1" stops the high-frequency clock oscillation and switches the system clock into low-frequency clock. Note that low-frequency clock oscillator takes a few seconds from the start of its oscillation to reach the stable oscillation. Therefore, switch to the SLOW operation mode immediately after the transition from Normal-1 to Normal-2 should be inhibited by program until stable low-frequency clock is supplied (for a few seconds as mentioned above).

- b.Returning from SLOW operation to Normal-2 operation

Bit 2 of the command register is cleared to "0" and, at the same time, the warm-up time for return is set to DWUT. When the warm-up time has passed, the Normal-2 operation takes place.

By monitoring SLS (bit 0 of the status register), the current operating mode can be known.

Figure 2-17. System Clock Switching Timing

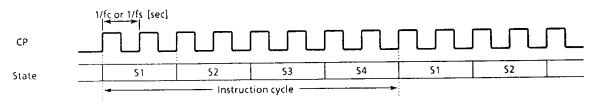

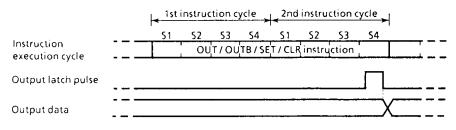

## 2.7.4 Instruction Cycle

The instruction execution and on-chip peripheral hardware operations are performed in synchronization with the basic clock. The smallest unit of instruction execution is called the "instruction cycle". The TLCS-470 series instruction set has 3 kinds of instructions, 1-cycle instruction to 3-cycle instruction. Each instruction cycle consists of 4 states (S1 through S4). Each state consists of 2 basic clock pulses.

Figure 2-18. Instruction Cycle

#### 3. PERIPHERAL HARDWARE FUNCTION

## 3.1 Ports

The data transfer with the external circuit and the command/status/data transfer with the internal circuit are performed by using the I/O instructions (13 kinds). There are 4 types of ports:

(1) I/O port

; Data transfer with external circuit

② Command register

; Control of internal circuit

③ Status register

Reading the status signal from internal circuit

(4) Data register

; Data transfer with internal circuit.

These ports are assigned with port addresses ( $00_H$  through  $1F_H$ ). Each port is selected by specifying its port address in an I/O instruction. Table 3-1 lists the port address assignments and the I/O instructions that can access the ports.

#### 3.1.1 I/O Ports

The 47C800 has 10 I/O ports (36 pins) each as follows:

① K0

; 4-bit input

② P1, P2

; 4-bit output

③ R4, R5, R6

; 4-bit input/output

④ R7

; 4-bit input/output (shared with the low-frequency reasonator

connecting pins and the watchdog timer output)

(5) R8

; 4-bit input/output (shared with external interrupt request input

and timer/counter input)

6 R9

; 3-bit input/output(shared with serial port)

(7) KE

; 1-bit sense input (shared with hold request/release signal input)

Each output port contains a latch, which holds the output data. The input ports have no latch; therefore, it is desired hold data exterenally until it is read or to read twice or more before processing it.

| tod             | Port                     | +                                       |                        |                        | Input/Output | utput instructions | tions                  |                         |                            |

|-----------------|--------------------------|-----------------------------------------|------------------------|------------------------|--------------|--------------------|------------------------|-------------------------|----------------------------|

| Address (**)    | Input (IP**)             | Output (OP**)                           | IN %p, A<br>IN %p, @HL | OUT A,%p<br>OUT @HL,%p | OUT #k, %p   | OUTB @HL           | SET %p, b<br>CLR %p, b | TEST %p,b<br>TESTP %p,b | SET @L<br>CLR @L<br>TEST@L |

| н00             |                          |                                         | 00                     | 1 (                    | 1 (          | , (                | 1 (                    | 00                      | ı                          |

| 01              |                          | P1 output port                          | )(<br>                 | )(                     | )(           | (Note 2)           | )(                     | )(                      | ł                          |

| 02              | P2 output latch          | P2 output port                          | O<br>                  | )<br>                  | )<br>)       |                    | )                      | )                       | ı                          |

| 03              |                          |                                         | Ι (                    | ι (                    | ۱ (          | ı                  | ۱ (                    | ١(                      | ۱(                         |

| 04              | R4 input port            | R4 output port                          | )(                     | )(                     | ) (          | I                  | )(                     | )(                      | )(                         |

| 02              | R5 input port            | R5 output port                          | )(                     | )(                     | )(           | 1                  | )(                     | )(                      | )(                         |

| 90              |                          | R6 output port                          | )(                     | )(                     | )(           | ı                  | )(                     | )(                      | )(                         |

| 07              |                          | R7 output port                          | )(                     | )(                     | )(           | ı                  | )(                     | )(                      | )                          |

| 80              | R8 input port            | R8 output port                          | 0                      | ) (<br>                | ) (          | ì                  | )(                     | )(                      | ı                          |

| 60              | R9 input port            | R9 output port                          | 0                      | )                      | )<br>        | 1                  | )                      | )                       | ı                          |

| 9<br>8          |                          |                                         | 1                      | ı                      | ı            | 1                  | 1                      | ı                       | ı                          |

| 80              |                          |                                         | I                      | 1                      | ı            | ı                  | i                      | ı                       | I                          |

| 9               |                          |                                         | 1                      | 1                      | ı            | ı                  | ı                      | ı                       | i                          |

| 8               |                          |                                         | ı                      | 1                      | 1            | ı                  | ı                      | ۱ (                     | ı                          |

| 96              | Status register (Note 3) |                                         | 0                      | 1                      | 1            | 1                  | ı                      | )                       | i                          |

| JO.             | Serial receive buffer    | Serial transmit buffer                  | 0                      | 0                      | 0            | _                  | 1                      | 1                       | I                          |

| 10 <sup>H</sup> | Undefined                | Hold operating mode control             | ı                      | 0                      | l            | ı                  | 1                      | ı                       | ı                          |

| =               | Undefined                |                                         | 1                      | ı                      | ı            | ı                  | 1                      | 1                       | ı                          |

| 12              | Undefined                | ĺ                                       | 1                      | ì                      | ١            | ı                  | i                      | ı                       | ı                          |

| 13              | Undefined                |                                         | ı                      | ı                      | ı            | 1                  | I                      | ı                       | 1                          |

| 14              | Undefined                |                                         | ı                      | 1 (                    | ı            | ı                  | ı                      | 1                       | ı                          |

| 15              | Undefined                | Watchdog Timer control                  | ı                      | 0                      | ı            | ı                  | ı                      | l                       | ı                          |

| 16              | Undefined                | System clock control                    | ı                      | 0                      | 1            | 1                  | I                      | ı                       | 1                          |

| 17              | Undefined                |                                         | 1                      | ı                      | ı            | ı                  | i                      | ı                       | ı                          |

| 8               | Undefined                |                                         | 1                      | ı                      | 1            | ı                  | 1                      | ł                       | ı                          |

| 19              | Undefined                | Interval Timer interrupt control        | ı                      | 0                      | 1            | ı                  | 1                      | ı                       | ı                          |

| 4               | Undefined                | 1                                       | 1                      | ı                      | 1            | ı                  | ı                      | ı                       | 1                          |

| <b>8</b> 2      | Undefined                |                                         | I                      | 1                      | 1            | i                  | ı                      | 1                       | ı                          |

| ¥               | Undefined                | Timer/Counter 1 control                 | I                      | 0'                     | ı            | ı                  | i                      | ı                       | ı                          |

| 0               | Undefined                | Timer/Counter 2 control                 | ı                      | 0                      | ı            | ı                  | ı                      | ı                       | I                          |

| 2               | Undefined                | Serial interface control 1              | 1                      | 0                      | i            | ı                  | ı                      | ı                       | ı                          |

| 1F              | Undefined                | Serial interface control 2              | _                      | 0                      | 1            | -                  | ı                      | ı                       | -                          |

| ];              | - + - + -                | 2 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 |                        |                        |              |                    |                        |                         |                            |

-"means the reseved state. Unavilable for the user programs. Note 1.

The 5-bit to 8-bit data conversion instruction [OUTB @HL], automatic access to ports P1 and P2. The status input of serial interface, clock generator, and  $\overline{\text{HOLD}}$  ( $\overline{\text{KE0}}$ ) pin. Note 2. Note 3.

Table 3-1. Port address Assignments and Available I/O Instructions

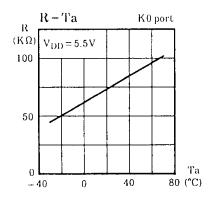

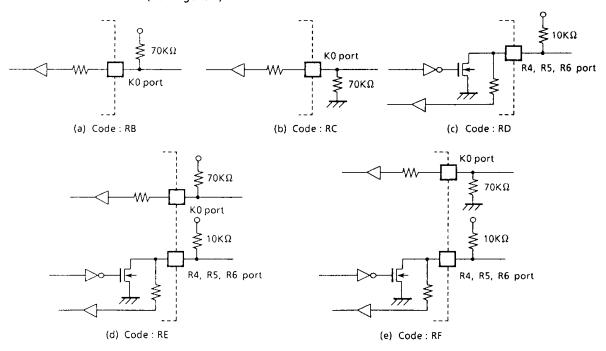

## (1) Port K0 (K03 - K00)

Port K0 is a 4-bit input-only port. A pull-up or pull-down resistor can be contained by the mask option.

Figure 3-1. Port K0

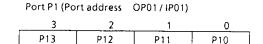

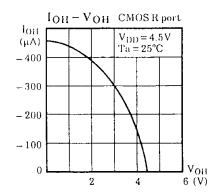

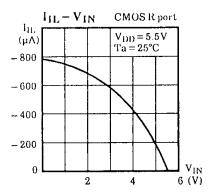

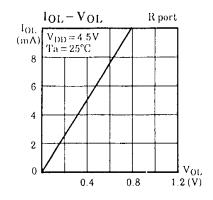

### (2) Ports P1 (P13 - P10) and P2 (P23 - P20)

Ports P1 and P2 are 4-bit high current output ports which can directly drive LEDs, with 4-bit latches. When an input instruction is executed, the latch data is read in these ports. The latch is initialized to "1" during reset. They can be accessed separately at port addresses OP01/IP01 and OP02/IP02. Additionally,8-bit data can be set to these ports (the upper 4 bits to port P2, the lower 4 bits to port P1) by using the 5-bit to 8-bit data conversion instruction [OUTB @HL].

Example 1: To output immediate value "5" to port P1.

> OUT #5, %OP01 ; Port P1←5

Example 2: To read the latch data from port P2 to store it in the accumulator

IN %IP02, A ; Acc←Port P2

Example 3: To read, from ROM, the 8-bit data corresponding to the 5 bits obtained by linking

the content (1 bit) of the carry flag with the contents (4 bits) of at address 90H in

RAM to output the 8-bit data to ports P2 and P1.

LD HL, #90H ; HL←90<sub>H</sub> (Sets the RAM address) OUTB @HL ; Port P2, P1←ROM data

Port P2 (Port address OP02 / IP02) P23 P22 P21

P20

Figure 3-2. Ports P1, P2

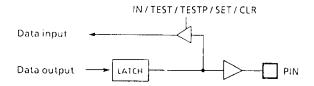

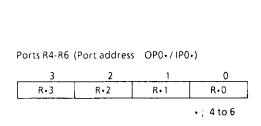

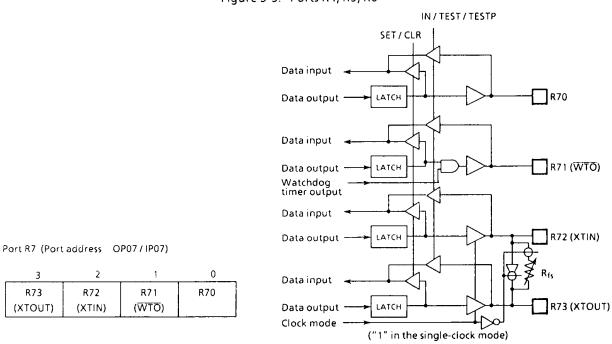

## (3) Ports R4 (R43 - R40), R5 (R53 - R50), R6 (R63 - R60), R7 (R73 - R70)

These ports are 4-bit I/O ports with a latch. When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset.

These 4 ports (16 pins) can be set, cleared, and tested for each bit as specified by L register indirect addressing bit manipulation instructions [SET @L], [CLR @L], and [TEST @L]. Table 3-2 lists the pins (I/O ports) that correspond to the L register contents.

Example: To clear R43 pin as specified by the L register indirect addressing bit manipulation instruction.

LD L, #0011B ; Set R43 pin address to L register

CLR @L ; R43←0

|   |   | Lireg | iste | Pin |     |

|---|---|-------|------|-----|-----|

|   | 3 | 2     | 1    | 0   | FIR |

|   | 0 | 0     | 0    | 0   | R40 |

|   | 0 | 0     | 0    | 1   | R41 |

| 1 | 0 | 0     | 1    | 0   | R42 |

|   | 0 | 0     | 1    | 1   | R43 |

|   | Lre | giste | r | Pin  |  |  |

|---|-----|-------|---|------|--|--|

| 3 | . 2 | 1     | 0 | PI(I |  |  |

| 0 | 1   | 0     | 0 | R50  |  |  |

| 0 | 1   | 0     | 1 | R51  |  |  |

| 0 | 1   | 1     | 0 | R52  |  |  |

| 0 | 1   | 1     | 1 | R53  |  |  |

| L register |   |   |   | Pin  |

|------------|---|---|---|------|

| 3          | 2 | 1 | 0 | rii) |

| 1          | 0 | 0 | 0 | R60  |

| 1          | 0 | 0 | 1 | R61  |

| 1          | 0 | 1 | 0 | R62  |

| 1          | 0 | 1 | 1 | R63  |

|   |   | Lreg | jiste | Pin |      |

|---|---|------|-------|-----|------|

| l | 3 | 2    | 1     | , 0 | riii |

| ı | 1 | 1    | 0     | 0   | R70  |

|   | 1 | 1    | 0     | 1   | R71  |

|   | 1 | 1    | 1     | 0   | R72  |

|   | 1 | 1    | 1     | 1   | R73  |

Table 3-2. Relationship between L register contents and I/O port bits

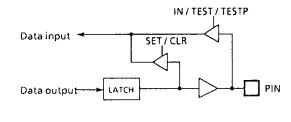

Port R7 is shared by the low-frequency resonator connection pins (XTIN, XTOUT) and the watchdog timer output pin (WTO). For the dual-clock mode operation, the low-frequency resonator(32.768kHz) is connected to R72 (XTIN) and R73 (XTOUT) pins. For the single-clock mode operation, R72 and R73 pins are used for the ordinary I/O ports. When the watchdog timer is used, R71 (WTO) becomes the watchdog timer output pin. The watchdog timer output is the logical AND output with the port R71 output latch. To use the R71 pin for an ordinary I/O port, the watchdog timer must be disabled (with the watchdog timer output set to "1").

Figure 3-3. Ports R4, R5, R6

Figure 3-4. Port R7

#### (4) Port R8 (R83 - R80)

Port R8 is a 4-bit I/O port with a latch. When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset. Port R8 is shared by the external interrupt request input pin and the timer/counter input pin. To use this port for one of these functional pins, the latch should be set to "1". To use it for an ordinary I/O port, the acceptance of external interrupt must be disabled or the event counter/pulse width measurement modes of the timer/counter must be disabled.

Note. When R82 (INT1) pin is used for an I/O port, external interrupt 1 occurs upon detection of the falling edge of pin input, and if the interrupt enable master flip-flop is enabled, the interrupt request is always accepted, so that a dummy interrupt processing must be performed (only the interrupt return instruction [RETI] is executed).

With R80 ( $\overline{\text{INT2}}$ ) pin, external interrupt 2 occurs like R82 but bit 0 of the interrupt enable register is only kept at "0", not accepting the interrupt request.

Figure 3-5. Port R8

#### (5) Port R9 (R92 - R90)

Potr R9 is a 3-bit I/O port with latch. When used as an input, the latch must be set to "1". The latch is initialized to "1" during reset. Port R9 is shared with the serial port.

To use port R9 for the serial port, the latch should be set to "1". To use port R9 for an ordinary I/O port, the serial port must be disabled. Although R93 pin does not exist actually, execution of the set or clear instruction for R93 ([SET %OP09,3] or [CLR %OP09,3]) affects the operation of the internal CPU. Therefore, these instructions should not be execution on R93. However, other instructions may be used, in which an uncertain value is read upon execution of an input instruction.

Figure 3-6. Port R9

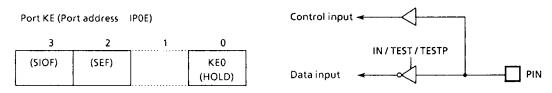

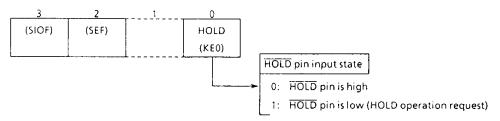

#### (6) Port KE (KEO)

Port KE is a 1-bit sense input port shared by the hold request/release signal input pin (HOLD). This input port is assigned to the least significant bit of port address IPOE and is processed as the data with inverted polarity. For example, if an input instruction is executed with the pin on the high level, "0" is read. Note that KEO pin cannot be used in the dual-clock mode.

Example: To wait until KEO pin goes low.

SWAIT: TEST %IPOE, 0; Waits if  $\overline{\text{KEO}}$  pin = "H".

B SWAIT

Figure 3-7. Port KE

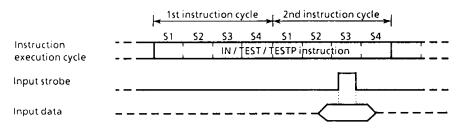

## 3.1.2 I/O Timing

## (1) Input timing

External data is read from an input port or an I/O port in the S3 state of the second instruction cycle during the input instruction (2-cycle instruction) execution. This timing cannot be recognized from the outside, so that the transient input such as chattering must be processed by program.

Figure 3-8. Input Timing

## (2) Output timing

Data is output to an output port or an I/O port in the S4 state of the second instruction cycle during the output instruction (2-cycle instruction) execution.

Figure 3-9. Output Timing

## 3.2 Interval Timer

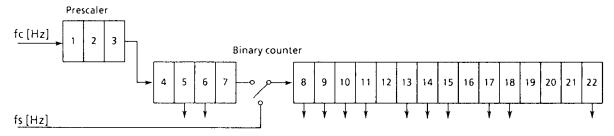

#### 3.2.1 Configuration of Interval Timer

The interval timer consists of a 19-stage binary counter with a divide-by-8 prescaler. The source clock to the interval timer and its input stage depend on the operating mode as shown below. During reset, the binary counter is cleared to "0". However, the prescaler is not cleared.

- ① In the single-clock mode

- The high-frequency clock (fc) is applied to the first stage of the interval timer.

- ② In the dual-clock mode

In this mode, the interval timer is split between stages 7 and 8. The low-frequency clock (fs) is applied to the 8th stage. The high-frequency clock (fc) is applied to the first stage of the interval timer. In the SLOW operating mode, the high-frequency clock oscillator stops, so that the divided outputs of the interval timer stage 1 through 7 also stop.

Figure 3-10. Configuration of Interval Timer

#### 3.2.2 Functions of Interval Timer

The interval timer provides the following functions:

- (i) Generation of instruction cycle

- (2) Generation of an interrupt with a fixed frequency (the interval timer interrupt)

- 3 Generation of internal source clock for timer/counters

- 4 Generation of internal serial clock for a serial interface

- ⑤ Generation of warm-up time at release of the HOLD operating mode

- 6 Generation of source clock for a watchdog timer

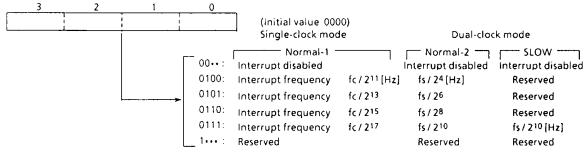

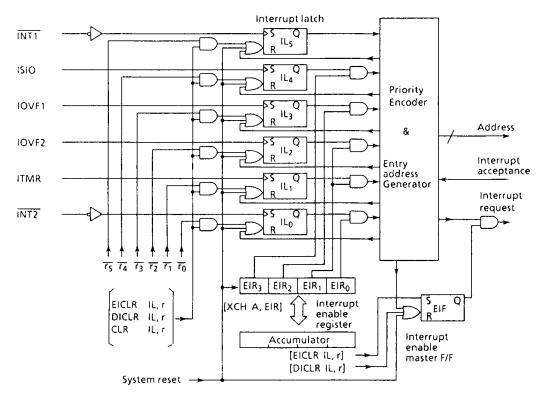

## 3.2.3 Interval Timer Interrupt (ITMR)

The interval timer can be used to generate an interrupt with a fixed frequency. An interval timer interrupt is controlled by the command register (OP19) and is initialized to "0" during reset. An interval timer interrupt is generated at the first rising edge of the binary counter output after the command has been set. The interval timer is not cleared by command, so that the first interrupt may occur earlier than the preset interrupt period.

Example: To set the interval timer interrupt frequency to fc/215[Hz] (Single-clock mode).

LD A, #0110B; OP19+0110<sub>B</sub>

OUT A. %OP19

Interval timer interrupt control command register (Port addres OP19)

Note 1. . ; don't care

Note 2. fc; High-frequency clock [Hz],

fs; Low-frequency clock [Hz]

(a) Command register

| Single-clock mode         | Dual-clock mode     | At fc = 4.194304MHz, fs = 32.768KHz |

|---------------------------|---------------------|-------------------------------------|

| fc / 2 <sup>11</sup> [Hz] | fs/24[Hz]           | 2048 Hz                             |

| fc / 2 <sup>13</sup>      | fs / 2 <sup>6</sup> | 512                                 |

| fc / 215                  | fs / 28             | 128                                 |

| fc / 217                  | fs / 210            | 32                                  |

(b) Example of interrupt frequency

Figure 3-11. Interval Timer Interrupt Control Command Register

## 3.3 Timer/Counters (TC1, TC2)

The 47C800 has two 12-bit timer/counters. RAM addresses are assigned to the count register in unit of 4 bits, permitting the initial value setting and counter reading through the RAM mauipulation instruction. When the timer/counter is not used, the mode selection may be set to "stopped" to use the RAM at the address corresponding to the timer/counter for storing the ordinary user-processed data.

Figure 3-12. Count Registers of the Timer/Counters (TC1, TC2)

#### 3.3.1 Functions of Timer/Counters

The timer/counters provide the following functions:

① Event counter ② Programmable timer ③ Pulse width measurement

## 3.3.2 Control of Timer/Counters

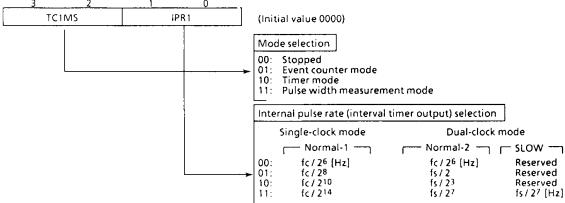

The timer/counters are controlled by the command registers. The command register is accessed as port address OP1C for timer/counter 1, and port address OP1D for timer/counter 2. These registers are initialized to "0" during reset.

Timer/Counter 1 control command register (Port address OP1C)

Timer/Counter 2 control command register (Port address OP1D)

Figure 3-13. Timer/Counter Control Command Register

TOSHIBA TMP47C800/980

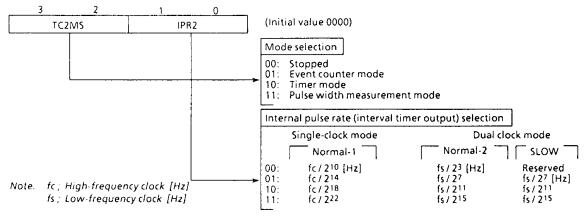

The timer/counter increments at the rising edge of each count pulse. Counting starts with the first rising edge of the count pulse generated after the command has been set. Count operation is performed in one instruction cycle after the current instruction execution, during which the execution of a next instruction and the acceptance of an interrupt are delayed. If counting is requested by both TC1 and TC2 simultaneously, the request by TC1 is preferred. The request from TC2 is accepted in the next instruction cycle. Therefore, during a count operation, the apparent instruction execution speed drops as counting occurs more frequently. The timer/counter causes an interrupt upon occurrence of an overflow (a transition of the count value from FFF<sub>H</sub> to 000<sub>H</sub>). If the timer/counter is during the interrupt enabled state and the overflow interrupt is accepted immediately after its occurrence, the interrupt is processed in the sequence shown in Figure 3-14. Note that counting continues if there is a count request after overflow occurrence.

Figure 3-14. Timer/Counter Overflow Interrupt Timing

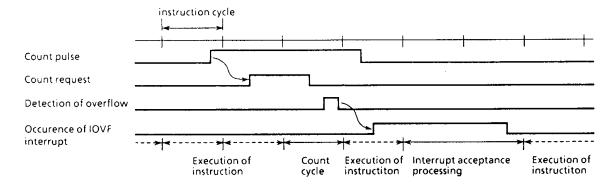

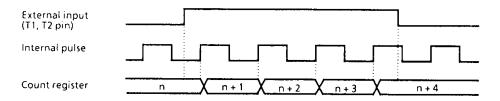

#### (1) Event counter mode

In the event counter mode, the timer/counter increments at each rising edge of the external pin (T1, T2) input. The maximum applied frequency of the external pin input is fc/32 for the 1-channel operation; for the 2-channel operation, the frequency is fc/32 for TC1 and fc/40 for TC2. The apparent instruction execution speed drops most to  $(9/11) \times 100 = 82\%$  when TC1 and TC2 are operated at the maximum applied frequency because the count operation is inserted once every 4 instruction cycles for TC1 and every 5 instruction cycles for TC2. For example, the instruction execution speed of  $2\mu s$  drops to  $3.6\mu s$ .

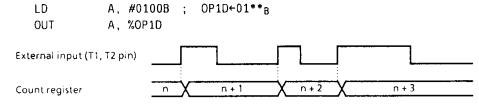

Example: To operate TC2 in the event counter mode.

Figure 3-15. Event Counter Mode Timing Chart

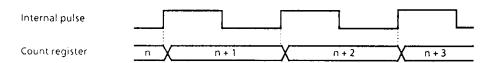

#### (2) Timer mode

In the timer mode, the timer/counter increments as the rising edge of the internal pulse generated from the interval timer. One of 4 internal pulse rates can be selected by the command register. The selected rate can be initially set to the timer/counter to generate an overflow interrupt in order to create a desired time interval.

When an internal pulse rate of fc/210 is used, a count operation is inserted once every 128 instruction cycles, so that the apparent instruction execution speed drops by  $(1/127) \times 100 = 0.8\%$ .

For example, the instruction execution speed of 2µs drops to 2.016µs. In the timer mode, R83 (T1) and R81 (T2) pins provide the ordinary I/O ports.

Example: To generate an overflow interrupt (at fc = 4 MHz) by TC1 after 100 ms.

LD HL,#0F4H ; TC1+E79<sub>H</sub> (Setting of count register) CLR DMB ST #9,@HL+ ST #7.@HL+ ST #0EH.@HL+ LD A,#1010B ; OP1C←1010<sub>B</sub> (Timer mode rate fc/210) OUT A.%OP1C LD A,#0100B ; EIR←0100<sub>8</sub> (Enables interrupt) XCH A.EIR EICLR IL,110111B; EIF←1, IL<sub>3</sub>←0

Figure 3-16. Timer Mode Timing Chart

## Calculating the preset value of the count register

The preset value of the count register is obtained from the following relation  $2^{12}$  – (interrupt setting time)  $\times$  (internal pulse rate)

For example, to generate an overflow interrupt after 100ms at fc = 4MHz with the internal pulse rate of  $fc/2^{10}$ , set the following value to the count register as the preset value:

$$2^{12} - (100 \times 10^{-3}) \times (4 \times 106/210) = 3705 = E79_{H}$$

| Internal pulse rate      | Max. setting time          | At fc = 4.194304MHz |                   |  |

|--------------------------|----------------------------|---------------------|-------------------|--|

|                          |                            | Internal pulse rate | Max. setting time |  |

| fc / 2 <sup>6</sup> [Hz] | 2 <sup>18</sup> / fc [sec] | 65536 [Hz]          | 0.0625 [sec]      |  |

| fc / 28                  | 2 <sup>20</sup> / fc       | 16384               | 0.25              |  |

| fc / 210                 | 2 <sup>2</sup> 2 / fc      | 4096                | 1                 |  |

| fc / 2 <sup>14</sup>     | 2 <sup>26</sup> / fc       | 256                 | 16                |  |

| fc / 218                 | 2 <sup>30</sup> / fc       | 16                  | 256               |  |

| fc / 2 <sup>2</sup> 2    | 234 / fc                   | 1                   | 4096              |  |

Table 3-3. Internal Pulse Rate Selection

#### (3) Pulse width measurement mode

In the pulse width measurement mode, the timer/counter increments with the pulse obtained by sampling the external pins (T1,T2) by the internal pulse. As shown in Figure 3-17 the timer/counter increments only while the external pin input is high. The maximum applied frequency to the external pin input must be one that is enough for analyzing the count value. Normally, a frequency sufficient slower than the internal pulse rate setting is applied to the external pin.

Figure 3-17. Pulse Width Measurement Mode Timing Chart

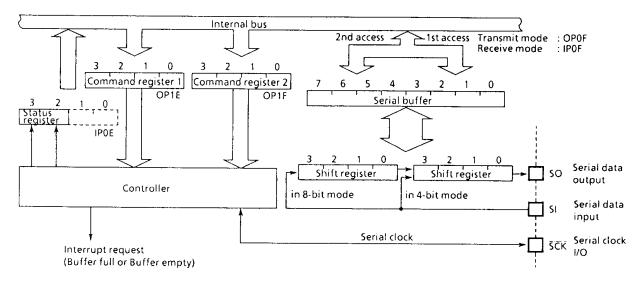

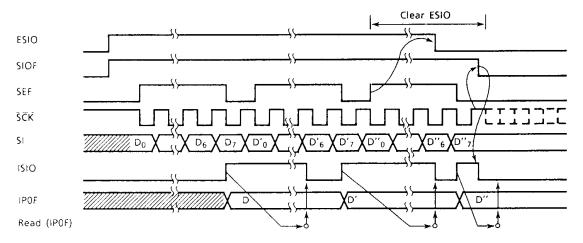

## 3.4 Serial Interface (SIO)

The 47C800 contains a serial interface with an 8-bit buffer. The serial interface is connected to the exterenal device via 3 pins (the serial port): R92 (SCK), R91 (SO), and R90 (SI). The serial port is shared by port R9. For the serial port, the output latch of port R9 must be set to "1". In the transmit mode, R90 pin provides the I/O port; in the receive mode, R91 pin provides the I/O port.

## 3.4.1 Configuration of Serial Interface

Figure 3-18. Configuration of Serial Interface

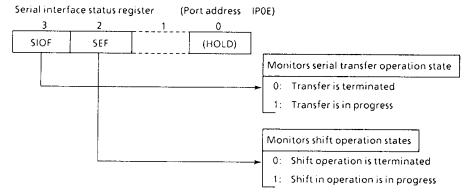

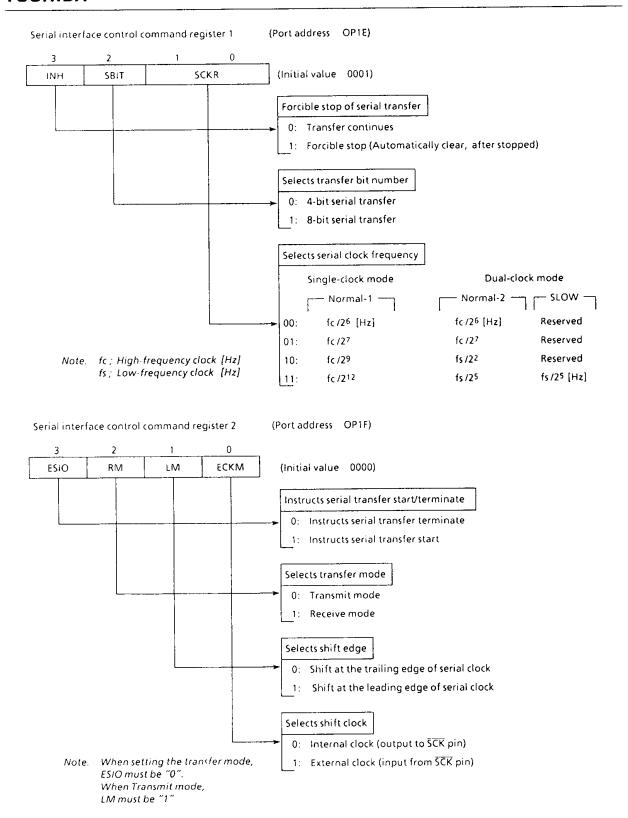

## 3.4.2 Control of Serial Interface

The serial interface is controlled by command registers (OP1E, OP1F). The operating states of the serial interface can be monitored by the status register (IP0E).

Figure 3-19. Serial Interface Status Register

TMP47C800/980

Figure 3-20. Serial Interface Control Command Register

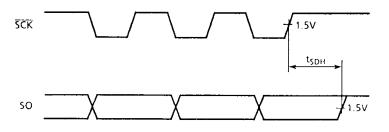

#### (1) Serial clock

For the serial clock, one of the following can be selected according to the contents of the command register:

#### a. Clock source selection

#### ① Internal clock

The serial clock frequency is selected by command register. The serial clock is output on the  $\overline{SCK}$  pin. Note that the start of transfer, the  $\overline{SCK}$  pin output goes high. This device provides the wait function in which the shift is not occurred until these processings are completed. The highest transfer rate based on the internal clock is 93750 bits/second (at fc = 6 MHz).

#### (2) External clock

The signal obtained by the clock supplied to the SCK pin from the outside is used for the serial clock. In this case, the output latch of R92 (SCK) must be set to "1" beforehand. For the shift operation to be performed correctly, each of the serial clock's high and low levels needs 2 instruction cycles or more to be completed.

#### b. Shift edge selection

Leading edge

Data is shifted at the leading edge (the falling edge of SCK pin input) of the serial clock.

② Trailing edge

Data is shifted at the trailing edge (the rising edge of SCK pin input) of the serial clock. However, in the transmit mode, the trailing-edge shift is not supported.

#### (2) Transfer bit number

SBIT (bit 2 of the command register 1) can select 4-bit/8-bit serial transfer.

## a. 4-bit serial transfer

In this mode, transmission/reception is performed on 4-bit basis. ISIO interrupt is generated every 4-bit transfer. Transmit/receive data is written/read by accessing the buffer register (OPOF / IPOF) respectively.

## b. 8-bit serial transfer

In this mode, transmission/reception is performed on 8-bit basis. ISIO interrupt is generated every 8-bit transfer.

Transmit/receive data is written/read by accessing the buffer register (OPOF / IPOF) twice. At the first access after setting transfer mode or generating the interrupt request, the write/read operation of lower 4-bit is performed to from the buffer register. At the second access, that of upper 4-bit is performed.

## (3) Transfer modes

Selection between the transmit mode and the receive mode is performed by RM (bit 2 of the command register).

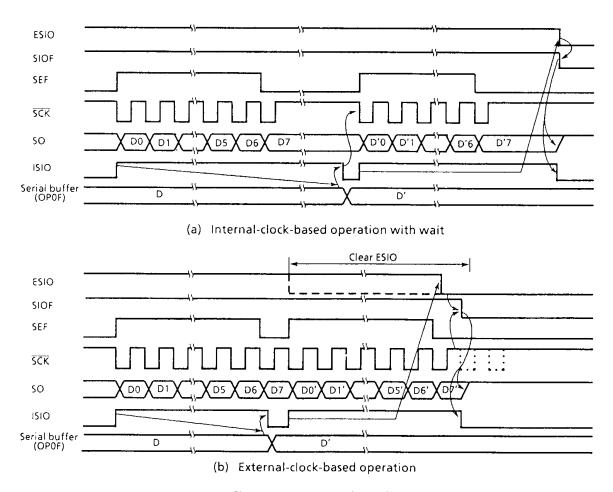

#### a. Transmit mode

The transmit mode is set to the command register then writes the first transmit data (4bits or 8bits) to the buffer register (OPOF). If the transmit mode is not set, the data is not written to the buffer register.

In the 8-bit transfer mode, the 8-bit data is written by accessing the buffer register (OP0F) twice. Then, setting ESIO to "1" starts transmission. The transmit data is output to the SO pin in synchronization with the serial clock from the LSB side sequentially. When the LSB is output, the transmit data is moved from the buffer register to the shift register. When the buffer register becomes empty, the buffer empty interrupt (ISIO) to request for the next transmit data is generated. In the interrupt service program, when the next transmit data is written to the buffer register, the interrupt request is reset.

In the operation based on the internal clock, if no more data is set after the transmission of the 4-bit or 8-bit data, the serial clock is stopped and the wait state sets in. In the operation based on the external clock, the data must be set in the buffer register by the time the next data shift operation starts.

Therefore, the transfer rate is determined by the maximum delay time between the occurrence of the interrupt request and the writing of data to the buffer register by the interrupt serviced program.'

To end transmission, ESIO is cleared to "0" instead of writing the next transmit data by the buffer empty interrupt service program. When ESIO is cleared, transmission stops upon termination of the currently shifted-out data.

The transmission end can be known by the SIOF state (SIOF goes "0" upon transmission end). In the operation based on the external clock, ESIO must be cleared to "0" before the next transmit data is shifted out. If ESIO is not cleared before, the transmission stops upon sending the next 4-bit or 8-bit data (dummy).

Example : To transmit (8-bit serial transfer) data stored in data memory (its address is specified by the HL register pair and the DMB) in synchronization with the internal clock (fc/27).

| _ | , - |                                                                                                     |

|---|-----|-----------------------------------------------------------------------------------------------------|

|   | LD  | , #0101B ; OP1E←0101 <sub>B</sub> (Sets the 8-bit serial transfer)                                  |

|   | OUT | N, %OP1E                                                                                            |

|   | LD  | , #0010B ; OP1F←0010 <sub>B</sub> (Sets the transmit mode of the operation based on internal clock) |

|   | OUT | A, %OP1F                                                                                            |

|   | OUT | OPOF←RAM[HL] (Writes the transmit data of lower 4-bits)                                             |

|   | INC | -                                                                                                   |

|   | OUT | PHL, %OPOF ; OPOF←RAM[HL] (Writes the transmit data of upper 4-bits)                                |

|   | LD  | i, #1010B ; ESIO←1 (Instructs transmission start)                                                   |

|   | OUT | A, %OP1F                                                                                            |

|   |     |                                                                                                     |

Figure 3-21. Transmit Mode

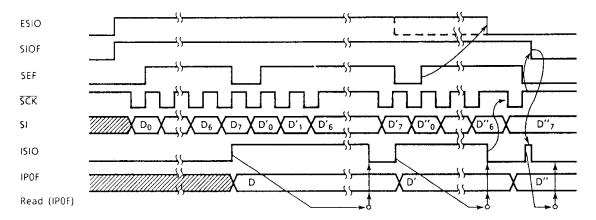

## b. Receive mode

Data can be received when ESIO is set to "1" after setting the receive mode to the command register. The data is put from the SI pin to the shift register in synchronization with the serial clock. Then the 4/8-bit data is transferred from the shift register to the buffer register (IPOF), upon which the buffer full interrupt (ISIO) to request for reading received data is generated. The receive data is read from the buffer register by the interrup service program. In the 8-bit transfer mode, the received data is read after an interrupt request occurs: the lower 4 bits are read by the first access and the upper 4 bits by the next access. When the data has been read, the interrupt request is reset and the next data is put in the shift register to be transferred to the buffer register.

In the operation based on the internal clock, if the previous receive data has not been read from the buffer register at the end of capturing the next data, the serial clock is stopped and the wait operation is performed until the data has been read.

In the operation based on the external clock, the shift operation is performed in synchronization with the externally-supplied clock, so that the data must be read from the buffer register before the next receive data is transferred to it. The maximum transfer rate in the external-clock-based operation is determined by the maximum delay time between the generation of interrupt request and the reading of receive data. In the receive mode, the shift operation may be performed at either the leading edge or the trailing edge. In the leading edge shift operation,data is captured at the leading edge of the serial clock, so that the first shift data must be put in the SI pin before the first serial clock is applied at the start of transfer.

Example: To instruct the receive start operation with the 8-bit serial transfer, internal clock and leading edge shift (with the interrupt enable register already set).

A, #0100B ; OP1E←0100<sub>B</sub> (Sets the 8-bit serial transfer) LD A, %OP1E OUT 1 D A. #0110B ; OP1F←0110<sub>B</sub> (Sets the receive mode) OUT %0P1F ; EIF←1 (Enables interrupt) ΕI ; ESIO←1 (Instructs reception start) LD A, #1110B OUT A. %OP1F

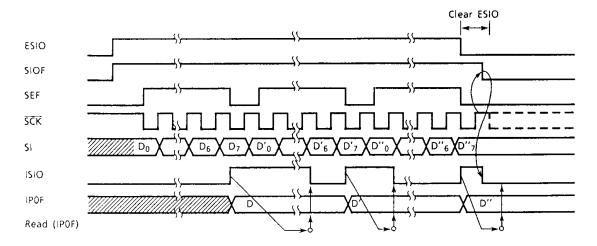

To end the receive operation, ESIO must be cleared to "0". When ESIO is cleared, the completion of the transfer of the current 4-bit or 8-bit data to the buffer register terminates the receive operation. To confirm the end of the receive operation by program, SIOF (bit 3 of the status register) must be sensed. SIOF goes "0" at the end of receive operation.

If the transfer modes are changed, the contents of the buffer register are lost. Therefore, the modes should not be changed until the last received data is read even after the end of reception is instructed (by clearing ESIO to "0").

The receive operation can be terminated in one of the following approaches determined by the transfer rate:

(1) When the transfer rate is sufficiently low (the external-clock-based operation)

If ESIO can be cleared to "0" before the next serial clock is applied upon occurrence of buffer full interrupt in the external-clock-based operation, ESIO is cleared to "0" by the interrupt service program, then the last received data is read.

Example: To instruct the receive end with sufficient low transfee rate (the leading edge shift).

LD A, #0111B ; ESIO←0 (Instructs reception end)

OUT A, %OP1F

IN %IP0F, A ; Acc←IP0F (Reads received data)

When the transfer rate is sufficiently high (the external/internal clock-based operation) If the transfer rate is high and, therefore, it is possible that the capture of the next data starts before ESIO is cleared to "0" upon acceptance of any interrupt, ESIO must be cleared to "0" by confirming that SEF (bit 2 of the status register) is set at reading the data proceeding the last data. Then, the data is read. In the interrupt serevicing following the reception of the last data, no operation is needed for termination; only the reading of the received data is performed.

This method is generally employed for the internal-clock-based operations. For an external-clock-based operation, ESIO must be cleared and the received data must be read before the last data is transferred to the buffer register.

Example: To instruct reception end when transfer rate is high (the internal clock, leading-edge shift).

## 3 One-word reception

When receiving only 1 word, ESIO is set to "1" then it is cleared to "0" after confirming that SEF has gone "1". In this case, buffer full interrupt is caused only once, so that the received data is read by the interrupt service program.

Example: To instruct the start/end of 1-word reception (the internal clock, the trailing edge shift).

|        | euge siiriy. |           |                                                                  |

|--------|--------------|-----------|------------------------------------------------------------------|

|        | LD           | A, #0100B | ; OP1F $\leftarrow$ 0100 <sub>B</sub> (Sets in the receive mode) |

|        | OUT          | A, %OP1F  |                                                                  |

|        | ΕI           |           | ; EIF←1 (Enables interrupt)                                      |

|        | LD           | A, #1110B | ; ESIO←1 (Instructs reception start)                             |

|        | OUT          | A, %OP1F  |                                                                  |

| SSEFO: | TEST         | %IP0E, 2  | ; Confirms that SEF = "1"                                        |

|        | В            | SSEF0     |                                                                  |

|        | LD           | A, #0110B | ; ESIO←0 (Instructs reception end)                               |

|        | OUT          | A, %OP1F  |                                                                  |

|        |              |           |                                                                  |

### (4) Stopping serial transfer

A serial transfer operation can be stopped forcibly.