Datacom

Edition 2001-06-29

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 7/26/01. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

TE3-MUX M13 Multiplexer and DS3 Framer PEB 3445 E V2.1

Datacom

#### PEB 3445 E

| Revision I                                | History: 2001-06-29                                                                                                                           | DS3                                                           |  |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|--|

| Previous V                                | ersion: Preliminary Data Sheet 09.2000                                                                                                        |                                                               |  |  |  |  |  |  |  |

| Page                                      | Subjects (major changes since last revision)                                                                                                  |                                                               |  |  |  |  |  |  |  |

|                                           | Changed document to new documentation guidelines                                                                                              | cument to new documentation guidelines.                       |  |  |  |  |  |  |  |

| 21                                        | Recommendation for demultiplexed bus operation add                                                                                            | ded to signal LALE.                                           |  |  |  |  |  |  |  |

| 55                                        | Added table content which was missing in previous ve                                                                                          | ersion.                                                       |  |  |  |  |  |  |  |

| 64f., 66f.<br>185ff.,                     | Figure 16, Figure 17, Figure 18, Figure 19 corrected LBLE were wrong in previous version.  Timings of LBHE in Figure 24 and Figure 25 redrawn |                                                               |  |  |  |  |  |  |  |

| 188ff.                                    | Merged timings for LA and LBHE.  Timings of LBLE in Figure 28 and Figure 29 redrawn Merged timings of LA and LBLE.                            | . Figure 31 added.                                            |  |  |  |  |  |  |  |

| 84, 139                                   | Description of register bits SIDLE, SAISA, RDC extended.                                                                                      |                                                               |  |  |  |  |  |  |  |

| 91, 101,<br>113, 118,<br>127, 151,<br>154 | Description of register bits OD, XBIT, GN, RES, T1E1                                                                                          | corrected.                                                    |  |  |  |  |  |  |  |

| 167, 179                                  | Major parts of register description (FHND and PHND) Register FHND: Bits ABORT and XTF removed. Register PHND: Bit XTF removed.                | rewritten.                                                    |  |  |  |  |  |  |  |

| 177                                       | Removed register bit XRA.                                                                                                                     |                                                               |  |  |  |  |  |  |  |

| 191                                       | Section 'DMA Interface Signals' added.                                                                                                        |                                                               |  |  |  |  |  |  |  |

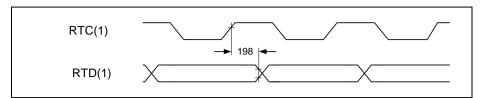

| 204                                       | RTD is updated with rising edge of RTC. This is corre                                                                                         | ated with rising edge of RTC. This is corrected in Figure 49. |  |  |  |  |  |  |  |

|                                           | Some minor documentation updates (wording, syntax                                                                                             | ·,).                                                          |  |  |  |  |  |  |  |

|                                           | Name change M13FX -> TE3-MUX. Removed PEF volume Table 27 "DS1/E1 Receive Data Timing" on Page 2                                              |                                                               |  |  |  |  |  |  |  |

|                                           | Changed figure 25 and 27. Removed timing 35 101,111,151,152,195,198. Changed table 11.                                                        | 5. Changed timings                                            |  |  |  |  |  |  |  |

|                                           | Changed FEAC FHND register to contain XTF bit.                                                                                                |                                                               |  |  |  |  |  |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| 1<br>1.1<br>1.1.1<br>1.1.2<br>1.1.3<br>1.2      | TE3-MUX Overview General Features  M23 Multiplexer and DS3 Framer  M12 Multiplexer and DS2 Framer  Bit Error Rate Tester  Logic Symbol  Typical Applications             | 13<br>14<br>14<br>14<br>16 |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6     | Pin Description Pin Diagram Pin Definitions and Functions Local Microprocessor Interface Serial Interface Test interface Power Supply, Reserved Pins and No-connect Pins | 18<br>19<br>20<br>23<br>29 |

| <b>3</b><br>3.1<br>3.2                          | General Overview  Block Diagram  Block Description                                                                                                                       | 31                         |

| <b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.2<br>4.3 | Functional Description  Remote and Local Loops  Local Loops  Remote Loops  B3ZS Code  Tributary Mapper                                                                   | 34<br>34<br>34<br>36       |

| 4.4<br>4.4.1<br>4.4.1.1<br>4.4.1.2<br>4.4.1.3   | M12 Multiplexer/Demultiplexer and DS2 framer M12 multiplex format Synchronization Procedure Multiplexer/Demultiplexer Loopback Control                                   | 40<br>40<br>41<br>41       |

| 4.4.1.4<br>4.4.2<br>4.4.2.1<br>4.4.2.2          | Alarm Indication Signal ITU-T G.747 format Synchronization Procedure Multiplexer/Demultiplexer                                                                           | 42<br>43<br>43<br>43       |

| 4.4.2.3<br>4.4.2.4<br>4.4.2.5<br>4.5<br>4.5.1   | Parity Bit  Remote Alarm Indication  Alarm Indication Signal  M23 multiplexer and DS3 framer  M23 multiplex format                                                       | 44<br>44<br>45             |

| 4.5.1.1<br>4.5.1.2<br>4.5.1.3<br>4.5.1.4        | M23 multiplex format Synchronization Procedure Multiplexer/Demultiplexer X-bit Alarm Indication Signal, Idle Signal                                                      | 46<br>46<br>46             |

| 4.5.1.5         | Loss of Signal                                    | 47 |

|-----------------|---------------------------------------------------|----|

| 4.5.1.6         | Performance Monitor                               | 47 |

| 4.5.2           | C-bit parity format                               | 48 |

| 4.5.2.1         | Synchronization Procedure                         |    |

| 4.5.2.2         | Multiplexer/Demultiplexer                         |    |

| 4.5.2.3         | X-bit                                             |    |

| 4.5.2.4         | Far End Alarm and Control Channel                 |    |

| 4.5.2.5         | Loopback Control                                  |    |

| 4.5.2.6         | Alarm Indication Signal, Idle Signal              |    |

| 4.5.2.7         | Loss of Signal                                    |    |

| 4.5.2.8         | Performance Monitor                               | 51 |

| 4.5.3           | Full Payload Rate Format                          | 52 |

| 4.6             | Signalling Controller                             |    |

| 4.6.1           | C-bit Parity Path Maintenance Data Link Channel   |    |

| 4.6.2           | Far End Alarm And Control Channel (BOM)           |    |

| 4.6.3           | Signalling controller FIFO operation              |    |

| 4.6.3.1         | Interrupt Driven Microprocessor Operation         |    |

| 4.6.3.2         | DMA Supported Data Transmission                   |    |

| 4.7             | Test Unit                                         |    |

| 4.8             | Interrupt Interface                               | 62 |

| 5               | Interface Description                             | 63 |

| <b>5</b><br>5.1 | Local Microprocessor Interface                    | 63 |

| 5.1.1           | Intel Mode                                        |    |

| 5.1.2           | Motorola Mode                                     |    |

| 5.2             | Serial Interface Timing                           |    |

| 5.2.1           | DS3 Interface                                     |    |

| 5.2.2           | DS1/E1 Interface/DS3 System Interface             |    |

| 5.2.2.1         | DS1/E1 Interface                                  |    |

| 5.2.2.2         | DS3 System Interface                              |    |

| 5.3             | JTAG Interface                                    |    |

| 0.0             |                                                   |    |

| 6               | Reset and Initialization procedure                |    |

| 6.1             | Chip Initialization                               |    |

| 6.2             | Mode Initialization                               | 72 |

| 7               | Register Description                              | 73 |

| 7.1             | Register Overview                                 |    |

| 7.2             | Detailed Register Description                     |    |

| 7.2.1           | DS3 Control and Status Registers                  |    |

| 7.2.2           | DS2 Control and Status Registers                  |    |

| 7.2.3           | Test Unit Registers                               |    |

| 7.2.4           | Test Unit Framer Registers                        |    |

| 7.2.5           | Far End Alarm and Control Channel (BOM) Registers |    |

|                 |                                                   |    |

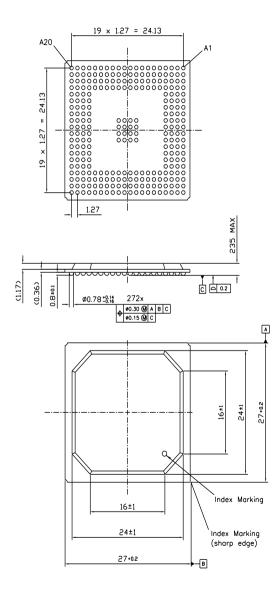

| 9       | Package Outline                         |

|---------|-----------------------------------------|

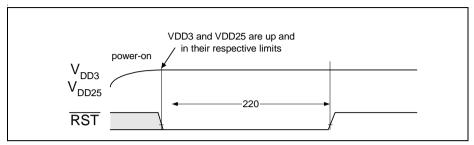

| 8.4.5   | Reset Timing                            |

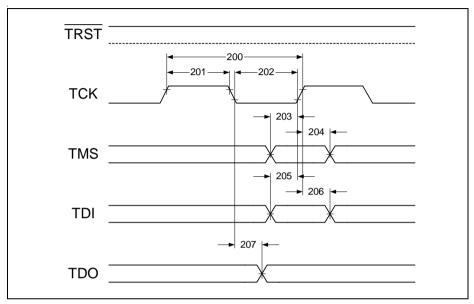

| 8.4.4   | JTAG Interface Timing                   |

| 8.4.3.5 | DS3 System Interface Timing             |

| 8.4.3.4 | DS1/E1 Interface Timing                 |

| 8.4.3.3 | Stuff Bit Timing                        |

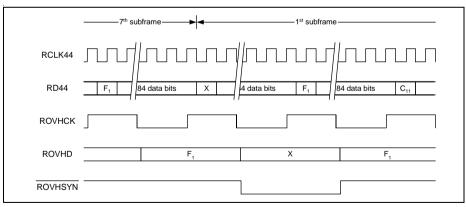

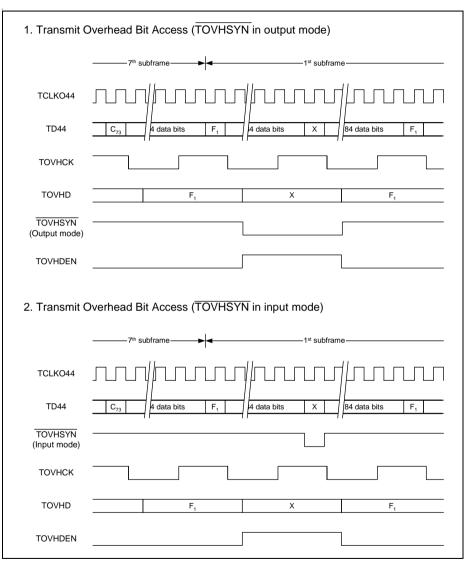

| 8.4.3.2 | Overhead Bit Timing                     |

| 8.4.3.1 | DS3 Serial Interface Timing             |

| 8.4.3   | Serial Interface Timing                 |

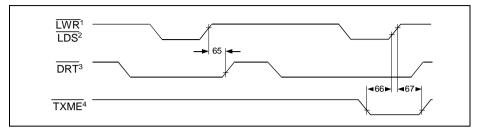

| 8.4.2.2 | DMA Transmit Timing                     |

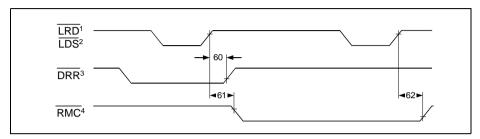

| 8.4.2.1 | DMA Receive Timing                      |

| 8.4.2   | DMA Interface Signals                   |

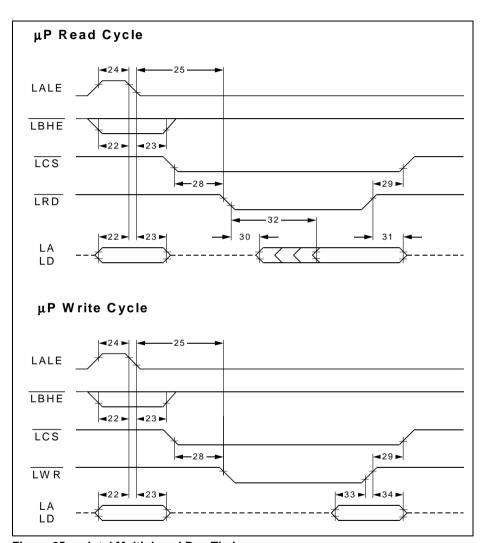

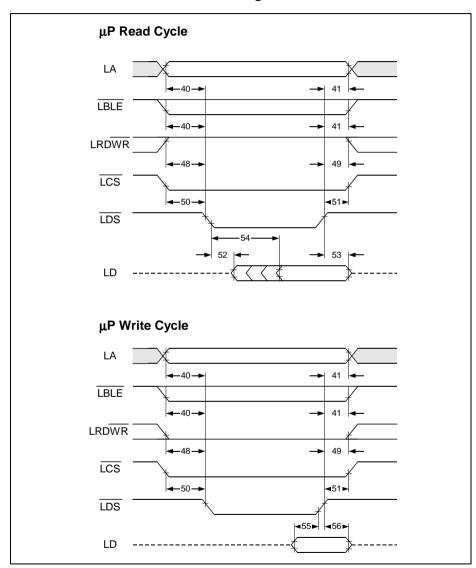

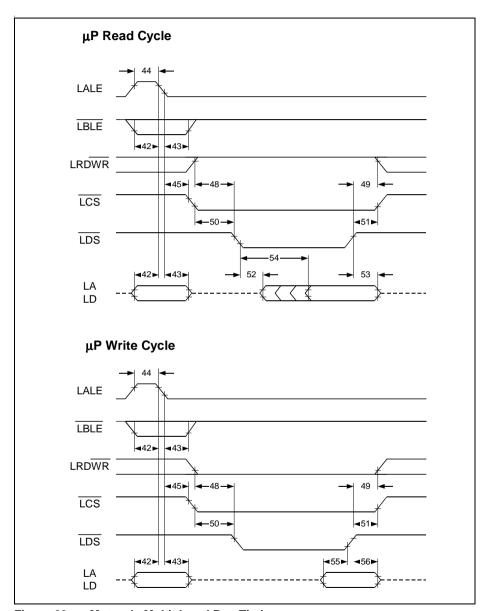

| 8.4.1.2 | Motorola Bus Interface Timing           |

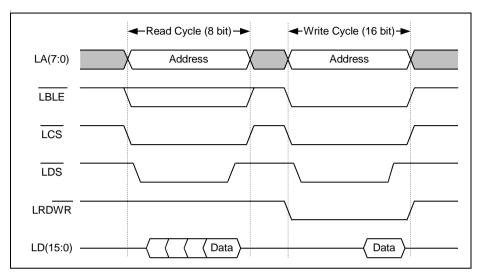

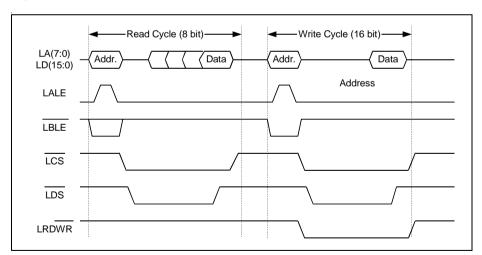

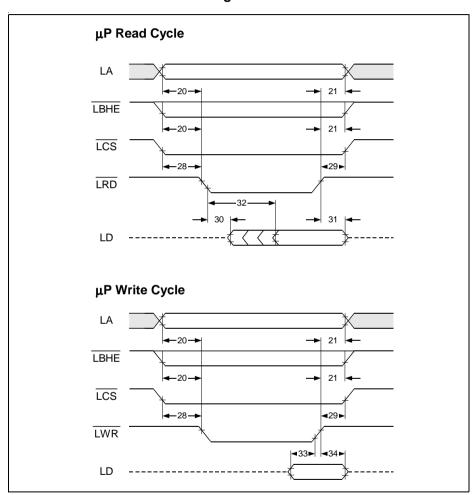

| 8.4.1.1 | Intel Bus Interface Timing              |

| 8.4.1   | Local Microprocessor Interface Timing   |

| 8.4     | AC Characteristics                      |

| 8.3     | DC Characteristics                      |

| 8.2     | Absolute Maximum Ratings                |

| 8.1     | Important Electrical Requirements       |

| 8       | Electrical Characteristics              |

| 7.2.6   | C-Bit Path Maintenance (HDLC) Registers |

|         |                                         |

| List of Figu | ures                                                        | Page      |

|--------------|-------------------------------------------------------------|-----------|

| Figure 1     | Logic Symbol                                                | 16        |

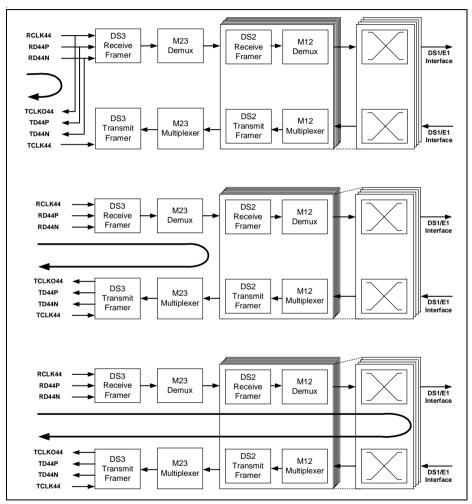

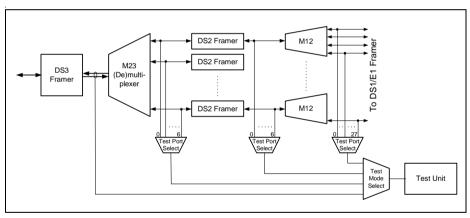

| Figure 2     | Typical DS3 Channelized Application                         |           |

| Figure 3     | Pin Configuration                                           | 18        |

| Figure 4     | Block Diagram                                               |           |

| Figure 5     | Local Loops                                                 | 34        |

| Figure 6     | Remote Loops                                                | 35        |

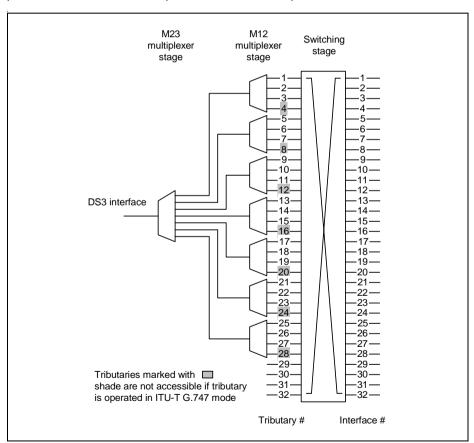

| Figure 7     | Tributary Mapper                                            | 37        |

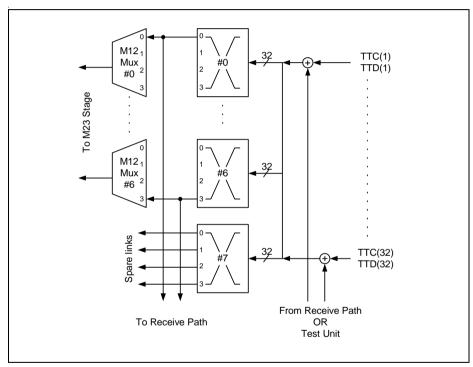

| Figure 8     | Tributary Mapper (Transmit Direction)                       | 38        |

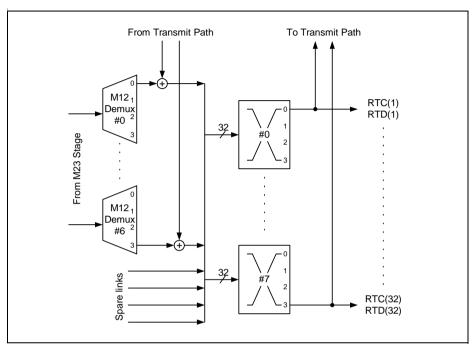

| Figure 9     | Tributary Mapper (Receive Direction)                        | 39        |

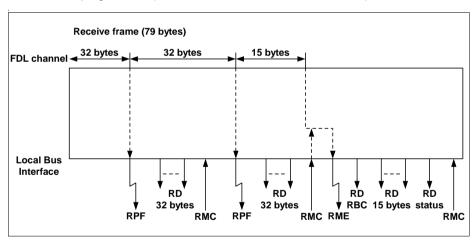

| Figure 10    | Interrupt Driven Reception Sequence Example (32-byte Receiv | e Thresh- |

|              | old) 56                                                     |           |

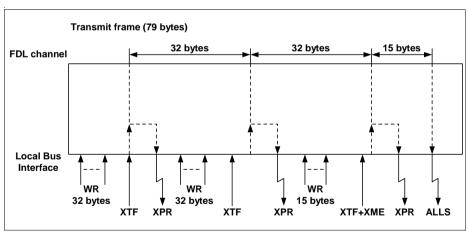

| Figure 11    | Interrupt Driven Transmit Sequence Example                  | 57        |

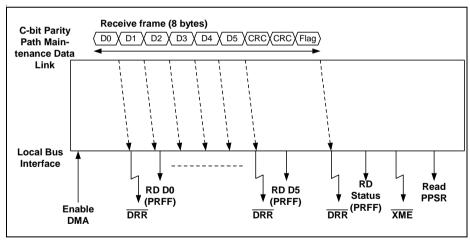

| Figure 12    | DMA Supported Receive Sequence                              |           |

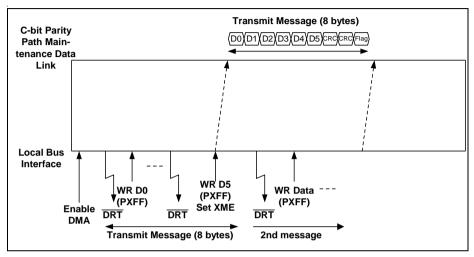

| Figure 13    | DMA supported Transmit Sequence                             | 59        |

| Figure 14    | Test Unit Access Points                                     | 60        |

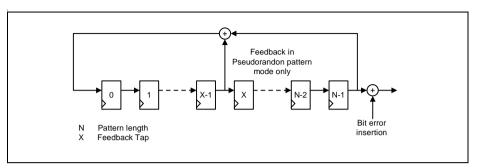

| Figure 15    | Pattern Generator                                           | 61        |

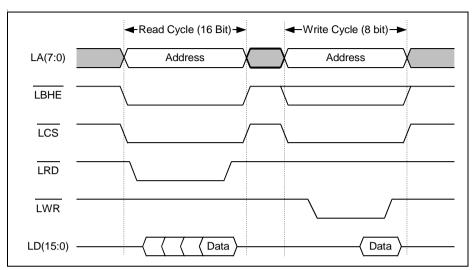

| Figure 16    | Intel Bus Mode (Demultiplexed Bus Operation)                |           |

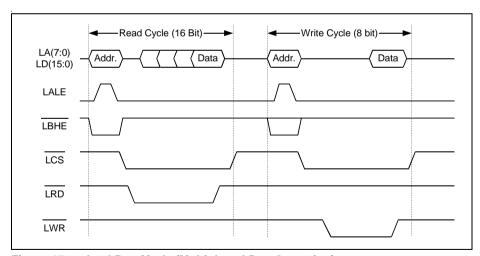

| Figure 17    | Intel Bus Mode (Multiplexed Bus Operation)                  |           |

| Figure 18    | Motorola Bus Mode (Demultiplexed Bus Operation)             |           |

| Figure 19    | Motorola Bus Mode (Multiplexed Bus Operation)               |           |

| Figure 20    | Receive Overhead Access                                     |           |

| Figure 21    | Transmit Overhead Access                                    |           |

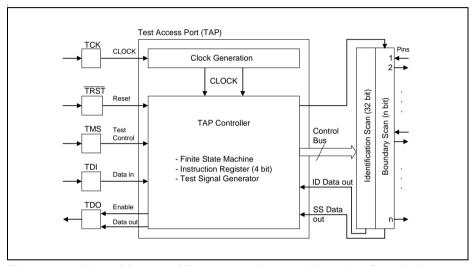

| Figure 22    | Block Diagram of Test Access Port and Boundary Scan Unit    | 70        |

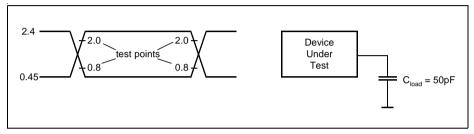

| Figure 23    | Input/Output Waveform for AC Tests                          |           |

| Figure 24    | Intel Demultiplexed Bus Timing                              | 185       |

| Figure 25    | Intel Multiplexed Bus Timing                                |           |

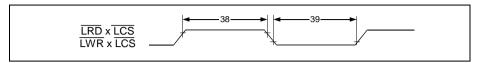

| Figure 26    | Read, Write Control Interval in Demultiplexed Bus Mode      |           |

| Figure 27    | Read, Write Control Interval in Multiplexed Bus Mode        |           |

| Figure 28    | Motorola Demultiplexed Bus Timing                           |           |

| Figure 29    | Motorola Multiplexed Bus Timing                             |           |

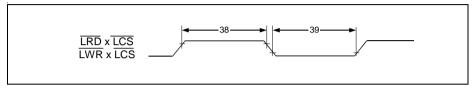

| Figure 30    | Read, Write Control Interval in Demultiplexed Bus Mode      |           |

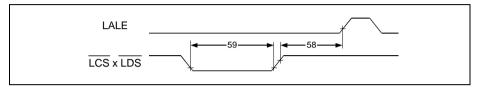

| Figure 31    | Read, Write, ALE Control Interval in Multiplexed Bus Mode   |           |

| Figure 32    | DMA Receive Timing                                          |           |

| Figure 33    | DMA Transmit Timing                                         |           |

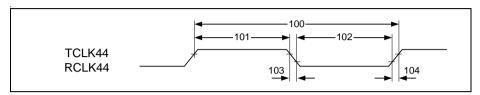

| Figure 34    | Clock Input Timing                                          |           |

| Figure 35    | DS3 Transmit Cycle Timing                                   |           |

| Figure 36    | DS3 Transmit Data Timing                                    |           |

| Figure 37    | DS3 Receive Cycle Timing                                    |           |

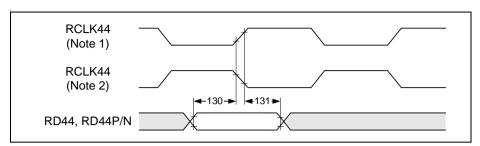

| Figure 38    | DS3 Transmit Overhead Timing                                |           |

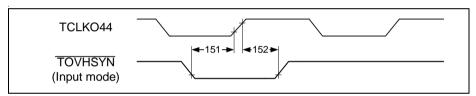

| Figure 39    | DS3 Transmit Overhead Synchronization Timing                |           |

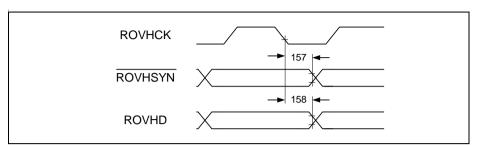

| Figure 40    | DS3 Receive Overhead Timing                                 |           |

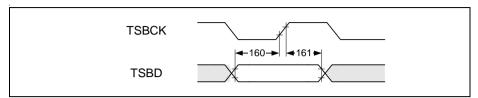

| Figure 41    | DS3 Transmit Stuff Bit Timing                               | 198       |

#### **PEB 3445 E**

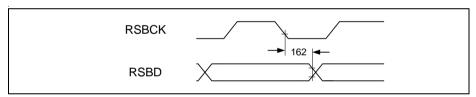

| Figure 42 | DS3 Receive Stuff Bit Timing    | 198 |

|-----------|---------------------------------|-----|

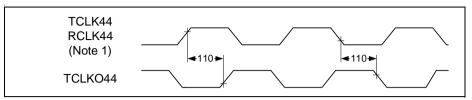

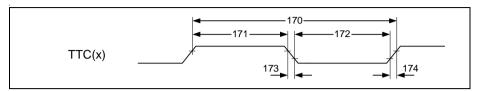

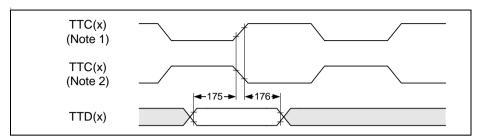

| Figure 43 | DS1/E1 Transmit Clock Timing    | 199 |

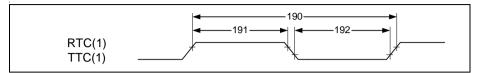

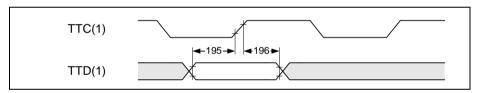

| Figure 44 | DS1/E1 Transmit Data Timing     | 200 |

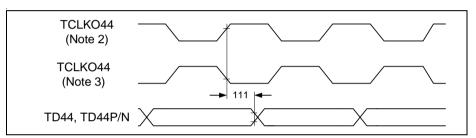

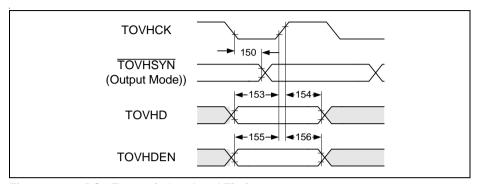

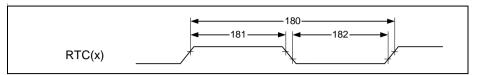

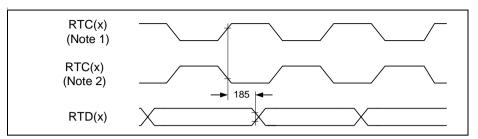

| Figure 45 | DS1/E1 Receive Clock Timing     | 201 |

| Figure 46 | DS1/E1 Receive Data Timing      | 202 |

| Figure 47 | DS3 System Clock Timing         | 203 |

| Figure 48 | DS3 System Transmit Data Timing | 203 |

| Figure 49 | DS3 System Receive Data Timing  | 204 |

| Figure 50 | JTAG Interface Timing           | 205 |

| Figure 51 | Reset Timing                    | 206 |

| List of Tab | les                                         | Page |

|-------------|---------------------------------------------|------|

| Table 1     | M12 multiplex format                        | 40   |

| Table 2     | ITU-T G.747 format                          | 43   |

| Table 3     | M23 multiplex format                        | 45   |

| Table 4     | C-bit parity format                         | 48   |

| Table 5     | Data Bus Access 16-bit Intel Mode           | 63   |

| Table 6     | Data Bus Access 16-bit Motorola Mode        | 65   |

| Table 7     | Register Overview                           |      |

| Table 8     | Far End Alarm and Control Transmit Commands | 169  |

| Table 9     | Path Maintenance Transmit Commands          | 180  |

| Table 10    | Absolute Maximum Ratings                    | 182  |

| Table 11    | DC Characteristics                          | 183  |

| Table 12    | DC Characteristics                          | 183  |

| Table 13    | Intel Bus Interface Timing                  | 187  |

| Table 14    | Motorola Bus Interface Timing               | 190  |

| Table 15    | DMA Receive Timing                          | 191  |

| Table 16    | DMA Transmit Timing                         | 192  |

| Table 17    | Clock Input Timing                          | 193  |

| Table 18    | DS3 Transmit Cycle Timing                   | 194  |

| Table 19    | DS3 Receive Cycle Timing                    | 195  |

| Table 20    | DS3 Transmit Overhead Timing                | 196  |

| Table 21    | DS3 Receive Overhead Timing                 | 197  |

| Table 22    | DS3 Transmit Stuff Timing                   | 198  |

| Table 23    | DS3 Receive Stuff Bit Timing                | 198  |

| Table 24    | DS1/E1 Transmit Clock Timing                | 199  |

| Table 25    | DS1/E1 Transmit Data Timing                 | 200  |

| Table 26    | DS1/E1 Receive Clock Timing                 | 201  |

| Table 27    | DS1/E1 Receive Data Timing                  | 202  |

| Table 28    | DS3 System Clock Timing                     | 203  |

| Table 29    | DS3 System Transmit Data Timing             | 203  |

| Table 30    | DS3 System Receive Data Timing              | 204  |

| Table 31    | JTAG Interface Timing                       | 205  |

| Table 32    | Reset Timing                                | 206  |

# M13 Multiplexer and DS3 Framer TE3-MUX

**PEB 3445 E**

V2.1

#### 1 TE3-MUX Overview

The TE3-MUX integrates a DS3 framer, with a M13 multiplexer, a tributary interchanger/ line selector and 32 serial line interfaces for DS1/E1/J1 lines with 4:28 line protection capability. It is an economical solution for applications, which require DS3 framing but no DS1/E1 framers. This is often required in a Central office where DS1/E1 from different equipment are multiplexed in a card. The TE3-MUX allows the DS1/E1 to be aggregated into DS3 without investing in the framers. Line and remote loopback capabilities can be used to trouble shoot in case of broken connections and other failures. The use of standard line interfaces to interconnect office equipment is called Office Repeater Bay (ORB) compliance.

#### 1.1 General Features

- Integrates a M13 multiplexer and a DS3 framer operating in M13 or C-bit parity mode

- Optionally the M13 multiplexer can be disabled, which provides an integrated solution for combined channelized/unchannelized DS3 applications

- Provides 32 tributary interfaces where each interface can be switched to any of the 28DS1/21E1 tributaries of the DS3 signal

- Integrates a bit error rate tester

- Integrates a 16-/8-bit switchable Intel or Motorola style microprocessor interface which operates in multiplexed or demultiplexed bus mode

- JTAG boundary scan according to IEEE1149.1 (5 pins).

- 0.25 µm, 2.5V low power core technology

- I/Os are 3.3V tolerant and have 3.3V driving capability

- Package P-BGA-272-1 (27mm x 27mm; pitch 1.27mm)

- Full scan path and BIST of on-chip RAMs for production test

- Power consumption: 340mW (typical)

- Temperature range -40..+85°C

#### 1.1.1 M23 Multiplexer and DS3 Framer

- Multiplexing/demultiplexing of seven DS2 into/from M13 asynchronous format according to ANSI T1.107, ANSI T1.107a

- Multiplexing/demultiplexing of seven DS2 into/from C-bit parity format according to ANSI T1.107. ITU-T G.704

- DS3 framing according to ANSI T1.107, T1.107a, ITU-T G.704

- Support of B3ZS encoded signals

- Provides access to the DS3 overhead bits and the DS3 stuffing bits via a serial clock and data interface (overhead interface)

- Insertion and Extraction of alarms according to ANSI T1.404 (remote alarm, AIS, far end receive failure)

- Supports HDLC (Path Maintenance Data Link) and bit oriented message mode (Far End Alarm and Control Channel) in C-bit parity mode. An integrated signalling controller provides 2x32 byte deep FIFO's for each direction of both channels.

- Detection of AIS and idle signal in presence of BER 10<sup>-3</sup>

- · Detection of excessive zeroes and LOS

- Alarm and performance monitoring with 16-bit counters for line code violations, excessive zeroes, parity error (P-bit), framing errors (F-bit errors with or without M-bit errors, far end block error (FEBE-bit) and CP-bit errors.

- · Automatic insertion of severely errored frame and AIS defect indication

### 1.1.2 M12 Multiplexer and DS2 Framer

- Multiplexing/Demultiplexing of four asynchronous DS1 bit streams into/from M13 asynchronous format

- Multiplexing/Demultiplexing of 3 E1 signals into/from ITU G.747 compliant DS2 signal.

- DS2 line loopback detection/generation

- Framing according to ANSI T1.107, T1.107a or ITU-T G.747

- · Insertion and extraction of X-bit

- Insertion and Extraction of alarms (remote alarm, AIS)

- Detection of AIS in presence of BER 10<sup>-3</sup>

- Alarm and performance monitoring (framing bit errors, parity errors)

- Reframe time below 7ms (TR-TSY-000009) for DS2 format and below 1 ms for ITU G.747 format

- Bit Stuffing/Destuffing in M12 multiplex format or C-bit parity format

- Insertion of AIS in lieu of low speed tributaries

#### 1.1.3 Bit Error Rate Tester

- User specified PRBS or Fixed Pattern with programmable length of 2 to 32 bits and programmable feedback tap (PRBS only)

- Optional Bit Inversion

- · Two error insertion modes: Single or programmable bit rates

- · Optional zero suppression

- · 32-bit counters for errors and received bits

- Programmable bit intervals for receive measurements

- Framed DS3, framed/unframed DS2 or framed/unframed DS1/E1 error insertion

- Additional framing error counters for DS1/E1 error insertion

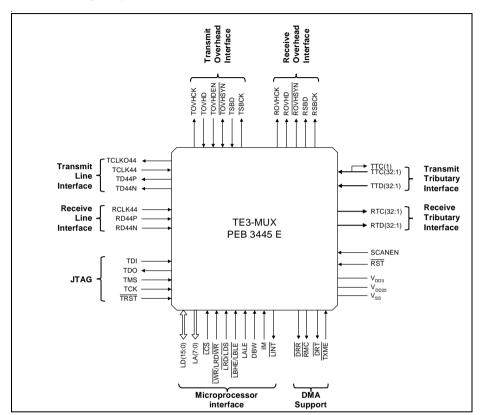

### 1.2 Logic Symbol

Figure 1 Logic Symbol

### 1.3 Typical Applications

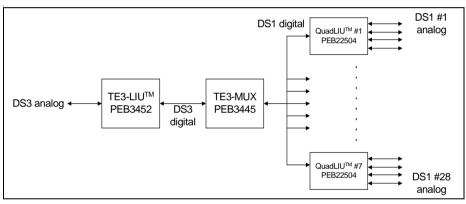

Typical applications for the TE3-MUX support of channelized DS3 with serial line interfaces on the low speed side. The system partitioning due to ORB compliance may allow usage in following systems:

- Terminal Multiplexers with DS1/E1 and HDSL interfaces

- Add Drop Multiplexers (ADM) with DS1/E1 and HDSL interfaces

- Digital Cross Connect devices with DS1/E1 and HDSL interfaces

- · DLC COT and RT

- · Channelized DS3 applications

The TE3-MUX supports 32 low speed serial interfaces. These interfaces can be mapped to any of the 28 DS3 tributaries which provides for 4:28 protection.

Figure 2 Typical DS3 Channelized Application

## 2 Pin Description

### 2.1 Pin Diagram

(top view)

|   | 20           | 19           | 18         | 17      | 16      | 15      | 14      | 13      | 12      | 11            | 10      | 9             | 8       | 7       | 6       | 5       | 4       | 3       | 2       | 1       |

|---|--------------|--------------|------------|---------|---------|---------|---------|---------|---------|---------------|---------|---------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Υ | NC23         | RTD(25)      | VDD25      | TTD(24) | TTD(23) | RTC(22) | TTC(22) | RTC(21) | RTC(20) | RTC(19)       | TTD(19) | RTD(18)       | RTD(17) | TTC(17) | TTD(16) | RTC(15) | RTD(14) | RTC(14) | RTC(13) | NC22    |

| W | RTC(26)      | TTD(26)      | RTC(25)    | RTD(24) | TTC(24) | TTC(23) | TTD(22) | RTD(21) | RTD(20) | RTD(19)       | VDD25   | RTC(18)       | RTC(17) | RTD(16) | TTC(16) | TTD(15) | RTD(13) | TTD(13) | NC21    | TTC(13) |

| ٧ | RTD(27)      | RTD(26)      | TTC(26)    | TTD(25) | RTC(24) | RTD(23) | RTD(22) | VDD25   | TTC(21) | TTC(20)       | TTC(19) | TTD(18)       | TTD(17) | RTC(16) | RTD(15) | TTC(15) | TTC(14) | NC20    | VDD25   | TTD(12) |

| U | VDD25        | TTC(27)      | TTD(27)    | VSS     | TTC(25) | VDD33   | RTC(23) | VSS     | TTD(21) | TTD(20)       | VDD33   | TTC(18)       | VSS     | VDD25   | VDD33   | TTD(14) | VSS     | RTD(12) | TTC(12) | RTC(11) |

| Т | RTC(28)      | TTD(28)      | TTC(28)    | RTC(27) |         |         |         |         |         |               |         |               |         |         |         | RTC(12) | RTD(11) | TTD(11) | RTC(10) |         |

| R | RTC(29)      | TTD(29)      | RTD(28)    | VDD33   |         |         |         |         |         | TE3-          | MUX     |               |         |         |         |         | VDD33   | TTC(11) | TTD(10) | VDD25   |

| Р | TTD(30)      | TTC(30)      | RTD(29)    | TTC(29) |         |         |         |         | F       | PEB 3         | 8445 E  | E             |         |         |         |         | RTD(10) | TTC(10) | RTD(9)  | RTC(9)  |

| N | VDD25        | RTD(30)      | RTC(30)    | VSS     |         |         |         |         |         |               |         |               |         |         | VSS     | TTD(9)  | TTC(9)  | RTD(8)  |         |         |

| М | RTD(31)      | RTC(31)      | TTD(31)    | TTC(31) |         |         |         |         | VSS     | VSS           | vss     | vss           |         |         |         |         | RTC(8)  | TTD(8)  | TTC(8)  | RTD(7)  |

| L | RTC(32)      | TTC(32)      | TTD(32)    | VDD33   |         |         |         |         | VSS     | VSS           | VSS     | VSS           |         |         |         |         | RTC(7)  | TTD(7)  | TTC(7)  | VDD25   |

| K | RTD(32)      | RMC          | TXME       | VDD25   |         |         |         |         | VSS     | VSS           | VSS     | VSS           |         |         |         |         | VDD33   | RTC(6)  | TTD(6)  | RTD(6)  |

| J | LINT         | DRT          | DRR        | IM      |         |         |         |         | vss     | VSS           | VSS     | VSS           |         |         |         |         | TTD(5)  | RTC(5)  | RTD(5)  | TTC(6)  |

| Н | DBW          | ECS          | LRD<br>LDS | vss     |         |         |         |         |         |               |         |               |         |         |         |         | vss     | RTC(4)  | RTD(4)  | TTC(5)  |

| G | LWR<br>LRDWR | LBHE<br>LBLE | VDD25      | LA(1)   |         |         |         |         |         |               |         |               |         |         |         |         | TTD(3)  | VDD25   | TTC(4)  | TTD(4)  |

| F | LALE         | NC19         | LA(2)      | VDD33   |         |         |         |         |         |               |         |               |         |         |         |         | VDD33   | TTC(3)  | RTC(3)  | RTD(3)  |

| Е | LA(0)        | LA(3)        | LA(4)      | LA(7)   |         |         |         |         |         |               |         |               |         |         |         |         | RTC(1)  | TTD(2)  | RTC(2)  | RTD(2)  |

| D | NC18         | LA(5)        | VDD25      | VSS     | RST     | VDD33   | LD(4)   | VSS     | NC17    | VDD33         | NC16    | VDD25         | VSS     | SCANEN  | VDD33   | TSBCK   | VSS     | TTD(1)  | TTC(1)  | TTC(2)  |

| С | LA(6)        | NC15         | NC14       | тск     | LD(1)   | NC13    | LD(7)   | LD(9)   | LD(12)  | VDD25         | TCLKO44 | RCLK44        | NC12    | NC11    | VDD25   | TOVHDEN | ROVHCK  | RSBCK   | VDD25   | RTD(1)  |

| В | NC10         | TDI          | TMS        | TRST    | LD(2)   | LD(5)   | VDD25   | LD(10)  | LD(13)  | LD(15)        | TCLK44  | RD44N         | NC9     | NC8     | NC7     | TOVHCK  | TOVHSYN | ROVHD   | ROVHSYN | NC6     |

| А | NC5          | TDO          | VDD25      | LD(0)   | LD(3)   | LD(6)   | LD(8)   | LD(11)  | LD(14)  | TD44<br>TD44P | TD44N   | RD44<br>RD44P | NC4     | NC3     | NC2     | NC1     | TOVHD   | TSBD    | RSBD    | VSS     |

Figure 3 Pin Configuration

#### 2.2 Pin Definitions and Functions

#### Signal Type Definitions:

I Input is a standard input- only signal.

O Totem Pole Output is a standard active driver.

I/O I/O is a bidirectional, tri-state input/output pin.

**o/d** Open Drain allows multiple devices to share a line as a wire-OR. A pull-

up is required to sustain the inactive state until another agent drives it,

and must be provided by the central resource.

#### **Signal Name Conventions:**

NCn No-connect Pin n

Such pins are not bonded with the silicon. Although any potential at these pins will not impact the device it is recommended to leave them unconnected. No-connect pins might be used for additional functionality in later versions of the device. Leaving them unconnected will guarantee

hardware compatibility to later device versions.

**Reserved** Reserved pins are for vendor specific use only and should be connected

as recommended to guarantee normal operation.

Note: The signal type definition specifies the functional usage of a pin. This does not reflect necessarily the implementation of a pin, e.g. a pin defined of signal type 'Input' may be implemented with a bidirectional pad.

### 2.3 Local Microprocessor Interface

| Pin No.                                                                                       | Symbol   | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-----------------------------------------------------------------------------------------------|----------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D16                                                                                           | RST      | I                       | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| J17                                                                                           | IM       | I                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| H20                                                                                           | DBW      | I                       | Data Bus Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| E17, C20, D19,<br>E18, E19, F18,<br>G17, E20                                                  | LA(7:0)  | I                       | Address bus These input address lines select one of the internal registers for read or write access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| B11, A12, B12,<br>C12, A13, B13,<br>C13, A14, C14,<br>A15, B15, D14,<br>A16, B16, C16,<br>A17 | LD(15:0) | I/O                     | Bota Bus Bidirectional three-state data lines which interface with the system's data bus. Their configuration is controlled by the level of pin DBW:  • 8-bit mode (DBW = 0): LD(7:0) are active. LD(15:8) are in high impedance and have to be connected to V <sub>DD3</sub> or V <sub>SS</sub> .  • 16-bit mode (DBW = 1): LD(15:0) are active. In case of byte transfers, the active half of the bus is determined by LA(0) and LBHE/LBLE and the selected bus interface mode (IM). The unused half is in high impedance. For detailed information, refer to Chapter 5.1. |  |  |  |

| H19                                                                                           | LCS      | I                       | Chip Select This active low signal selects the TE3-MUX for read/write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Pin No. | Symbol           | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F20     | LALE             | I                       | Address Latch Enable The address information provided on address lines LA(7:0) is internally latched with the falling edge of LALE. This function allows the TE3-MUX to be directly connected to a multiplexed address/data bus. In this case, pins LA(7:0) must be externally connected to the data bus pins. When the TE3-MUX is operated in demultiplexed bus mode LALE shall be connected to VDD3. |

| H18     | LRD<br>or<br>LDS | I                       | Read (Intel Bus Mode) This active low signal selects a read transaction. Data strobe (Motorola Bus Mode) This active low signal indicates that valid data has to be placed on the data bus (read cycle) or that valid data has been placed on the data bus (write cycle).                                                                                                                              |

| G20     | or<br>LRDWR      | I                       | Write Enable (Intel Bus Mode) This active low signal selects a write cycle. Read Write Signal (Motorola Bus Mode) This input signal distinguishes write from read operations.                                                                                                                                                                                                                          |

| J20     | LINT             | od                      | Interrupt Request This line indicates general interrupt requests of the TE3-MUX. The interrupt sources can be masked via registers.                                                                                                                                                                                                                                                                    |

| Pin No. | Symbol     | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                     |

|---------|------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G19     | LBHE<br>or | I                       | Byte High Enable (Intel Bus Mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the upper byte LD(15:8) of the data bus. In 8-bit bus interface mode this signal has no function and should be tied to V <sub>DD3</sub> . Refer to Chapter 5.1 for detailed information. |

|         | LBLE       | I                       | Byte Access (Motorola Bus Mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the lower byte LD(7:0) of the data bus. In 8-bit bus interface mode this signal has no function and should be tied to $V_{\rm DD3}$ . Refer to Chapter 5.1 for detailed information.       |

| J18     | DRR        | 0                       | Data Request Receive This signal indicates that the receive FIFO of the path maintenance data link channel contains a byte which has to be read by an external CPU.                                                                                                                                          |

| K19     | RMC        | 0                       | Receive Message Complete This signal indicates that the DMA controller has to read the port status register PPSR in order to release the receive FIFO.                                                                                                                                                       |

| J19     | DRT        | 0                       | Data Request Transmit This signal indicates a request to store a new byte in the transmit FIFO of the path maintenance data link channel.                                                                                                                                                                    |

| K18     | TXME       | I                       | Transmit Message End This signal in combination with DRT indicates that the byte written to the transmit FIFO is the last byte of a HDLC message. TXME has to asserted together with the data signal LD.                                                                                                     |

### 2.4 Serial Interface

| Pin No.       | Symbol          | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                    |  |  |  |  |

|---------------|-----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DS3 Serial In | terface Signals |                         |                                                                                                                                                                                                                             |  |  |  |  |

| B10           | TCLK44          | I                       | DS3 Transmit Clock Input This clock provides a reference clock for the DS3 interface. The frequency of this clock is nominally 44.736 MHz.                                                                                  |  |  |  |  |

| C10           | TCLKO44         | 0                       | DS3 Transmit Clock Output This output is a buffered version of the selected transmit clock. In normal operation mode TCLKO44 is a buffered version of TCLK44. In looped timed mode TCLKO44 is a buffered version of RCLK44. |  |  |  |  |

| A11           | TD44            | 0                       | DS3 Transmit Data This unipolar serial data output represents the DS3 signal. TD44 can be updated on the falling or the rising edge of TCLKO44.                                                                             |  |  |  |  |

|               | TD44P           | 0                       | In dual-rail mode this pin represents the positive pulse of the B3ZS encoded DS3 signal. TD44P can be updated on the falling edge or rising edge of TCLKO44.                                                                |  |  |  |  |

| A10           | TD44N           | 0                       | DS3 Transmit Negative Pulse In dual-rail mode this pin represents the negative pulse of the B3ZS encoded DS3 signal. TD44N can be updated on the falling or rising edge of TCLKO44.                                         |  |  |  |  |

| C9            | RCLK44          | I                       | DS3 Receive Clock Input This pin provides the receive clock input. The frequency of this clock is nominally 44.736 MHz.                                                                                                     |  |  |  |  |

| Pin No.      | Symbol              | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                 |

|--------------|---------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A9           | RD44<br>or<br>RD44P | I                       | DS3 Receive Data This unipolar serial data input represents the DS3 signal. RD44 can be sampled on the falling or rising edge of RCLK44. DS3 Receive Positive Pulse In dual-rail mode this pin represents the positive pulse of the B3ZS encoded DS3 signal. RD44P can be sampled on the |

| B9           | RD44N               | I                       | falling or rising edge of RCLK44.  DS3 Receive Negative Pulse In dual-rail mode this pin represents the negative pulse of the B3ZS encoded DS3 signal. RD44N can be sampled on the falling or rising edge of RCLK44.                                                                     |

| DS3 Overhead | Interface           |                         |                                                                                                                                                                                                                                                                                          |

| B5           | TOVHCK              | 0                       | Transmit Overhead Bit Clock This signal provides the bit clock for the DS3 overhead bits of the outgoing DS3 frame. TOVHCK is nominally a 526 kHz clock.                                                                                                                                 |

| A4           | TOVHD               | I                       | Transmit Overhead Data The overhead bits to be placed in the outgoing DS3 frame can be provided via TOVHD. Transmit overhead data is sampled on the rising edge of TOVHCK and those bits marked by TOVHDEN are inserted in the overhead bit positions of the outgoing DS3 frame.         |

| C5           | TOVHDEN             | I                       | Transmit Overhead Data Enable The asserted TOVHDEN signal marks the bits to be inserted in the DS3 frame. TOVHDEN is sampled together with TOVHD on the rising edge of TOVHD.                                                                                                            |

| Pin No. | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|---------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B4      | TOVHSYN | I/O                     | Transmit Overhead Synchronization TOVHSYN provides the means to align TOVHD to the first M-frame of the DS3 signal or to align the first M-frame to TOVHSYN.  If operated in output mode TOVHSYN is asserted when the X-bit of the 1st subframe of the DS3 multiframe has to be inserted via TOVHD. TOVHSYN is updated on the falling edge of TOVHCK.  If operated in input mode TOVHSYN must be asserted when the X-bit of the 1st M-frame of the DS3 signal is output on TD44. TOVHSYN is sampled on the rising edge of TCLKO44. |

| D5      | TSBCK   | 0                       | Transmit Stuff Bit Clock This signal provides the bit clock for DS3 transmit stuff bit data.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A3      | TSBD    | I                       | Transmit Stuff Bit Data Data provided via TSBD is optionally inserted in the stuffed bit positions of the DS3 signal. TSBD is sampled on the rising edge of TSBCK. This function is available in M13 asynchronous format only.                                                                                                                                                                                                                                                                                                     |

| C4      | ROVHCK  | 0                       | Receive Overhead Bit Clock This signal provides the bit clock for the received DS3 overhead bits. ROVHCK is nominally a 526 kHz clock.                                                                                                                                                                                                                                                                                                                                                                                             |

| B3      | ROVHD   | 0                       | Receive Overhead Data ROVHD contains the extracted overhead bits of the DS3 frame. It is updated on the falling edge of ROVHCK.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin No.                                                                                                                                                                 | Symbol       | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B2                                                                                                                                                                      | ROVHSYN      | 0                       | Receive Overhead Synchronization ROVHSYN is asserted while the X-bit of the 1 <sup>st</sup> subframe of the DS3 signal is provided via ROVHD. It is updated on the falling edge of ROVHCK.                                                                                               |

| C3                                                                                                                                                                      | RSBCK        | 0                       | Receive Stuff Bit Clock This signal provides the bit clock for DS3 receive stuff bit data.                                                                                                                                                                                               |

| A2                                                                                                                                                                      | RSBD         | O                       | Receive Stuff Bit Data ROVHD provides data which was inserted in the stuffed bit positions of the DS3 signal. RSBD is updated on the falling edge of RSBCK. This function is available in M13 asynchronous format only.                                                                  |

| DS1/E1 Interfac                                                                                                                                                         | e Signals, D | S3 System In            | terface Signals                                                                                                                                                                                                                                                                          |

| L20, M19, N18,<br>R20, T20, T17,<br>W20, W18,<br>V16, U14, Y15,<br>Y13, Y12, Y11,<br>W9, W8, V7,<br>Y5, Y3, Y2, T4,<br>U1, T1, P1, M4,<br>L4, K3, J3, H3,<br>F2, E2, E4 | RTC(32:1)    | O                       | DS1/E1 Receive Clock This interface provides the receive clock for each of the low speed interfaces. Dependent on the tributary (DS1/E1) this clock has a nominal frequency of 1.544 MHz or 2.048 MHz. Due to the destuffing and demultiplexing process the receive clock contains gaps. |

| E4                                                                                                                                                                      | RTC(1)       | 0                       | DS3 Receive Clock When the TE3-MUX is operated in unchannelized mode (DS3 framer mode) this interface provides the DS3 receive payload clock. It is derived from the receive clock RCLK44 and has clock gaps on the DS3 bit positions containing the overhead bits.                      |

| Pin No.                                                                                                                                                                 | Symbol    | Input (I)<br>Output (O) | Function                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K20, M20, N19,<br>P18, R18, V20,<br>V19, Y19, W17,<br>V15, V14, W13,<br>W12, W11, Y9,<br>Y8, W7, V6,<br>Y4, W4, U3,<br>T3, P4, P2, N1,<br>M1, K1, J2, H2,<br>F1, E1, C1 | RTD(32:1) | 0                       | DS1/E1 Receive Data The data stream of the DS1/E1 tributary is directly feeded to this output. RTD(x) is updated on the rising or falling edge of RTC(x).                                          |

| C1                                                                                                                                                                      | RTD(1)    | Ο                       | DS3 Receive Data When the TE3-MUX is operated in unchannelized mode (DS3 framer mode) the payload of the incoming DS3 signal is output on RTD(1). RTD(1) is updated on the falling edge of RTC(1). |

| Pin No.                                                                                                                                                                 | Symbol    | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L19, M17, P19, P17, T18, U19, V18, U16, W16, W15, Y14, V12, V11, V10, U9, Y7, W6, V5, V4, W1, U2, R3, P3, N2, M2, L2, J1, H1, G2, F3, D1, D2                            | TTC(32:1) | I                       | DS1/E1 Transmit Clock Transmit data is sampled on the rising edge of TTC(x) and inserted into the assigned DS1/E1 tributary of the DS3 signal. Dependent on the tributary type TTC(x) has a clock frequency of 1.544 MHz or 2.048 MHz.                                  |

| D2                                                                                                                                                                      | TTC(1)    | 0                       | DS3 Transmit Clock When the TE3-MUX is operated in unchannelized mode (DS3 framer mode) this interface provides the DS3 transmit payload clock. It is derived from the transmit clock TCLKO44 and has clock gaps on the DS3 bit positions containing the overhead bits. |

| L18, M18, P20,<br>R19, T19, U18,<br>W19, V17, Y17,<br>Y16, W14,<br>U12, U11, Y10,<br>V9, V8, Y6,<br>W5, U5, W3,<br>V1, T2, R2, N3,<br>M3, L3, K2, J4,<br>G1, G4, E3, D3 | TTD(32:1) | I                       | DS1/E1 Transmit Data TTD(x) provides the DS1/E1 data stream to be inserted in the assigned DS1/E1 tributary of the DS3 signal. TTD(x) can be sampled on the rising or falling edge of TTC(x).                                                                           |

| D3                                                                                                                                                                      | TTD(1)    | I                       | DS3 Transmit Data When the TE3-MUX is operated in unchannelized mode (DS3 framer mode) the payload of the outgoing DS3 signal needs to be provided via TTD(1). TTD(1) is sampled on the rising edge of TTC(1)                                                           |

### 2.5 Test interface

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                             |

|---------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C17     | TCK    | I                       | JTAG Test Clock This pin is connected with an internal pull-up resistor.                                                                                             |

| B18     | TMS    | I                       | JTAG Test Mode Select This pin is connected with an internal pull-up resistor.                                                                                       |

| B19     | TDI    | I                       | JTAG Test Data Input This pin is connected with an internal pull- up resistor.                                                                                       |

| A19     | TDO    | 0                       | JTAG Test Data Output                                                                                                                                                |

| B17     | TRST   | I                       | JTAG Test Reset This pin is connected with an internal pull-up resistor.                                                                                             |

| D7      | SCANEN | I                       | Full Scan Path Test Enable When connected to $V_{\rm DD3}$ the TE3-MUX works in a vendor specific test mode. It is recommended to connect this pin to $V_{\rm SS}$ . |

### 2.6 Power Supply, Reserved Pins and No-connect Pins

| Pin No.                                                                                                                                                         | Symbol              | Input (I)<br>Output (O) | Function                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------|-------------------------------------------------------------------|

| A1, D4, D8,<br>D13, D17, H4,<br>H17, N4, N17,<br>U4, U8, U13,<br>U17, J9, J10,<br>J11, J12, K9,<br>K10, K11, K12,<br>L9, L10, L11,<br>L12, M9, M10,<br>M11, M12 | $V_{\rm SS}$        | I                       | Ground 0V All pins must have the same level.                      |

| A18, B14, C2,<br>C6, C11, D9,<br>D18, G3, G18,<br>K17, L1, N20,<br>R1, U7, U20,<br>V13, V2, W10,<br>Y18                                                         | $V_{\mathrm{DD25}}$ | I                       | Supply Voltage 2.5V ± 0.25V All pins must have the same level.    |

| D6, D11, D15,<br>F4, F17, K4,<br>L17, R4, R17,<br>U6, U10, U15                                                                                                  | $V_{DD3}$           | I                       | Supply Voltage 3.3V ± 0.3V All pins must have the same level.     |

| A5, A6, A7, A8,<br>A20, B1, B6,<br>B7, B8, B20,<br>C7, C8, C15,<br>C18, C19, D10,<br>D12, D20, F19,<br>V3, W2, Y1,<br>Y20                                       | NC123               |                         | No-connect Pins 123  It is recommended not to connect these pins. |

#### **General Overview**

### 3 General Overview

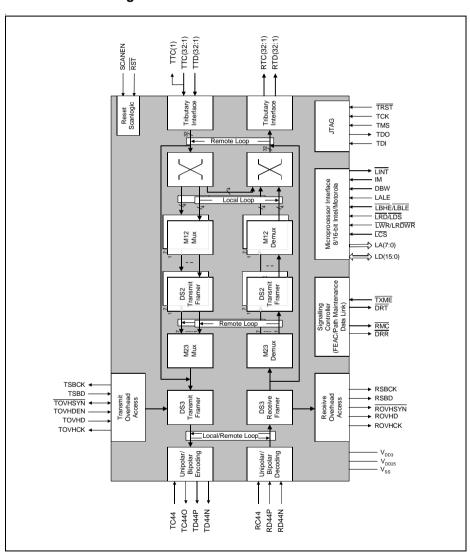

### 3.1 Block Diagram

Figure 4 Block Diagram

**General Overview**

### 3.2 Block Description

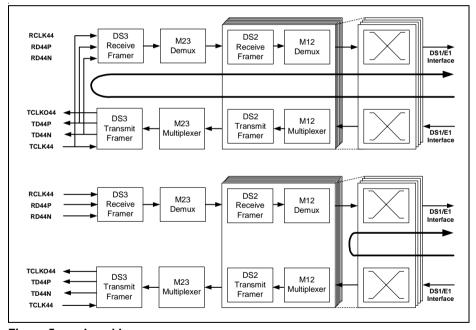

#### 32 port line selector/tributary mapper

This structure allows the user to connect any DS1/E1 signal to a specified tributary of any M12 module. Therefore it maps 32 DS1/E1 signals into 28 DS1 time slots or 21 E1 time slots of the DS3 signal.

The four remaining spare ports can be used for microcontroller based protection, e.g. they can be operated in stand-by mode. They can also be used to interface an external test unit to test any DS1/E1.

#### M12 multiplexer/demultiplexer and DS2 framer

There are seven independent M12 multiplexer/demultiplexer modules in the chip. Each module can operate in either ANSI T1.107, ANSI T1.107a or ITU-T G.747 mode. In other words, a module can either map 4 DS1/J1 to one DS2 or 3 E1 to one DS2. When mapping DS1 signals into DS2 signals the M12 multiplexer performs inversion of the second and fourth DS1 signal. The DS2 framer performs frame and multi-frame alignment in receive direction and vice versa inserts the framing bits according to ANSI T1.107, ANSI T1.107a or ITU-T G.747. It detects loopback requests or enables insertion of loopback requests under microprocessor control.

#### M23 multiplexer/demultiplexer and DS3 framer

In channelized operating mode the M23 multiplexer/demultiplexer maps/demaps seven DS2 signals (generated by the M12 multiplexer/demultiplexer and DS2 framer) into/from M13 asynchronous format or C-bit parity format. In unchannelized mode one logical input stream is mapped into the information bits of the DS3 stream according to ANSI T1.107, ANSI T1.107a. The DS3 framer performs frame and multiframe alignment in receive direction and inserts the frame and multiframe alignment bits. Access to the DS3 overhead bits is provided by an additional overhead interface or via internal registers. An integrated signalling controller supports the Far End Alarm and Control Channel and the C-bit Parity Path Maintenance Data Link in DMA or interrupt mode. Performance monitoring provides counting of framing bit errors, parity errors, CP-bit errors, far end block errors, excessive zeros and line code violations. The framer detects loopback requests and allows insertion of loopbacks under microprocessor control.

#### BERT/PRBS generator/detector

The device has an integrated bit error rate tester. It is a programmable pseudo random bit sequence generator/monitor capable of supporting any smart jack loopback code from 2 to 32 bits in length and with a programmable feedback tap. The monitor can detect the incoming pattern and transmit the same pattern towards the far end of any low speed/high speed port.

#### **General Overview**

The test unit also has single/multi bit error insertion for testing and diagnostics and supports framed DS3, framed/unframed DS2 and framed/unframed DS1/E1 error insertion.

#### **Functional Description**

### 4 Functional Description

#### 4.1 Remote and Local Loops

#### 4.1.1 Local Loops

Local loops are provided on DS3 and DS1 level on a per port/tributary basis. In the local loop the outgoing bit stream of a port/tributary is mirrored to the receive data path. This allows to provide data via the low speed tributaries which is processed by the TE3-MUX in transmit direction, mirrored to the respective receiver and send back to the originating source. In order to ensure that the local port loop works even without incoming receive clock, each line looped uses the corresponding transmit clock.

Figure 5 Local Loops

### 4.1.2 Remote Loops

The TE3-MUX supports remote loops in different stages of the M13 data path. In DS3 line loopback mode the incoming DS3 signal is mirrored and placed on the DS3 signal output. While operating in DS3 line loopback mode, the incoming receive clock RCLK44 is used to update outgoing transmit data. In DS2 line loopback mode one or more

#### **Functional Description**

selectable DS2 signals are looped after the M23 stage the of the TE3-MUX. Finally the DS1/E1 line loopback mode mirrors one or more incoming lines. Tributary data provided via the low speed serial interface is replaced by the mirrored data stream.

Figure 6 Remote Loops

#### **Functional Description**

#### 4.2 B3ZS Code

In the B3ZS line code each block of three consecutive zeros is replaced by either of two replacements codes which are B0V and 00V, where B represents a pulse which applies to the bipolar rule ('+1' or '-1') and V represents a bipolar violation (two consecutive '+1' or '-1' bits). The replacement code is chosen in a way that there is an odd number of valid B pulses between consecutive V pulses to avoid the introduction of a DC component into the analog signal.

The receive line decoder decodes the incoming B3ZS dual rail data signal and changes the replacement patterns to the original three-zeros pattern. Pattern sequences violating these rules are reported as bipolar violation errors.

# 4.3 Tributary Mapper

The tributary mapper connects any of the 28 low speed tributaries to any of the 32 DS1/E1 low speed interfaces. A DS3 tributary consists of seven DS2 tributaries. Each DS2 tributaries consists of four DS1 tributaries when operated in DS1 format or three E1 tributaries when operated in ITU-T G.747 format. When a DS2 tributary is operated in ITU-T G.747 format the first three tributaries of a M12 multiplexer are accessible only. The fourth tributary of that M12 multiplexer is not used.

Mapping of the tributaries to the serial interfaces can be done independently in receive and transmit direction. After reset the tributary mapper maps the tributaries 1..28 to the port interfaces 1..28 and the spare lines 29..32 to the port interfaces 29..32.

Figure 7 Tributary Mapper

### **Transmit Path**

**Figure 8** shows the DS1/E1 transmit part of the TE3-MUX. Each M12 multiplexer is assigned one input switch which maps 4 out of 32 input signals to the four inputs of the M12 multiplexer. The multiplexer as well as the switch to be programmed are selected via D2TSEL.GN. Then the four outputs of the switch are configured using register D2TTM0..3. Additionally each line can be switched into remote loop mode or one selected line can be fed via the integrated bit error rate tester.

Figure 8 Tributary Mapper (Transmit Direction)

#### Receive Path

In receive direction a group of four consecutive output ports is assigned to one output switch (see **Figure 9**). This output switch maps any of the 28 M12 demultiplexer outputs or any of the four internal spare links to its four outputs. The output multiplexer to be programmed is selected via D2RSEL.GN. Then the four outputs of the switch are programmed via D2RTM0..3.

Figure 9 Tributary Mapper (Receive Direction)

# 4.4 M12 Multiplexer/Demultiplexer and DS2 framer

The M12 multiplexer and the DS2 framer can be operated in two modes:

- M12 multiplex format according to ANSI T1.107

- ITU-T G.747 format

# 4.4.1 M12 multiplex format

The framing structure of the M12 signal is shown in **Table 1**. A DS2 multiframe consists of four subframes. Each subframe combines 6 blocks with 49 bits each. The first bit of each block contains an overhead (OH) bit and 48 information bits. The 48 information bits are formed by bit-by-bit interleaving of the four DS1 signals or a total of 12 bits from each DS1 signal. The first bit is assigned to the 1<sup>st</sup> tributary DS1 signal, the second bit is assigned to the 2<sup>nd</sup> tributary DS1 signal and so on.

Table 1 M12 multiplex format

|            | Subframe |       | Block 1 through 6 of a subframe |                 |      |       |      |                 |      |                 |      |                |      |

|------------|----------|-------|---------------------------------|-----------------|------|-------|------|-----------------|------|-----------------|------|----------------|------|

|            |          |       | 1                               | 2               | 2    | ;     | 3    | 4               | 4    | ;               | 5    |                | 6    |

|            | 1        | $M_0$ | [48]                            | C <sub>11</sub> | [48] | $F_0$ | [48] | C <sub>12</sub> | [48] | C <sub>13</sub> | [48] | F <sub>1</sub> | [48] |

| DS2-       | 2        | $M_1$ | [48]                            | C <sub>21</sub> | [48] | $F_0$ | [48] | C <sub>22</sub> | [48] | C <sub>23</sub> | [48] | F <sub>1</sub> | [48] |

| Multiframe | 3        | $M_1$ | [48]                            | C <sub>31</sub> | [48] | $F_0$ | [48] | C <sub>32</sub> | [48] | C <sub>33</sub> | [48] | F <sub>1</sub> | [48] |

|            | 4        | Χ     | [48]                            | C <sub>41</sub> | [48] | $F_0$ | [48] | C <sub>42</sub> | [48] | C <sub>43</sub> | [48] | F <sub>1</sub> | [48] |

## $M_0, M_1$

$\rm M_0$  and  $\rm M_1$  form the multiframe alignment signal. Each DS2 multiframe consists of three M-bits and they are located in bit 0 of subframe one through three. The multiframe alignment signal is '011'.

Χ

This bit is the fourth bit of the multiframe alignment signal and can be set to either '0' or '1'. It is accessible via an internal register.

#### $F_0, F_1$

$F_0$  and  $F_1$  form the frame alignment pattern. Each DS2 multiframe consists of eight F-bits, two per subframe in block 3 and 6.  $F_0$  and  $F_1$  form the pattern '01'. This pattern is repeated in every subframe.

## C<sub>11</sub>..C<sub>43</sub>

The C-bits control the bit stuffing procedure of the multiplexed DS1 signals.

#### [48]

These bits represent a data block, which consists of 48 bits. [48] consists of four time slots of 12 bit and each time slot is assigned to one of four participating DS1 signals.

# 4.4.1.1 Synchronization Procedure

The integrated DS2 framer searches for the frame alignment pattern '01' and the multiframe alignment pattern in each of the seven DS2 frames which are contained in a DS3 signal. Frame alignment is declared, when the DS2 framer has found the basic frame alignment pattern (F-bit) and the multiframe alignment pattern (M-bit).

Loss of frame is declared, when 2 out of 4 or 3 out of 5 incorrect F-bits are found or when one or more incorrect M-bits are found in 3 out of 4 subframes.

# 4.4.1.2 Multiplexer/Demultiplexer

## Demultiplexer

The demultiplexer extracts four DS1 signals out of each DS2 signal. If two out of three bits of C<sub>i1</sub>, C<sub>i2</sub>, C<sub>i3</sub> are set to '1' the first information bit in the i<sup>th</sup> subframe and the 6<sup>th</sup> block which is assigned to the i<sup>th</sup> DS1 signal is discarded.

The demultiplexer performs inversion of the 2<sup>nd</sup> and 4<sup>th</sup> tributary DS1 signal.

## Multiplexer

The multiplexer combines four DS1 signals to form a DS2 signal. Stuffing bits are inserted and the  $C_{i1}$ -,  $C_{i2}$ -,  $C_{i3}$ -bits, which are assigned to the i<sup>th</sup> DS1 signal, are set to '1' in case that not enough data is available.

The  $2^{\text{nd}}$  and  $4^{\text{th}}$  DS1 signal are automatically inverted in transmit direction.

# 4.4.1.3 Loopback Control

#### Detection

Loopback requests encoded in the C-bits of the DS2 signal are flagged when they are repeated for at least five DS2 multiframes. Loops must be initiated by an external microprocessor.

### Generation

A loopback request, which is transmitted in lieu of the C-bits, can be placed in each DS2 signal.

# 4.4.1.4 Alarm Indication Signal

#### Detection

AIS is declared, when the AIS condition (the received DS2 data stream contains an all '1' signal with less then 3/9 zeros within 3156 bits while the DS2 framer is out of frame) is present within a time interval that is determined by register D2RAP.

### Generation

The alarm indication signal is an all '1' unframed signal and will be transmitted if enabled.

### 4.4.2 ITU-T G.747 format

The multiplexing frame structure is shown in **Table 2**.

Table 2 ITU-T G.747 format

|                | Set | Content                                            | Bit       |

|----------------|-----|----------------------------------------------------|-----------|

|                | I   | Frame Alignment Signal 111010000                   | 1 to 9    |

|                |     | Bits from tributaries                              | 10 to 168 |

|                | II  | Alarm indication to the remote multiplex equipment | 1         |