2

### 64KX4 Bit CMOS VIDEO RAM

#### **FEATURES**

- Dual Port Architecture 64K x 4 bits RAM port 256 × 4 bits SAM port

- · Performance range:

| item                                   | - 10  | - 12  |

|----------------------------------------|-------|-------|

| RAM access time (t <sub>RAC</sub> )    | 100ns | 120ns |

| RAM access time (t <sub>CAC</sub> )    | 25ns  | 30ns  |

| RAM cycle time (t <sub>RC</sub> )      | 180ns | 220ns |

| RAM Page mode cycle (t <sub>PC</sub> ) | 60ns  | 75 ns |

| SAM access time                        | 25ns  | 35ns  |

| SAM cycle time                         | 30ns  | 40ns  |

| RAM active current                     | 65mA  | 55mA  |

| SAM active current                     | 40mA  | 35mA  |

| RAM & SAM standby                      | 3mA   | 3mA   |

- Fast Page Mode

- . RAM Read. Write. Read-Modify-Write

- Serial Read and Serial Write

- Read Transfer and Write Transfer

- Real Time Read Transfer capability

- . Write per Bit masking on RAM write cycles

- . CAS-before RAS, RAS-only and Hidden Refresh

- . Common data I/O using three-state RAM output control

- · All inputs and outputs TTL compatible

- · Refresh: 256 cycles/4ms

- Single +5V ± 10% supply voltage.

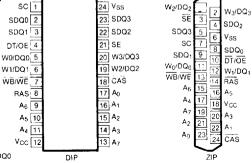

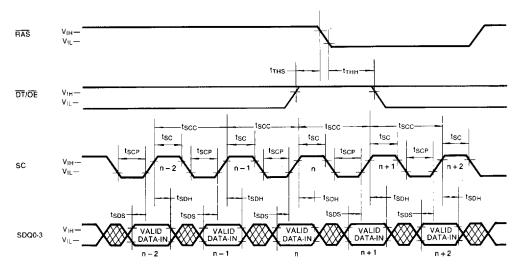

- Plastic 24-pin 400 mil ZIP or DIP.

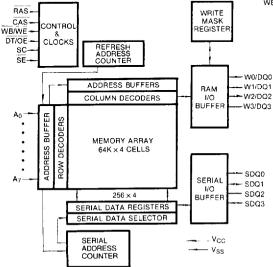

#### FUNCTIONAL BLOCK DIAGRAM

#### GENERAL DESCRIPTION

The Samsung KM424C64 is a CMOS 64K × 4 bit Dual Port DRAM. It consists of a 64K x 4 dynamic random access memory (RAM) port and 256 x 4 static serial access memory (SAM) port. The RAM and SAM ports operate asynchronously except during data transfer between the ports.

The RAM array consists of 256 rows of 1024 bits. It operates like a conventional 64K x 4 CMOS DRAM. The RAM port has a write per bit mask capability.

The SAM port consists of four 256 bit high speed shift registers that are connected to the RAM array through a 1024 bit data transfer gate. The SAM port has serial read and write capabilities.

Data may be internally transferred bi-directionally between the RAM and SAM ports using read or write transfers.

Refresh is accomplished by familiar DRAM refresh modes. The KM424C64 supports RAS only, Hidden, and CAS-before-RAS refresh for the RAM port. The SAM port does not require refresh.

All inputs and I/O's are TTL level compatible. All address lines and Data inputs are latched on chip to simplify system design. The outputs are unlatched to allow greater system flexibility.

### PIN CONFIGURATION (Top Views)

| Pin Name      | Pin Function                 |

|---------------|------------------------------|

| sc            | Serial Clock                 |

| SDQo -SDQ3    | Serial Data Input/Output     |

| DT/OE         | Data Transfer/Output Enable  |

| WB/WE         | Write Per Bit/Write Enable   |

| RAS           | Row Address Strobe           |

| CAS           | Column Address Strobe        |

| Wo/DQo-W3/DQ3 | Data Write Mask/Input/Output |

| SE            | Serial Enable                |

| Ao-A8         | Address Inputs               |

| Vcc           | Power(+5V)                   |

| Vss           | Ground                       |

### **CMOS VIDEO RAM**

### ABSOLUTE MAXIMUM RATINGS\*

| Item                                                          | Symbol           | Rating        | Unit |

|---------------------------------------------------------------|------------------|---------------|------|

| Voltage on Any Pin Relative to Vss                            | Vin, Vout        | -1 to +7.0    | ٧    |

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> | V <sub>cc</sub>  | -1 to +7.0    | ٧    |

| Storage Temperature                                           | T <sub>stg</sub> | - 55 to + 150 | °C   |

| Power Dissipation                                             | PD               | 1             | W    |

| Short Circuit Output Current                                  | los              | 50            | mA   |

<sup>\*</sup>Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS (Voltage referenced to V<sub>ss</sub>, T<sub>A</sub> = 0 to 70°C)

| Item               | Symbol          | Min   | Тур | Max | Unit |

|--------------------|-----------------|-------|-----|-----|------|

| Supply Voltage     | V <sub>cc</sub> | 4.5   | 5.0 | 5.5 | V    |

| Ground             | V <sub>SS</sub> | 0     | 0   | 0   | ٧    |

| Input High Voltage | V <sub>IH</sub> | 2.4   | _   | 6.5 | ٧    |

| Input Low Voltage  | V <sub>1L</sub> | - 1.0 | _   | 0.8 | ν    |

### DC AND OPERATING CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter(RAM Port)                                                  |                                              | CAM David                                 | Cumhal             | KM42               | 4C64 |      |      |

|----------------------------------------------------------------------|----------------------------------------------|-------------------------------------------|--------------------|--------------------|------|------|------|

|                                                                      | Parameter(HA                                 | M PORO                                    | SAM Port           | Symbol             | - 10 | - 12 | Unit |

| Operating                                                            | Current*                                     |                                           | Standby            | I <sub>CC1</sub>   | 65   | 55   | mA   |

| (RAS and                                                             | CAS Cycling @ t <sub>RC</sub> =              | min)                                      | Active             | I <sub>CC1</sub> A | 100  | 85   | mA   |

| Standby                                                              | RAS, CAS, DT/OF                              | SE = VIH, SC = VIL                        | Standby            | I <sub>CC2</sub>   | 3    | 3    | mA   |

| Current                                                              | WB/WE = V <sub>IH</sub>                      | $\overline{SE} = V_{IL}$ , $SC = Cycling$ | Active             | I <sub>CC2</sub> A | 40   | 35   | mA   |

| RAS Only                                                             | Refresh Current*                             |                                           | Standby            | 1 <sub>CC3</sub>   | 65   | 55   | mA   |

|                                                                      | , RAS Cycling @ t <sub>RC</sub>              | = min)                                    | Active             | I <sub>CC3</sub> A | 100  | 85   | mA   |

| Fast Page                                                            | Mode Current*                                |                                           | Standby            | I <sub>CC4</sub>   | 50   | 40   | mA   |

|                                                                      | , <del>CAS</del> Cycling @ t <sub>PC</sub> : | = min)                                    | Active             | I <sub>CC4</sub> A | 85   | 70   | mA   |

| CAS-Before                                                           | re-RAS Refresh Curre                         | nt*                                       | Standby            | I <sub>CC5</sub>   | 65   | 55   | mA   |

| (RAS and CAS Cycling @ t <sub>RC</sub> = min)                        |                                              | Active                                    | I <sub>CC5</sub> A | 100                | 85   | mA   |      |

| Data Transfer Current* (RAS and CAS Cycling @ t <sub>RC</sub> = min) |                                              | Standby                                   | I <sub>CC6</sub>   | 75                 | 65   | mA   |      |

|                                                                      |                                              | Active                                    | I <sub>CC6</sub> A | 110                | 95   | mA   |      |

<sup>\*</sup>NOTE: Icc1/A, Icc3/A, Icc3/A, Iccs/A, and Iccs/A are dependent on output loading and cycle rates. Specified values are obtained with the output open. Icc is specified as an average current.

### INPUT/OUTPUT CURRENTS (Recommended operating conditions unless otherwise noted.)

| Item                                                                                              | Symbol          | Min         | Max | Unit |

|---------------------------------------------------------------------------------------------------|-----------------|-------------|-----|------|

| Input Leakage Current (Any input 0≤V <sub>IN</sub> ≤6.5V, all other pins not under test=0 volts.) | I <sub>IL</sub> | <b>–</b> 10 | 10  | μΑ   |

| Output Leakage Current (Data out is disabled, 0V≤VOUT≤5.5V)                                       | loL             | - 10        | 10  | μΑ   |

| Output High Voltage Level<br>(RAM I <sub>OH</sub> = -5mA, SAM I <sub>OH</sub> = -2mA)             | V <sub>OH</sub> | .2.4        |     | ٧    |

| Output Low Voltage level (RAM $I_{OL} = 4.2$ mA, SAM $I_{OL} = 2$ mA)                             | V <sub>OL</sub> | _           | 0.4 | V    |

### CAPACITANCE (T<sub>A</sub> = 25°C)

| Item                                                | Symbol           | Min | Max | Unit |  |

|-----------------------------------------------------|------------------|-----|-----|------|--|

| Input Capacitance (A <sub>0</sub> -A <sub>7</sub> ) | C <sub>iN1</sub> |     | 6   | ρF   |  |

| Input Capacitance (RAS, CAS, WB/WE, DT/OE, SE, SC)  | C <sub>IN2</sub> |     | 7   | pF   |  |

| Input/Output Capacitance (Wo/DQo-W3/DQ3)            | Coo              |     | 7   | pF   |  |

| Input/Output Capacitance (SDQo -SDQ3)               | C <sub>SDQ</sub> |     | 7   | pF   |  |

# AC CHARACTERISTICS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C, V<sub>CC</sub>=5.0V $\pm$ 10%. See notes 1, 2)

|                                            |                   | -1  | o        | -1  | 12      | Unit | Notes        |

|--------------------------------------------|-------------------|-----|----------|-----|---------|------|--------------|

| Parameter                                  | Symbol            | Min | Max      | Min | Max     | Unit |              |

| Random read or write cycle time            | t <sub>RC</sub>   | 180 |          | 220 |         | ns   |              |

| Read-modify-write cycle time               | t <sub>RWC</sub>  | 245 |          | 295 |         | ns   |              |

| Fast page mode cycle time                  | t <sub>PC</sub>   | 60  |          | 75  |         | ns   |              |

| Fast page mode read-modify-write           | t <sub>PRWC</sub> | 125 |          | 145 |         | ns   |              |

| Access time from RAS                       | t <sub>RAC</sub>  |     | 100      |     | 120     | ns   | 3,4          |

| Access time from CAS                       | tcac              |     | 25       |     | 30      | ns   | 4            |

| Access time from column address            | t <sub>AA</sub>   |     | 50       |     | 60      | ns   | 3,11         |

| Access time from CAS precharge             | topa              |     | 55       |     | 65      | ns   | 3            |

| CAS to output in Low-Z                     | t <sub>CLZ</sub>  | 5   |          | 5   |         | ns   | 3            |

| Output buffer turn-off delay               | t <sub>OFF</sub>  | 0   | 30       | 0   | 35      | ns   | 7            |

| Transition time (rise and fall)            | tτ                | 3   | 50       | 3   | 50      | ns   | 2            |

| RAS precharge time                         | t <sub>RP</sub>   | 70  |          | 90  | ļ       | ns   |              |

| RAS pulse width                            | tras              | 100 | 10,000   | 120 | 10,000  | ns   |              |

| RAS pulse width (Fast page mode)           | tRASP             | 100 | 100,000  | 120 | 100,000 | ns   |              |

| RAS hold time                              | t <sub>RSH</sub>  | 25  |          | 30  |         | ns   | ļ            |

| CAS hold time                              | t <sub>CSH</sub>  | 100 |          | 120 |         | ns   |              |

| CAS pulse width                            | t <sub>CAS</sub>  | 25  |          | 30  |         | ns   |              |

| RAS to CAS delay time                      | t <sub>RCD</sub>  | 25  | 75       | 25  | 90      | ns   | 5,6          |

| RAS to column address delay time           | t <sub>RAD</sub>  | 20  | 50       | 20  | 60      | ns   | 11_          |

| CAS to RAS precharge time                  | t <sub>CRP</sub>  | 10  |          | 10  |         | ns   | <u> </u>     |

| CAS precharge time                         | t <sub>CPN</sub>  | 15  |          | 20  |         | ns   | <u> </u>     |

| CAS precharge time (Fast page)             | top               | 15  |          | 20  |         | ns   |              |

| Row address set-up time                    | t <sub>ASR</sub>  | 0   |          | 0   |         | ns   | +-           |

| Row address hold time                      | t <sub>RAH</sub>  | 15  |          | 15  |         | ns   | <del> </del> |

| Column address set-up time                 | t <sub>ASC</sub>  | 0   | <u> </u> | 0_  |         | ns   | <u> </u>     |

| Column address hold time                   | t <sub>CAH</sub>  | 20  |          | 25  |         | ns   | <del></del>  |

| Column address hold time referenced to RAS | t <sub>AR</sub>   | 75  |          | 85  |         | ns   |              |

| Column address to RAS lead time            | t <sub>RAL</sub>  | 50  |          | 60  |         | ns   |              |

| Read command set-up time                   | t <sub>RCS</sub>  | 0   |          | 0   |         | ns   | <del>_</del> |

| Read command hold referenced to CAS        | t <sub>RCH</sub>  | 0   |          | 0   |         | ns   | 9            |

| Read command hold referenced to RAS        | t <sub>RRH</sub>  | 10  |          | 10  |         | ns   | 9            |

| Write command hold time                    | twon              | 20  |          | 25  |         | ns   | 1            |

### STANDARD OPERATION (Continued)

| Parameter                                                   | Sumb = 1         |     | 10          | _   | 12  |      | Notes |

|-------------------------------------------------------------|------------------|-----|-------------|-----|-----|------|-------|

| r arameter                                                  | Symbol           | Min | Max         | Min | Max | Unit |       |

| Write command hold time referenced to RAS                   | t <sub>wcn</sub> | 75  |             | 85  |     | ns   |       |

| Write command pulse width                                   | t <sub>we</sub>  | 20  | <u> </u>    | 25  |     | ns   |       |

| Write command to RAS lead time                              | t <sub>RWL</sub> | 25  |             | 30  |     | ns   |       |

| Write command to CAS lead time                              | t <sub>cwL</sub> | 25  |             | 30  |     | ns   |       |

| Data set-up time                                            | t <sub>DS</sub>  | 0   |             | 0   | ·   | ns   | 10    |

| Data hold time                                              | t <sub>DH</sub>  | ·20 |             | 25  |     | ns   | 10    |

| Data hold referenced to RAS                                 | tohe             | 75  |             | 85  |     | ns   |       |

| Write command set-up time                                   | t <sub>wcs</sub> | 0   | İ           | 0   |     | ns   | 8     |

| CAS to WE delay                                             | t <sub>CWD</sub> | 60  |             | 70  |     | ns   | 8     |

| RAS to WE delay                                             | t <sub>RWD</sub> | 135 |             | 160 |     | ns   | 8     |

| Column address to WE delay time                             | t <sub>AWD</sub> | 85  |             | 100 |     | ns   | 8     |

| CAS set-up time (C-B-R refresh)                             | t <sub>CSR</sub> | 10  |             | 10  |     | ns   |       |

| CAS hold time (C-B-R refresh)                               | t <sub>CHR</sub> | 20  |             | 25  |     | ns   |       |

| RAS precharge to CAS hold time                              | t <sub>RPC</sub> | 10  |             | 10  |     | ns   |       |

| RAS hold time referenced to OE                              | t <sub>ROH</sub> | 20  |             | 20  |     | ns   |       |

| Access time from output enable                              | toea             | -   | 25          |     | 30  | ns   |       |

| Output enable to data input delay                           | t <sub>OED</sub> | 20  |             | 25  |     | ns   |       |

| Output buffer turnoff delay from OE                         | t <sub>OEZ</sub> | 0   | 25          | 0   | 30  | ns   | 7 —   |

| Output enable command hold time                             | toen             | 25  |             | 30  |     | ns   |       |

| Data to CAS delay                                           | tozc             | 0   |             | 0   |     | ns + |       |

| Data to output enable delay                                 | t <sub>DZO</sub> | 0   | _·          | 0   | -   | ns   |       |

| Refresh period (256 cycles)                                 | t <sub>REF</sub> |     | 4           |     | 4   | ms   |       |

| WB Set-up time                                              | twsa             | 0   |             | 0   |     | ns   |       |

| WB hold time                                                | t <sub>RWH</sub> | 15  |             | 20  |     | ns   |       |

| Write per bit mask data set-up                              | t <sub>MS</sub>  | 0   |             | 0   |     | ns   |       |

| Write per bit mask data hold                                | t <sub>MH</sub>  | 15  |             | 20  |     | ns + |       |

| DT high set-up time                                         | t <sub>THS</sub> | 0   |             | 0   |     | пѕ   |       |

| DT high hold time                                           | t <sub>THH</sub> | 15  |             | 20  |     | ns   |       |

| DT low set-up time                                          | t <sub>TLS</sub> | 0   |             | 0   |     | ns   |       |

| DT low hold time                                            | t <sub>TLH</sub> | 15  | <del></del> | 20  |     | ns   |       |

| DT low hold ref to column address (real time read transfer) | t <sub>ATH</sub> | 35  | -           | 40  | - + | ns   | -     |

### **CMOS VIDEO RAM**

#### **STANDARD OPERATION** (Continued)

| <b>D</b>                                                          | Cumbal           | -1  | 0    | -1  | 2      | Unit | Notes |

|-------------------------------------------------------------------|------------------|-----|------|-----|--------|------|-------|

| Parameter                                                         | Symbol           | Min | Max  | Min | Max    | Onn  | Motes |

| DT low hold ref to RAS<br>(real time read transfer)               | t <sub>RTH</sub> | 80  |      | 95  |        | ns   |       |

| DT low hold ref to CAS (real time read transfer)                  | tстн             | 30  | <br> | 35  |        | ns   |       |

| SE set-up referenced to RAS                                       | tesa             | 0   |      | 0   |        | ns   |       |

| SE hold time referenced to RAS                                    | treh             | 15  |      | 20  |        | ns   |       |

| DT to RAS precharge delay                                         | t <sub>TRD</sub> | 10  |      | 10  |        | ns   | <br>  |

| DT to CAS precharge delay time                                    | trop             | 10  |      | 10  |        | ns   |       |

| DT precharge time                                                 | t <sub>TP</sub>  | 30  |      | 35  |        | ns   |       |

| RAS to first SC delay (read transfer)                             | trsd             | 100 |      | 120 |        | ns   |       |

| CAS to first SC delay (read transfer)                             | tcsp             | 50  |      | 60  |        | ns   |       |

| Last SC to DT lead time                                           | t <sub>TSL</sub> | 0   |      | 0   |        | ns   |       |

| DT to first SC delay (read transfer)                              | t <sub>TSD</sub> | 20  |      | 20  |        | ns   |       |

| Last SC to RAS set-up (serial input)                              | tsas             | 30  | İ    | 40  |        | ns   |       |

| RAS to first SC delay time (serial input)                         | tsrd             | 25  | Ī    | 25  |        | ns   |       |

| RAS to serial input delay                                         | t <sub>SDD</sub> | 50  |      | 60  |        | ns   |       |

| Serial out buffer turn-off delay from RAS (pseudo write transfer) | t <sub>SDZ</sub> | 10  | 50   | 10  | 60     | ns   | 7     |

| Serial input to first SC delay                                    | tszs             | 0   |      | 0   |        | ns   |       |

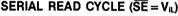

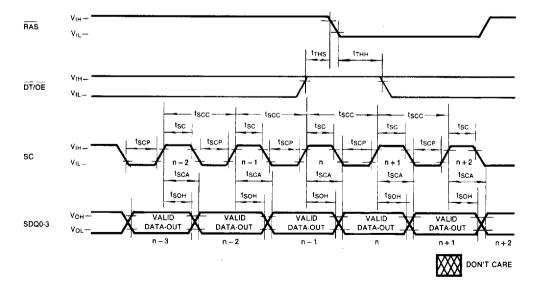

| SC cycle time                                                     | tscc.            | 30  |      | 40  | l<br>L | ns   |       |

| SC pulse width (SC high time)                                     | tsc              | 10  |      | 15  |        | ns   |       |

| SC precharge (SC low time)                                        | tsce             | 10  |      | 15  |        | ns   |       |

| Access time from SC                                               | tsca             |     | 25   |     | 35     | ns   | 4     |

| Serial output hold time from SC                                   | tsон             | 5   |      | 5   |        | ns   | !<br> |

| Serial input set-up time                                          | tsps             | 0   |      | 0   |        | ns   |       |

| Serial input hold time                                            | tsph             | 20  |      | 30  |        | ns   |       |

| Access time from SE                                               | tsea             |     | 25   |     | 35     | ns   | 4     |

| SE pulse width                                                    | t <sub>SE</sub>  | 25  |      | 35  |        | ns   |       |

| SE precharge time                                                 | tsep             |     |      | 35  |        | ns   |       |

| Serial out buffer turn-off from SE                                | tsez             | 0   | 20   | 0   | 30     | ns   | 7     |

| Serial input to SE delay time                                     | tsze             | 0   |      | 0   |        | ns   |       |

| Serial write enable set-up                                        | tsws             | 5   |      | 10  |        | ns   |       |

| Serial write enable hold time                                     | tswн             | 15  |      | 20  |        | ns   |       |

#### NOTES

- V<sub>IH</sub>(min) and V<sub>IL</sub>(max) are reference levels for measuring timing of input signals. Transition times are measured between V<sub>IH</sub>(min) and V<sub>IL</sub>(max) and are assumed to be 5ns for all inputs.

- 3. RAM port outputs are measured with a load equivalent to 2 TTL loads and 100pF.

- SAM port outputs are measured with a load equivalent to 2 TTL loads and 50pF. D<sub>OUT</sub> comparator level: V<sub>OH</sub>/V<sub>OL</sub> = 2.0/0.8V.

- Operation within the t<sub>RCD</sub>(max) limit insures that t<sub>RCD</sub>(max) can be met. t<sub>RCD</sub>(max) is specified as a reference point only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- Assumes that t<sub>RCD</sub>≥t<sub>RCD</sub>(max).

- The parameters, t<sub>OFF</sub>(max), t<sub>OEZ</sub>(max), t<sub>SDZ</sub>(max) and t<sub>SEZ</sub>(max), define the time at which the output achieves the open circuit condition and is not referenced to V<sub>OH</sub> or V<sub>OL</sub>.

- 8. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are non restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If t<sub>WCS</sub>≥t<sub>WCS</sub>(min) the cycle is an early write cycle and the data out pin will remain high impedance for the duration of the cycle. If t<sub>CWD</sub>≥t<sub>CWD</sub>(min) and t<sub>RWD</sub><t<sub>RWD</sub>(min) and t<sub>AWD</sub>≥t<sub>AWD</sub>(min), then the cycle is a read-write cycle and the data out will contain the data read from the selected address. If neither of the above conditions are satisfied, the condition of the data out is indeterminate.

- 9. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- These parameters are referenced to the CAS leading edge in early write cycles and to the WE leading edge in read-write cycles.

- 11. Operation within the t<sub>RAD</sub>(max) limit insures that t<sub>RCD</sub>(max) can be met. t<sub>RAD</sub>(max) is specified as a reference point only. If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max) limit, then access time is controlled by t<sub>AA</sub>.

#### **DEVICE INFORMATION**

All operation modes of KM424C64 are determined by CAS, DT/OE, WB/WE and SE at the falling edge of RAS. The truth table of the operation modes is shown in table 1.

Table 1. Operation truth table

| RAS           | CAS | ADDRESS    | DT/OE | WB/WE | SE | FUNCTION               |

|---------------|-----|------------|-------|-------|----|------------------------|

| Н             | Н   | *          | *     | *     | *  | Standby                |

|               | L   | *          | *     | *     | *  | CAS-before-RAS Refresh |

|               | Н   | row/column | H→L   | н     | *  | READ                   |

| $\overline{}$ | н   | row/column | н     | H→L   | *  | WRITE                  |

| \ <u> </u>    | Н   | row        | Н     |       | *  | RAS-only Refresh       |

|               | н   | row/column | Н     | L     | *  | WRITE-per-Bit          |

|               | Н   | row/tap    | L     | H     | *  | READ Transfer          |

|               | н   | row/tap    | L     | L     | L  | WRITE Transfer         |

|               | Н   | row/tap    | L     | L     | н  | Pseudo-Write Transfer  |

#### **Device Operation**

The KM424C64 contains 262,144 memory locations, sixteen address bits are required to address a particular 4-bit word in the memory array. Since the KM424C64 has only 8 address input pins, time multiplexed addressing is used to input 8 row and 8 column addresses. The multiplexing is controlled by the timing relationship between the row address strobe (RAS), the column address strobe (CAS) and the valid row and column address inputs.

Operation of the KM424C64 begins by strobing in a valid row address with RAS while CAS remains high. Then the address on the 8 address input pins is changed from a row address to a column address and is strobed in by CAS. This is the beginning of any KM424C64 cycle in which a memory location is accessed. The specific type of cycle is determined by the state of the write enable pin and various timing relationships. The cycle is terminated when both RAS and CAS have returned to the high state. Another cycle can be initiated after RAS remains high long enough to satisfy the RAS precharge time (t<sub>RP</sub>) requirement.

#### RAS and CAS Timing

The minimum RAS and CAS pulse widths are specified by t<sub>BAS</sub>(min) and t<sub>CAS</sub>(min) respectively. These minimum pulse widths must be satisfied for proper device operation and data integrity. Once a cycle is initiated by bringing RAS low, it must not be aborted prior to satisfying the minimum RAS and CAS pulse widths. In addition, a new cycle must not begin until the minimum RAS precharge time, tap, has been satisfied. Once a cycle begins, internal clocks and other circuits within the KM424C64 begin a complex sequence of events. If the sequence is broken by violating minimum timing requirements, loss of data integrity can occur.

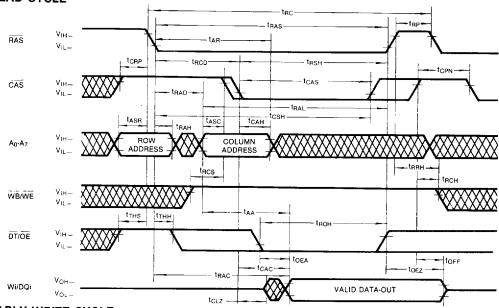

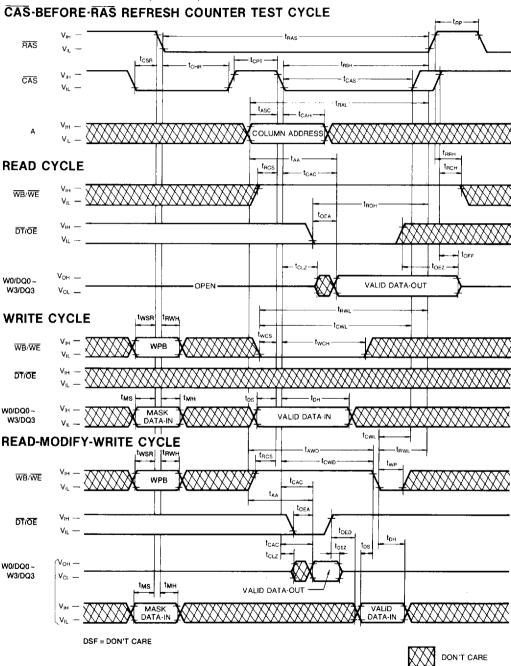

#### Read

A read cycle is achieved by maintaining WB/WE high during a RAS/CAS cycle. The access time is normally specified with respect to the falling edge of RAS. But the access time also depends on the falling edge of CAS and on the valid column address transition. If CAS goes low before t<sub>RCD</sub>(max) and if the column address is valid before t<sub>RAD</sub>(max) then the access time to valid data is specified by trac(min). However, if CAS goes low after t<sub>BCD</sub>(max) or if the column address becomes valid after t<sub>RAD</sub>(max), access is specified by t<sub>CAC</sub> or t<sub>AA</sub>.

The KM424C64 has common data I/O pins. The DT/OE has been provided so the output buffer can be precisely controlled. For data to appear at the outputs, DT/OE must be low for the period of time defined by toea.

#### Write

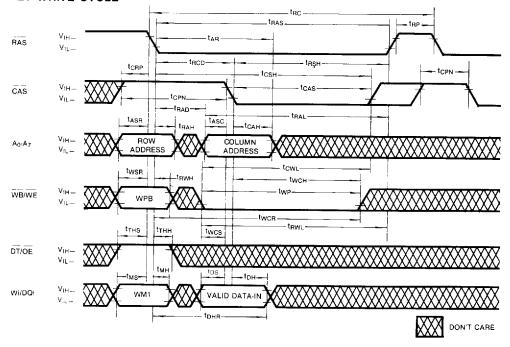

The KM424C64 can perform early write and read-modifywrite cycles. The differece between these cycles is in the state of data-out and is determined by the timing relationship between WB/WE, DT/OE and CAS. In any type of write cycle Data-in must be valid at or before the falling edge of WB/WE whichever is later.

Early Write: An early write cycle is performed by bringing WB/WE low before CAS. The 4-bit wide data at the data input pins is written into the addressed memory cells. Throughout the early write cycle the outputs remain in the Hi-Z state. In the early write cycle DT/OE must meet DT/OE high set-up and hold time as RAS falls but otherwise does not affect any circuit operation during the CAS active period.

Read-Modify-Write: In this cycle, valid data from the addressed cells appears at the outputs before and during the time that data is being written into the same cell locations. In this cycle read operation is achieved by bringing DT/OE low with RAS and CAS low. The access time to valid data is specified by toFA. After DT/OE goes high, the data to be written is stored by WB/WE with set-up and hold times referenced to this signal.

Late Write: This cycle shows the timing flexibility of (DT/OE) which can be activated just after (WB/WE) falls, even when (WB/WE) is brought low after CAS.

#### Fast Page Mode

Fast page mode provides high speed read, write or readmodify-write access to all memory cells within a selected row. These cycles may be mixed in any order. A fast page mode cycle begins with a normal cycle. Then, while RAS is kept low to maintain the row address. CAS is cycled to strobe in additional column addresses. This eliminates the time required to set up and strobe sequential row addresses for the same page.

#### Write-Per-Bit

The write-per-bit function selectively controls the internal write-enable circuits of the RAM port. When WB/WE is held 'low' at the falling edge of RAS, during a random access operation, the write-mask is enabled. At the same time, the mask data on the Wi/DQi pins is latched onto the write-mask register (WM1). When a '0' is sensed on any of the Wi/DQi pins, their corresponding write circuits are disabled and new data will not be

When a '1' is sensed on any of the Wi/DQi pins, their corresponding write circuits will remain enabled so that new data is written. The write mask data is valid for only one cycle. The truth table of the write-per-bit function is shown in table 2.

Table 2. Truth Table for Write-per-Bit Function

| RAS | CAS | DT/ŌĒ | WB/WE | Wi/DQi | FUNCTION     |

|-----|-----|-------|-------|--------|--------------|

| -\  | Н   | Н     | Н     | *      | WRITE ENABLE |

| \   | Н   | Н     | i · L | 1      | WRITE ENABLE |

|     | İ   |       |       | 0      | WRITE MASK   |

#### **Data Output**

The KM424C64 has a three state output buffers which are controlled by  $\overline{CAS}$  and  $\overline{DT}/\overline{OE}$ . When either  $\overline{CAS}$  or  $\overline{DT}/\overline{OE}$  is high (V<sub>iH</sub>) the output is in the high impedance (Hi-Z) state. In any cycle in which valid data appears at the output the output goes into the low impedance state in a time specified by  $t_{CLZ}$  after the falling edge of  $\overline{CAS}$ . Invalid data may be presented at the output during the time after  $t_{CLZ}$  and before the valid data appears at the output. The timing parameters  $t_{CAC}$ ,  $t_{RAC}$  and  $t_{AA}$  specify when the valid data will be present at the output. The valid data remains at the output until  $\overline{CAS}$  returns high. This is true even if a new  $\overline{RAS}$  cycle occurs (as in hidden refresh). Each of the KM424C64 operating cycles is listed below after the corresponding output state produced by the cycle.

Valid Output Data: Read, Read-Modify-Write, Hidden Refresh, Fast Page Mode Read, Fast Page Mode Read-Modify-Write.

#### Refresh

The data in the KM424C64 is stored on a tiny capacitor within each memory cell. Due to leakage the data may leak off after a period of time. To maintain data integrity it is necessary to refresh each of the 256 rows every 4 ms. Any operation cycle performed in the RAM port refreshes the 1024 bits selected by the row addresses or an on-chip refresh address counter. Either a burst refresh or distributed refresh may be used. There are several ways to accomplish this.

$\overline{\it RAS}$ -Only Refresh: This is the most common method for performing refresh. It is performed by strobing in a row address with  $\overline{\it RAS}$  while  $\overline{\it CAS}$  remains high. This cycle must be repeated for each of the 256 row addresses,  $(A_0,A_7)$ .

CAS-before-RAS Refresh: The KM424C64 has CAS-before-RAS on-chip refresh capability that eliminates the need for external refresh addresses. If CAS is held low for the specified set up time (t<sub>CSR</sub>) before RAS goes low, the on-chip refresh circuitry is enabled. An inter-

nal refresh operation automatically occurs. The refresh address is supplied by the on-chip refresh address counter which is then internally incremented in preparation for the next CAS-before-RAS refresh cycle.

Hidden Refresh: A hidden refresh cycle may be performed while maintaining the latest valid data at the output by extending the CAS active time and cycling RAS. The KM424C64 hidden refresh cycle is actually a CAS-before-RAS refresh cycle within an extended read cycle. The refresh row address is provided by the on-chip refresh address counter.

Other Refresh Methods: It is also possible to refresh the KM424C64 by using read, write or read-modify-write cycles. Whenever a row is accessed, all the cells in that row are automatically refreshed. There are certain applications in which it might be advantageous to perform refresh in this manner but in general RAS-only or CAS-before-RAS refresh is the preferred method.

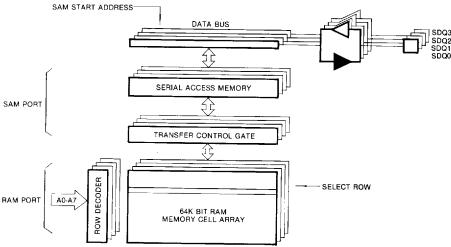

#### **Transfer Operation**

The KM424C64 features bi-directional transfer capability from RAM to SAM and from SAM to RAM. A transfer consists of loading 256 words by 4-bits of data from one port into the other. During a data transfer cycle, RAM port and SAM port can't operate independently. Data transfer cycle includes are following operations.

- i) Data is transferred between RAM memory cell on the specified row address and SAM data register (except pseudo write transfer).

- ii) Direction of data transfer is defined.

- iii) Serial read or serial write is selected.

- iv) SAM start address (the address to be accessed first after the termination of transfer cycle in the SAM data register) is specified.

There are three types of transfer operations: read transfer, write transfer and pseudo-write transfer. As shown in table 3, the type of transfer operation is determined by CAS, DT/OE, WB/WE and SE at the falling edge of RAS.

Table 3. Truth Table for Transfer Operation

| RAS | CAS | DT/OE | WB/WE | SE | FUNCTION                    | TRANSFER DIRECTION |

|-----|-----|-------|-------|----|-----------------------------|--------------------|

|     | Н   | L     | Н     | *  | Read transfer cycle         | RAM→SAM            |

| \   | H   | L     | L     | L  | Write transfer cycle        | SAM→RAM            |

|     | Н   | L     | L     | Н  | Pseudo write transfer cycle | ·                  |

### Read-Transfer Cycle

A read-transfer consists of loading a selected row of data from the RAM array into the SAM register. A readtransfer is accomplished by holding CAS high, DT/OE low and WB/WE high at the falling edge of RAS. The row address selected at the falling edge of RAS determines the RAM row to be transferred into the SAM. The actual data transfer is completed at the rising edge of DT/OE. When the transfer is completed, the SDQ lines

are set into the output mode. In a read/real-time readtransfer cycle, the transfer of a new row of data is completed at the rising edge of DT/OE and becomes valid on the SDQ lines after the specified access time t<sub>SCA</sub> from the rising edge of the subsequent serial clock(SC) cycle. The start address of the serial pointer of the SAM is determined by the column address selected at the falling edge of CAS.

Figure 2. BLOCK diagram of RAM and SAM PORT during read transfer

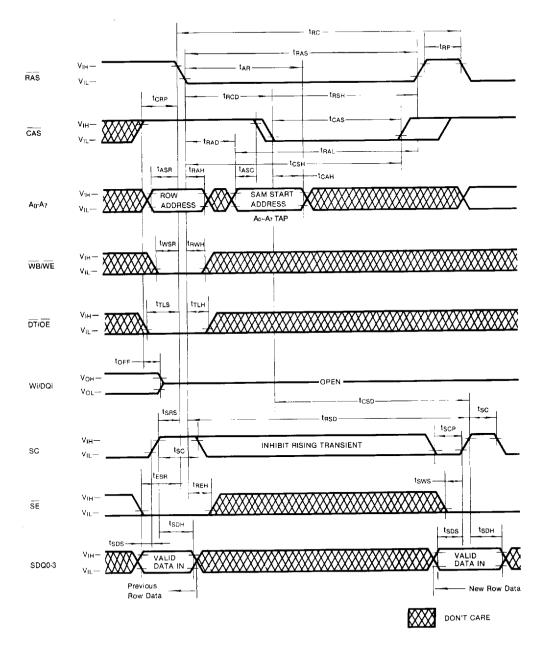

#### Write Transfer Cycle

A write transfer cycle consists of loading the content of the SAM data register into a selected row of RAM array. A write transfer is accomplished by CAS high, DT/OE low, WB/WE low and SE low at the falling edge of RAS. The row address selected at the falling edge of RAS determines the RAM row address into which the data will be transfered. The column address selected at the falling edge of CAS determines the start address of the serial pointer of the SAM. After the write transfer is completed, the SDQ lines are in the input mode so that serial data synchronized with SC can be loaded. When two consecutive write transfer operations are performed, there is a delay in availability between the last bit of the previous row and the first bit of the new row. Consequently the SC clock must be held at a constant VIL or VIH after the SC precharge time tsce has been satisfied. A rising edge of the SC clock must not occur until after a specified delay  $t_{\mbox{\scriptsize RSD}}$  from the falling edge of RAS.

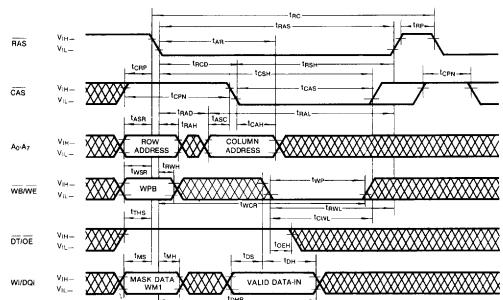

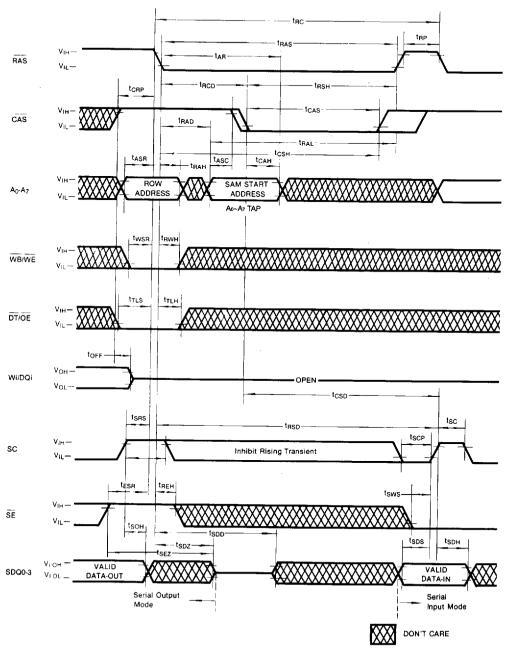

#### Pseudo Write Transfer Cycle

The pseudo write transfer cycle switches SDQ lines from serial read mode to serial write mode. It doesn't perform data transfer. A pseudo write transfer is accomplished by holding CAS high, DT/OE low, WB/WE low and SE high at the falling edge of RAS. The pseudo write transfer cycle must be performed after a read transfer cycle if the subsequent operation is a write transfer cycle. There is a timing delay associated with the switching of the SDQ lines from serial output mode to serial input mode. During this period, the SC clock must be held at a constant  $V_{IL}$  or  $V_{IH}$  after the  $t_{SC}$ precharge time has been satisfied. A rising edge of the SC clock must not occur until after the specified delay t<sub>RSD</sub> from the falling edge of RAS.

#### SAM Port Operation

The KM424C64 is provided with a 256 word by 4 bit serial access memory (SAM). High speed read and write operation may be performed through the SAM port independent of the RAM port operations, except during transfer operation. The preceding transfer operation determines the direction of data flow through the SAM registers. Data may be read out of the SAM port after a read transfer cycle (RAM→SAM) has been performed. Data can be shifted out of the SAM port starting at any of the 256 bit locations. This tap location corresponds to the column address selected at the falling edge of CAS

### **CMOS VIDEO RAM**

during the read transfer cycle. The SAM register is configured as a circular data register. The data is shifted sequentially starting from the selected tap location to

the most significant bit and then wraps around to the least significant bit.

> Tap location started by column address of read-transfer cycle.

Subsequent real time read transfer may be performed on the fly as many times as desired within the refresh constraint of the RAM memory array. A pseudo write transfer cycle must be performed in order to write data into the SAM port. This cycle switches the SAM port operation from output mode to input mode. Data is not transferred during a pseudo write transfer cycle. A write transfer cycle (SAM→RAM) may then be performed. The data in the SAM register is loaded into the RAM row selected by the row address at the falling edge of RAS. The start address of SAM registers is determined by the column address selected at the falling edge of CAS.

Table 4. Truth Table for SAM Operation

| Preceding<br>Transfer<br>Cycle | SAM port operation      | DT/OE (at the falling edge of RAS) | sc | SE | Function            |

|--------------------------------|-------------------------|------------------------------------|----|----|---------------------|

| read-                          | serial                  |                                    |    | L  | Serial read enable  |

| transfer                       | output<br>mode          |                                    |    | Н  | Serial read disable |

| write-<br>transfer             | serial<br>input<br>mode | L*                                 | Л  | L  | Serial write enable |

\*When simultaneous operation is being performed on the RAM port and the SAM port, DT/OE must be held high at the falling edge of RAS so as to prevent a false transfer cycle.

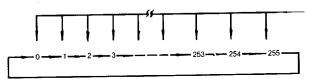

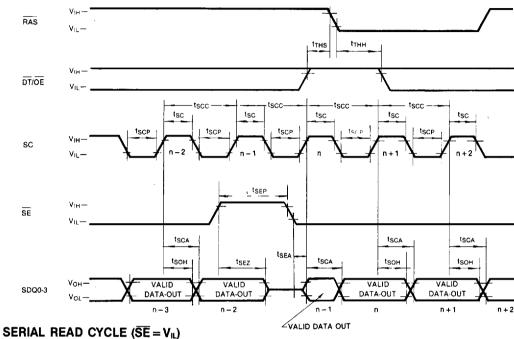

#### Serial Clock (SC)

All operations of the SAM port are synchronized with the serial clock SC. Data is shifted in or out of the SAM registers at the rising edge of SC. In a serial read, the output data becomes valid on the SDQ pins after the maximum specified serial access time t<sub>SCA</sub> from the rising edge of SC. The serial clock SC also increments the 8 bit serial pointer which is used to select the SAM address. The pointer address is incremented in a wrap around mode to select sequential locations after the starting location which is determined by the column address in the read transfer cycle. When the pointer reaches the most significant address location (decimal 255), the next SC clock will be placed at the least significant address location (decimal 0).

#### Serial Enable (SE)

The  $\widetilde{SE}$  input is used to enable serial access operation. In a serial read cycle, SE is used as an output control.

When SE is high, serial access is disabled, however, the serial address pointer location is still incremented when SC is clocked even when SE is high.

### Serial Input/Output (SDQ0-SDQ3)

Serial input and serial output share common I/O pins. Serial input or output mode is determined by the most recent transfer cycle. When a read transfer cycle is performed, the SAM port is in the output mode. When a pseudo write is performed, the SAM port operation is switched from output mode to input mode. During subsequent write transfer cycle, the SAM port remains in the input mode.

#### Power-up

If  $RAS = V_{IL}$  during power-up, the KM424C64 could possibly begin an active cycle. This condition results in higher than necessary current demands from the power supply during power-up. It is recommended that  $\overline{RAS}$  and  $\overline{CAS}$  track with  $V_{\infty}$  during power-up or be held at a valid  $V_{\mbox{\tiny IH}}$  in order to minimize the power-up current.

An initial pause of 200 µsec is required after power-up followed by 8 initialization cycles before proper device operation is assured.

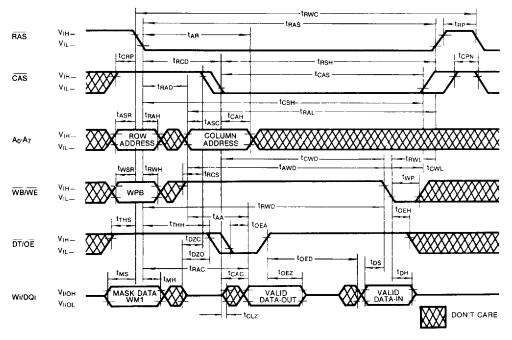

### TIMING DIAGRAMS **READ CYCLE**

### **EARLY WRITE CYCLE**

### TIMING DIAGRAMS (Continued) WRITE CYCLE (OE CONTROLLED WRITE)

### READ-WRITE/READ-MODIFY-WRITE CYCLE

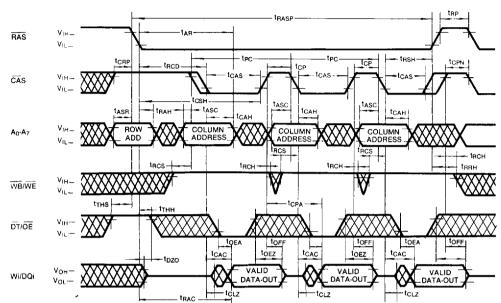

### TIMING DIAGRAMS (Continued) **FAST PAGE MODE READ CYCLE**

#### **FAST PAGE MODE WRITE CYCLE**

### TIMING DIAGRAMS (Continued) FAST PAGE MODE READ-MODIFY-WRITE CYCLE

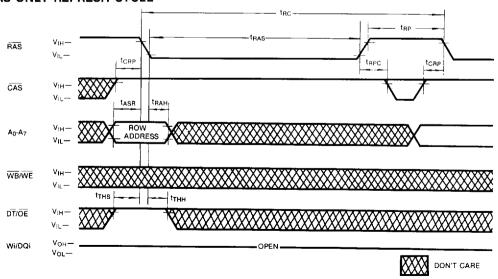

#### RAS ONLY REFRESH CYCLE

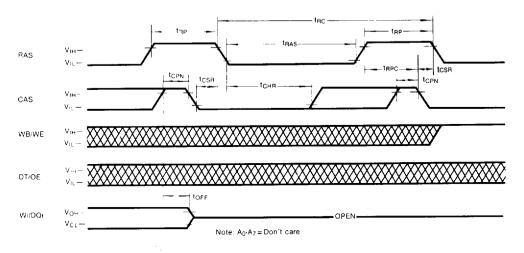

### TIMING DIAGRAMS (Continued) CAS-BEFORE-RAS REFRESH CYCLE

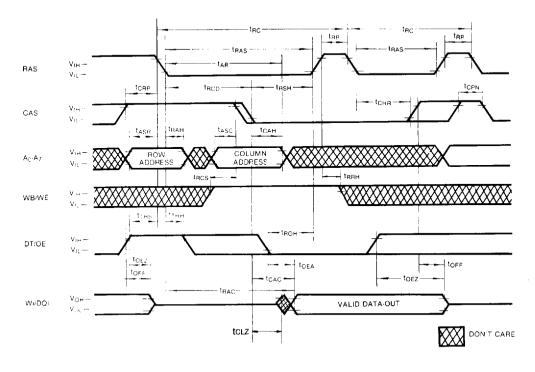

#### HIDDEN REFRESH CYCLE

### **CMOS VIDEO RAM**

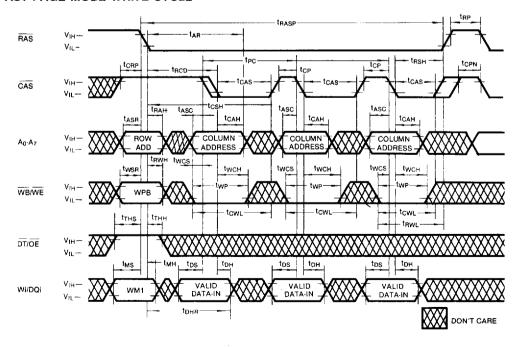

### TIMING DIAGRAMS (Continued)

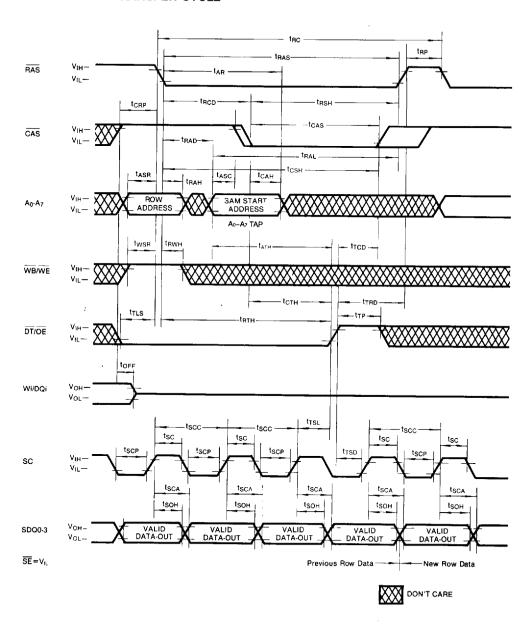

### TIMING DIAGRAMS (Continued) **READ TRANSFER CYCLE**

- \*1. When the previous data transfer cycle is a write or pseudo transfer cycle, it is defined as Read Transfer Cycle (1)

- \*2. When the previous data transfer cycle is a read transfer cycle, it is defined as Read Transfer Cycle (2).

### TIMING DIAGRAMS (Continued) **REAL TIME READ TRANSFER CYCLE**

### TIMING DIAGRAMS (Continued) WRITE TRANSFER CYCLE

### **CMOS VIDEO RAM**

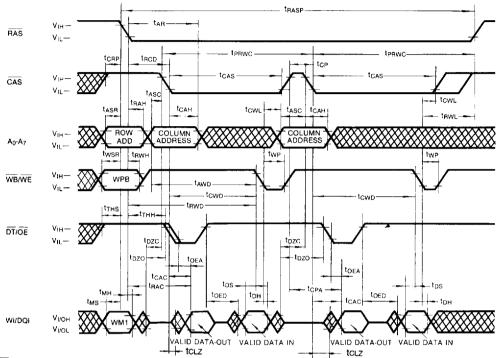

### TIMING DIAGRAMS (Continued) **PSEUDO WRITE TRANSFER CYCLE**

### TIMING DIAGRAMS (Continued) SERIAL READ CYCLE (SE CONTROLLED OUTPUTS)

### **CMOS VIDEO RAM**

TIMING DIAGRAMS (Continued)

SERIAL WRITE CYCLE (SE = Va)

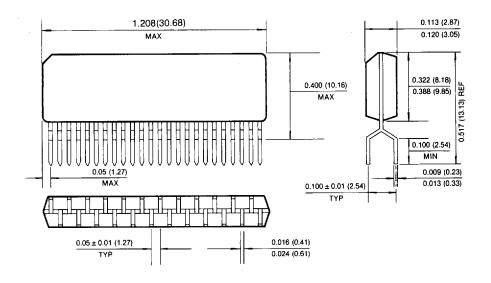

### PACKAGE DIMENSIONS 24-PIN PLASTIC DIP

Units: Inches (millimeters)

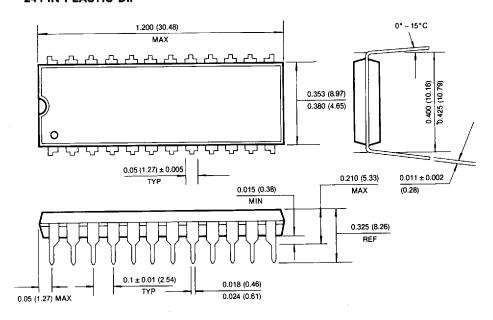

#### 24-PIN PLASTIC ZIP